Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

° (61) Дополнительное к авт. свид-ву (22) Заявлено 31.01.78 (21) 2573391/18-21 (51) М. Кл. . Н 03 К 13/02 с присоединением заявки ¹вЂ” (23) Приоритет

Государствен н ы и к Фиррт

СССР но долам изооретеннй н открытий

Опубликовано 230780. Бюллетень ¹ 27

Дата опубликования описания 230780 (53) УДК 681,325 (088. 8) (72) Авторы изобретения

A. П. Стахов, A. Д. Азаров, M. Е. Бородянский и В . A. Лужецкий (71) Заявитель

Винницкий политехнический институт (54) АНАЛОГО-ЦИФРОВОЙ ПЕРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области вычислительной и измерительной техники и может быть использовано для преобразования аналоговых величин в цифровые.

Известен аналого — цифровой преобразователь, содержащий усилитель, многопороговый блок сравнения, преобразователь параллельного коца, 1() цифро-аналоговый преобразователь, блок управления, входной блок и выходной блок (1).

Такие аналого-цифровые преобразователи не позволяют получить точное значение результата преобразования при воздействии помех.

Иэ известных устройств, наиболее близким по технической сущности является аналого-цифровой преобразо.ватель, содержащий (К вЂ” 1) усилите° лей, (K-1) цифро-аналоговых преобра" эователей, многопороговый блок сравнения, первый выход которого соединен с входом преобразователя парал — 25 лельного кода, выход 1 — того цифроаналогового преобразователя соединен со вторым входом i — того усилителя, первый вход которого соединен с выходом (i — 1) .— го усилителя, первый, вход первого усилителя подключен к входной клемме аналого-цифрового преобразователя и блок управле- ния (2), Недостатком такого аналого-цифрового преобразователя является значительное отличие конечного результата преобразования от истинного при воздействии импульсных помех в аналоговой части и сбоев в дискретной части.

Цель изобретения - повышения информационной надежности.

Это достигается тем, что аналогоцифровой преобразователь содержит (К-1) усилителей, (К-1),цифроаналЬговый преобраэователей, МНогопороговый блок сравнения, первый выход которого соединен со входом преобразователя кода, выход 1-того цифроаналогового преобразователя соединен со вторым входом i — того усилителя, первый вход которого соединен с выходом (1 — 1 ) †. го усилителя, первый вход первого усилителя подключен к входной клемме аналого-цифрового преобразователя, и блок управления, аналоговый коммутаторg первый и второй ,цифровые коммутаторы,преобразователь

,,последовательного кода, счетчик и

750721 блок контроля, прйчем выходы (К-1) ! усилителей соединены со второго по

К-й входами аналогового коммутатора, выход которого соединен со входом многопорогового блока сравнения, первый выход многопорогового блока сравнения соединен со входом преобразователя последовательного кода, выход которого соединен со входом второго цифрового коммутатора., второй выход многопорогового блока сравнения соединен с первым входом блока КоНТроля, выход преобразователя параллельного кода соединен со вторым входом блока контроля и входом первого цифрового коммутатора, 1 - и выход которого, динен со входом 1 — того 15 цифроаналогового преобразователя, выходы второго цифрового коммутатора соединены с входами счетчика, вызод которого соединен с третьим входом блока контроля и подключен к 20 выходной клемме аналого-цифрового преобразователя, первый вход аналогового коммутатора соединен с первым входом первого усилителя, вторые выходы цифроаналоговых преобразова- 5 телей соединены с четвертого по (К+2) — и входами блока контроля, выход которого соединен со входом блока управления, управляющие входы аналогового коммутатора, первого и второго цифровых коммутаторов, многопорогового блока сравнения, цифроаналоговых преобразователей и счетчика соединены с соответствующими выходами блока управления.

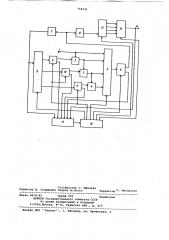

На чертеже представлена структурная схема предлагаемого аналого-цифрового преобразователя.

Он содержит вход 1, на который подается измеряемая величина, усилители 2,3,4, выходы которых соедине- 40 ны со входами аналогового коммутатора 5. Выход аналогового коммутатора

5 соединен со входом многопорогового блока сравнения 6, который осуществляет преобразование аналоговой вели- 45 чины в параллельный уяитарный код.

Этот код преобразуется в минимальный р-код преобразователем параллельного кода 7, выход которого через первый цифровой коммутатор 8 соединен со входами цифро-аналоговых преобразователей 9,10,11. Выход блока 6 также соединен со. входом преобразователя последовательного кода 12, осуществляющего преобразование параллельного унитарного кода в последовательный унитарный код. Выход преобразователя 12 через второй цифровой коммутатор 13 соединен с входом счетчика 14. Выход счетчика 14 является выходом 15 аналого- QQ цифрового преобразователя.

Алгоритм преобразования обеспечивается блокоМ управления 16, а контроль правильной работы блоком конт- . роля 17. 65

Процесс преобразования входной аналоговой величины в n — разрядный минимальный р-код происходит за ( циклов, в каждом из которых формируется m разрядов кода, В i — м цикле участвуют (i-1) усилителей, (i-1) цифроаналоговых преобразователей, i-й канал аналогового коммутатора и (i-1)-й канал первого и второго цифровых коммутаторов и остальные узлы схемы.

Аналого-цифровой преобразователь при отсутствии импульсных помех в преобразуемом аналоговом сигнале, а ,также сбоев в цифровых узлах преобразователя работает следующим образом.

В нервом цикле преобразуемая аналоговая величина со входа 1 . поступает на первый вход аналогового коммутатора 5, который под действием управляющего сигнала, поступающего из блока управления 16, передает ее на вход многопорогового блока сравнения 6. Многопороговый блок сравнения 6 преобразует входную аналоговую величину в.параллельный унитарный код, который преобразуется в параллельный минимальный р-код преобразователем 7 и в последовательный унитарный код преобразователем 12..Последовательный унитарный код через второй цифровой коммутатор 13 поступает на первый вход счетчика.На втором цикле минимальный р-код с выхода преобразователя 7 поступает через первый цифровой коммутатор 8 под действием управляющего сигнала из блока управления на вход первого цифро-аналогового преобразователя 9. Аналоговая величина соответствующая этому коду с первого выхода цифроаналогового преобразователя 9 подается на второй вход усилителя 2, на первый вход которого подана входная преобразуемая величина. Разность этих величин Л1 усиливается усилителем в 2 в М раэ, где:

М ð если m нечетное г

<х р если m четное г и подается на второй вход коммутатора 5.

Под действием управляющего сигнала блока 16 величина М передается на вход блока 6 ° Параллельный унитарный код соответствующий этой веллчине преобразуется в параллельный минимальный р-код преобразователем / и в последовательный унитарный код преобразователем 12. Последовательный уни тарный код передается через цифровой коммутатор 13 на второй вход счетчика 14, тем самым к содержимому счетчика добавляется результат преобразования второго цикла. На третьем и четвертом циклах аналого-цифровой преобразователь работает аналогичным образом, причем в работу включаются цибфоаналогобый преобразователь 10

750721

Формула изобретения

Аналого-цифровой преобразователь, содержащий (К-1) усилителей,.(К-1) цифроаналоговых преобразователей, многопороговый блок сравнения, пер" вый выход которого соединен со входом преобразователя параллельного кода, выход i — го цифроаналогового преобразователя соединен со вторым

50 и усилитель 3 на третьем цикле, цифроаналоговый преобразователь 11 и усилитель 4 на четвертом цикле.

При появлении импульсной помехи отрицательной полярности в аналоговых цепях на данном цикле, на последующих циклах будут появляться максимальные кодовые комбинации. Признаком неправильной работы является наличие хотя бы двух таких подряд идущих кодовых комбинаций с выхода преобразователя 7 на вход блока контроля

17. При этом блок контроля 17 вырабатывает сигнал, под действием которого блок управления 16 формирует последовательность сигналов приводящую ана1

15 .oro-цифровой преобразователь в исходное состояние, а затем обеспечивающую повторное преобразование.

В случае воздействия импульсной помехи положительной полярности на данном цикле, на последующих циклах 20 в блок контроля 17 поступит сигнал со второго выхода многопорогового блока сравнения 6. При этом с выхода блока 17 поступает сигнал на вход блока 16, который в свою очередь 25 вырабатывает сигналы, приводящие аналого-цифровой преобразователь в исходное состояние и обеспечивающие повторное преобраз ов ание .

Признаком сбоев цифровых узлов 30 является появление неминимальной формы представления кодов в этих узлах.

В этой форме представления, после каждой единицы в р-коде может следовать менее р нулей, что и фиксируется блоком контроля 17. Реакция блока управления 16 на сигнал из блока контроля 17 та же, что и в предыдущих случаях.

Введение новых блоков и связей позволяет повысить информационную надежность аналого-цифрового преобразователя. входом i — го усилителя, первый вход которого соединен с выходом (i-1) — го усилителя, первый вход первого усилителя подключен к входной клемме аналого-цифрового преобразователя, и блок управления, отличающийся тем, что, с целью повышения информационной надежности, в него введены аналоговый коммутатор, первый и второй цифровые коммутаторы, преобразователь последовательного кода, счетчик и блок контроля, причем выходы (K;1) усилителей соединены со второ го по К-й входами аналогового коммутатора, выход которого соединен со входом многопорогового блока сравнения,первый выход многопорогового блока сравнения соединен со входом преобразователя последовательного кода, выход которого соединен со входом второго цифрового коммутатора, второй выход многопорогового блока сравнения соединен с первым входом блока контроля, выход преобразователя параллельного кода соединен со вторым входом блока контроля и входом первого цифрового коммутатора, i — и выход которого соединен со входом i — го,циф1 оаналогового преобразователя, выходы второго цифрового коммутатора соединены с входами счетчика, выход которого соединен с третьим входом блока контроля и подключен к выходной .клемме аналогоцифрового преобразователя, первый вход аналогового коммутатора соединен с первым входом первого усилителя, вторые выходы цифроаналоговых преобразователей соединены с четвертого по (K+2) — и входами блока контроля, выход которого соединен со входом блока управления, управляющие входы аналогового коммутатора, первого .и второго цифровых коммутаторов, многопорогового блока сравнения, цифро-аналоговых преобразователей и счетчика соединены с соответствующими выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Великобритания, заявка

М 13187..75, кл. G 4 Н, 01.08.73

2. Гитис Э ° И. Преобразователи информации для ЭЦВЦ, М.,"Энергия,"

1975, с. 319 (прототип).

750721

Составитель Г. Шаповал

Редактор В. Голышкина Техред М.Петко

Корректор Р). Макаренко филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 4670/45 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035,Москва, Ж-35, Раушская наб., д. 4/5