Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСХОМУ СВИ ЕТИЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлеио040478 (21) 2598537/18-21 с присоединением заявки № (53)м. Ки.

Н 03 К 13/17 (23) Приоритет

Гасударственный комитет

СССР но делам изобретений и открытий

Опубликовано 230780. Бюллетень ¹ 27

Дата опубликования описания 230780 (53) УДК 681. 325 (088.8) (72) Автор изобретения

В. А. Шульгин

Воронежский ордена Ленина государственный университет им . Ленинского комсомола (71) Заявитель (54 ) AHAJIOI О-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике и может использоваться в устройствах связи между аналоговыми устройствами и цифровыми вычисли- 5 тельными машинами.

Известен аналого-цифровой преобразователь, содержащий набор компараторов, каждый из которых срабатывает при определенном значении 10 входного напряжениями при этом подает на- выход преобразователя набор импульсов, соответствующих в двоичном коде напряжению срабатывания (Ц .

Однако устройство отличается слож-1 ностью, дороговизной и не находит широкого применения.

Известен аналого-цифровой преобразователь, содержащий последовательно соединенные анализирующие элементы, выполненный на МОП-транзисторах и конденсатор, включенный на входе каждого анализирующего элемента, который вырабатывает нулевой или еди-25 ничный логический сигнал в зависимости от знака разности между величиной сигнала на его входе и соответствующей этому элементу весовой величиной $2(.

Однако устройство имеет низкое быстродействие.

Целью изобретения является повышение быстродействия.

Указанная цель достигается тем, что в аналого-цифровом преобразователе, содержащем последовательно соединенные анализирующие элементы, каждый анализирующий элемент содержит повторитель тока, биполярный транзистор, пороговое устройство, инвертирукщий повторитель тока, генератор весового тока и компаратор, причем вход и выход повторителя тока соединены соответственно с входной и выходной шинами анализирукщего элемента, эмиттер биполярного транзистора соединен с генератором весового тока, базы — со входом инвертирующего повторителя тока, коллектор — со входом повторителя тока, выход неинвертирующего повторителя тока соединен с выходом повторителя тока, причем инвертирующий повторитель тока выполнен на двух транзисторах одного типа проводимости, соединенные змиттеры которых подключены к источнику питания, коллектор и база первого транзистора

750726 соединены между собой и с базой вто рого транзистора, пороговое устройство выполнено на компараторе и транзисторе того же типа проводимости, база и эмиттер которого соединены соответственно с базами и эмиттерами транзисторов в инвертирующем повторителе тока, а коллектор соединен со входом компаратора, выход которого подключен к выходной шине анализи рующего элемента.

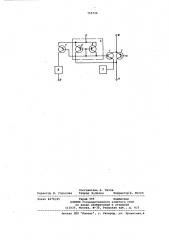

Структурная электрическая схема одного анализирующего элемента приведена на чертеже.

Устройство содержит транзисторы

1 и 2 разного типа проводимости, генератор 3 весового тока, инвертирующий повторитель 4 тока, состоящий из транзистора 5 в диодном включении и транзистора 6, транзистор 7 и компаратор 8 представляет собой пороговое устройство. Эмиттерные переходы согласованных транзисторов 5,6 и 7 включены параллельные друг другу, коллектор и база транзистора 5 соединены с базой транзистора 1, коллектор транзистора

6 соединен с коллектором транзистора

2, а коллектор транзистора 7 с компаратором 8, клемма 9 — выход логического сигнала, клемма 10 — вход анализируемого тока, а клемма 11 используется для подключения входа следующего анализирующего элемента или шины питания.

Когда входной ток на клемме 10 больше весового тока генератора 3, разность этих токов поступает на эмиттер открытого транзистора 2 и тем самым на клемму 11. При этом ток базы транзистора 1, и следовательно, ток эмиттера транзистора 5 практически равны нулю, что определяет первое состояние компаратора 8 и тем самым первый уровень логического сигнала на клемме 9 вследствие равенства тока коллектора транзистора эмиттерному току транзистора 5, обеспеченному параллельным включением эмиттерных переходов этих транзисторов.

Когда входной ток становится меньше весового, транзистор 2 запирается, а транзистор 1 входит в насыщение и ток его базы в этом случае будет равен разности входного и весовых токов. Эта разность через транзистор

7 поступает на компаратор 8 и меняет его состояние, чем обеспечивается наличие второго уровня логического сигнала на клемме 9. Одновремейно .через транзистор 6 разность токов поступает на клемму 11.

2О

5.5

Таким образом, через клемму 11 на вход следующего анализирующего элемента поступает модуль разности входного и весового токов, а знак этой разности определяет уровень логического сигнала на клемме 9.

Время преобразования сигнала примерно равно сумме времен обрабатывания отдельных анализирующих элемен- тов, каждое иэ которых определяется главным образом временем рассасыва,ния неосновных носителей для современных транзисторов 10-50 мс.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий последовательно соединенные анализирующие элементы, отличающийся тем, что, с целью повышения быстродействия, каждый анализирующий элемент содержит повто) итель тока, биполярный транзистор, пороговое устройство, инвертирующий повторитель тока, генератор весового тока и компаратор, причем вход и выход повторителя,тоКа соединены соответственно с входной и выходной шинами анализирующего элемента, эмиттер биполярного транзистора соединен с генератором весового тока, база — со входом инвертирующего повторителя тока, коллектор — co входом повторителя тока, выход инвертирующего повторителя тока соединен с выходом повторителя тока.

2. Преобразователь по п.1, о тл и ч а ю шийся тем, что инвертирующий повторитель тока выполнен на двух транзисторах одного типа проводимости, эмиттеры которых подключены к источнику питания, коллектор и база первого транзистора соединены между собой и с базой второго транзистора, пороговое устройство выполнено на компараторе и транзисторе того же типа проводимости, база и эмиттер которого соединены соответственно с базами и эмиттерами транзисторов инвертирующего повторителя тока, а коллектор соединен со входом компаратора, выход которого подключен к выходной шине анализирующего элемента.

Источники информации, принятые во внимание при экспертизе

1. Гребен A.Á. Проектирование аналоговых интегральных схем. М., энергия", 1976, с. 231-232.

2. Патент Японии 9 52-14071, кл. 98(5)F1, 1977 (прототип).

750726

Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4б70/45

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Составитель А. Титов

Редактор П. Горькова Техред Я.Петко Корректор И. Муска