Дешифратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ %ТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<>750731 (61) Дополнительное к авт. свид-ву 9 652706 (22) 3аявлено 211177 {2f) 2545887/18-21 (51)М. Кл.

Н 03 К 13/243

G 06 F 5/02 с присоединением эа«вки Мо

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 230780. Бюллетень 89 27

Дата опубликования описания 250780 (53) УДК 621.374.3 (088.8) (72) Авторы изобретения

Б.Е. Гласко и A.К. Култыгин. (71) Заявитель (5 4 ) ДЕИИФРАТОР

Изобретение относится к автоматйке и вычислительной технике и предназначено для использования в запоминающих устройствах. 5

В основном авт. свид. 9 652706 описан дешифратор, содержащий дешифраторную матрицу, к каждому столбцу которой подключены две одноименные () входные шины, а к каждой строке две одноименные выходные шины, соединенные с соответствующей нагрузкой, в котором в каждом .узле дешифраторной матрицы столбец соединен со строкой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матрицы осуществлена включением первого резистора между первой

: входной шиной столбца и первой выходной шиной строки и второго резистора между второй входной шиной столбца и второй выходной шиной строки, а связь другого знака — включением первого резистора между второй входной шиной столбца с первой выходной шиной строки и второго резистора между первой входной шиной столбца и второй выходной шиной. строки.

Недостатком данного дешифратора является недостаточный коэффициент полезного действия и большие потери мощности в элементах.

Целью изобретения является уменьшение потерь мощности в элементах дешифратора и повышение его КПд.

Поставленная цель достигается тем, что в дешифратор, содержащий дешифраторкую, построенную в соответствии с ортогональной матрицей Адамера матрицу, к каждому столбцу которой подключены две одноименные входные шины, а к каждой строке — две одноименные выходные шины, соединенные с соответствующей нагрузкой, в которой в каждом узле дешифраторной матрицы столбец соединен со строкой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матрицы осуществляется вклю-. чением первого резистора между первой входной шиной столбца и первой выходной шиной строки и второго резистора между второй входной шиной столбца и второй выходной шиной строки, а связь .другого знака — включением первого резистора между второй входной шиной столбца и первой выходной шиной строки и второго реэис" тора между перйой входной шиной столбца и второй выходной шиной стро750731 ки, последовательно с каждым резис.тором связи включены встречи друг другу два нелинейных элемента, имеющих в одном направлении вольт-амперную характеристику с участком отрицательного сопротивления, а в другом направлении — сопротивление близкое к нулю, например, Л -диоды.

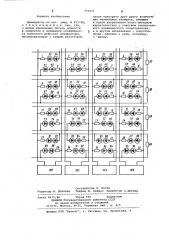

Принципиальная электрическая схема описываемЬго дешифратора приведена на чертеже.

Дешифратор содержит резисторы связи -1-32, нелинейные элементы 33...96, нагрузки 97... 100 формирователи входных сигналов (например, триггеры) или ключи 101...1 04.

Дешифратор работает следующим образом. I

На входные шины дешифратора долж- ны быть поданы входные сигналы равной амплитуды, полярность которых соответствует знакам членов одной из строк матрицы Адамара. Если, например, должна быть выбрана нагрузка

97, то. полярность входных сигналов определяется строкой "++++". При этом положительной . полярности входного сигнала соответствует наличие положительного или отрицательного потенциала на первой и нулевого потен.циала — на второй одноименных входных шинах (т.е, Е, О), а отрицательной полярности входного сигнала обратное распределение потенциалов (т.е. О, Е). Если, например, на вход ные шины дешифраторной матрицы подана комбинация сигналов Е, О; F,, О;

Е„О; Е О, то токи от источников входных сигналов протекают через цепочки 1"33-34, 2-35-36, 3-37-38, 4-39-40, суммируются в нагрузке 97 и через цепочки 5-41-42, 6-43-44, 7-45-46, 8-47-48 стекают к шинам, имеющим нулевой потенциал. Токи в остальных нагрузках дешифратора равны нулю. Рассмотрим, например, распределение потенциалов на зажимах нагрузки 98: цепочки 9-49-50, 10-51-52 и 11-53-54, 12-55-56 образуют делитель напряжения, определяющий потенциал на одном зажиме нагрузки 98, цепочки 14-59-60, 13-57-58, 16-63-64, 15-61-62 образуют делитель, определяющий потенциал иа другом зажиме той же нагрузки; поскольку все цепочки связи идентичны, то на обоих зажимах нагрузки 98 потенциалы равны Е/2, и ток через нее не протекает. По той же причине не протекает ток через нагрузки 99, 100.

При полярности входных сигналов, определяемой какой-либо другой строкой матрицы Адамара, работа дешифратора аналогична вышеописанной: на зажимах соответствующей нагрузки имеется разность потенциалов, и через нее протекает ток, равный сумме токов, протекающих через цепочки связи между входными формирователями

IH данной нагрузкой, а на зажимах остальных нагрузок разность потенциалов равна нулю.

Влияние нелинейных элементов на работу дешифратора состоит в следующем. Предположим сначала, что они отсутствуют, т.е. в узлах дешифраторной матрицы включены только резисторы, имеющие сопротивление Я.. Пусть величина сопротивления нагрузок, подключенных к входным шинам, равна r. Тогда через каждый из резисторов связи, включенных в цепь выбранной нагрузки, протекает ток н д, — = —, а через каждый резес(m < QrlfP тор связи в цепи невыбранных нагрузок протекает ток 4<-P,"I g, причем n= Р/г, а в — порядок матрицы Адамара, на основе каторой построена дешифратор-,О ная матрица. Ток 3 больше тока 3 „

З (ге 9.n)l ln ?П так как отношение

Т1= а больше 1 при любых е ) О, пъ О. Отсюда следует, что чисто реэистивный дешифратор имеет очень низкий коэффи-, циент полезного действия. Кроме того, отсюда становится ясно, каким путем коэффициент полезного действия может быть увеличен наиболее эффективно: необходимо максимально уменьшить ток, протекающий через резисторы связи, включенные в цепь невыбранных нагрузок. Поскольку напряжение, приложенное к этим резисторам, больше напряжения, падающего на резисторах в цепи выбранной нагрузки, а ток, протекающий через них, должен быть меньше, то последовательно с резисторами связи необходимо включить нелинейный элемеит, имеющий вольтамперную характеристику с участком отрицательного дйнамического сопротивления.Зго и дает возможность уменьшить ток, протекающий через резисторы связи в цепях невйбранных Нагрузок, относительно тока, протекающего через резисторы связи в цепи выбранной нагрузки, при большем напряжении, приложенном к первым резисторам. При использовании в качестве такого нелинейного элемента л — диода ток, протекающий через резисторы связи в.цепях невыбранных нагрузок, уменьшается практически до нуля; при этом коэффициент полезного действия дешифратора очень сильно возрастает за счет того,что снижаются практически до нуля потери мощности в резисторах связи, включенных в цепи невыбранных нагрузок. Поскольку при различных комбинациях входных сигналов дешифратора токи через цепочки связи протекают в том и другом направлениях, последовательно с резистором необходимо включить два встречно включенных нелинейных элемента.

750731

Формула изобретения

Составитель Л. Багян

Редактор Н. Козлова Техред M . .Рейвес Корректор С.Шекмар

Заказ 4671/46 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушекая наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Дешифратор по авт. свид. 9 65270 отличающийся тем, что, с целью уменьшения потерь мощности в элементах и повышения коэффициента полезного действия дешифратора, последовательно с каждым резистором связи навстречу друг другу включены два нелинейных элемента, имеющих

6, в одном направлении вольт-амперную характеристику с участком отрицательного динамического сопротивления, а в другом направлении — сопротивление, близкое к нулю, например, Л -диоды.