Резервированный триггерный делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

750743 (61) Дополнительное к авт. свид-ву (22) Заявлено 011277 (21) 2548463/18-21 (51)м. Кп, с присоединением заявки Мо (23) Приоритет

Н 03 К 23/02

Государственный кормитеT

СССР по делам изобретеиий и открытий

Опубликовано 230780 Бюллетень Мо 27 (53) УДК 621. 374..4 (088.8) Дата опубликования описания 230 780 (72) Авторы изобретения

A.Ã.Açàðîâ и Г.И.Цветков

Научно-исследовательский институт автоматики и электромеханики при Томском институте автоматизированных систем управления и радиоэлектроники (71) Заявитель (54) РЕЗЕРВИРОВАННЫЙ ТРИГГЕРНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к автоматике и вычислительной технике и мо-, жет быть использовано, в частности, при построении надежных задающих генераторов.

Известны резервированные делители частоты, выполненные на триггерах j 1) и (2), Известен делитель частоты., содержащий триггерные счетчики на

3КС-триггерах, мажоритарные элементы, инверторы и устраняющий сбой в работе триггеров при любом одиночном отказе.

Это достигается тем, что прямые выходы мажоритарных элементов соединены с 3 входами, а инвертированные выходы с К-входами входных

3КС-триггеров каждого счетчика (1) .

Недостатком указанного устройства является его сложность и сравнительно невысокая надежность,так как работоспособность делителя сохраняется только при одном сбое.

Известен также резервированный триггерный делитель частоты, содержащий основной канал деления с последовательно включенными триггерами и резервные триггеры (lj.

Требуемая кратность резервирования достигается тем, что к выходу основного канала деления последовательно подключены резервные триггеры, причем каждый триггер запускается через элемент ИЛИ, вход которого через развязывающие конденсаторы соединен с выходами двух предыдущих триггеров, а выход послед1О него триггера основного канала деления и каждого резервного триггера соединен с избирательным каскадом, выход которого является выходом делителя частоты.

15 Однако при определенных отказах в любом из триггеров теряется информация о неисправном триггере и в делителе возникают сбои.

Целью изобретения является по20 вышение надежности работы устройства.

Это достигается тем, что в резервированном триггерном делителе частоты, содержащем резервный триггер и каналы деления, каждый из которых содержит триггер, вход которого подключен к выходу элемента ИЛИ пре« дыдущего канала деления, вход резервного триггера подключен к выходу элемента ИЛИ последнего канала деле4

750743 ния, а выходы через избирательный каскад — к выходам триггера последнего канала деления, в каждый канал деления введены дифференцирующие цепи, дополнительный элемент ИЛИ и элемент ИЛИ-НЕ, при этом в каждом канале деления выход дополнительного элемента ИЛИ через первую дифференцирующую цепь подключен к одному из входов элемента ИЛИ, выход элемента ИЛИ-НЕ через вторую дифференцирующую цепь — к другому вхо, ду элемента ИЛИ, прямой выход триггера соединен с первым входом дополнительного элемента ИЛИ своего канала и со вторым входом дополнительного элемента ИЛИ последующего канала деления, а инверсный выход — с первым входом элемента ИЛИ-НЕ своего канала деления и со вторым входом элемента

ИЛИ-НЕ другого канала деления.

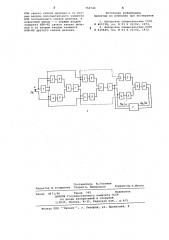

На чертеже представлена структурная электрическая схема резервированного триггерного делителя частоты для случая однократного резервирования.

Устройство содержит триггеры 1, элементы ИЛИ 2, 3, элементы ИЛ -HE 4, дифференцирующие цепи 5, резервный триггер б, избирательный каскад 7.

Входы избирательного каскада 7 соединены с прямыми и инверсными выходами триггера 1 последнего канала деления и резервного триггера б. Вход каждого триггера 1 подключен к выходу элемента ИЛИ 3, входы которого через дифференцирующие цепи 5 подключены к выходам элементов ИЛИ 2 и

ИЛИ-HE 4. Входы элементов ИЛИ 2 подключены к прямым выходам двух предыдущих, триггеров 1, а входы элемента ИЛИ-НЕ 4 — к инверсным выходам этих триггеров.

Устройство работает следующим образом.

Прямой сигнал Q c каждого триггера 1 поступает одновременно на два элемента ИЛИ 2, а инверсный Q — на два элемента ИЛИ-HE 4. Выходные импульсы элементов ИЛИ 2 и ИЛИ-НЕ 4 поступают на дифференцирующие цепи

5 и далее на элемент ИЛИ 3, который запускает последующий триггер.

При нормальной работе (интервал времени -t,) на выходе элемента

ИЛИ 3 формируются узкие импульсы, которые поступают на вход последующего триггера. На вход избирательного каскада 7, который выделяет сигнал требуемой частоты, поступают сигналы с триггера 1 последнего канала деления (f, = cgz / К ) и с резервного триггера б (f = f6„/2V ), где К вЂ” коэффициент деления. Если триггер 1 остановился в состоянии

9 = 0 (интервал времени t, -t>), то на выходе элемента ИЛИ-НЕ 4 сигнал исчезает„ ) а частота импульсов на выходе элемента ИЛИ 2 удваивается.

На выходе элемента ИЛИ 3 частота импульсов также удваивается и делитель в целом продолжает функционировать нормально, так как на выходе . резервного триггера 6, нагруженного на избирательный каскад

7, присутствуют импульсы требуемой частоты f

ИЛИ-НЕ 4 частота импульсов удваивается, и делитель в целом продол15 жает функционировать нормально, так как последующий триггер продолжает запускаться от элемента ИЛИ 3 импульсами удвоенной частоты и на

1 выходе резервного триггера б сущест20 вуют импульсы требуемой частоты f „ /К.

Отказ любого из элементов ИЛИ 2, ИЛИ-НЕ 4, дифференцирующих цепей 5, ИЛИ 3 аналогичен отказу последующего триггера и поэтому нет необр5 ходимости в их резервировании.При отказе любого из элементов в предложенном делителе отсутствуют какие-либо сбои и переходные процессы. Это достигается тем, что вход элемента ИЛИ 3 через дифференцирующие цепи 5 соединен с выходами дополнительно введенных элементов

ИЛИ 2 и ИЛИ-НЕ 4,входы ко орых подключены соответственно к прямым и инверсным выходам двух предыдущих триггеров.

О

Формула изобретения

Резервированный триггерный делитель частоты, содержащий резервный триггер и каналы деления, каждый из которых содержит триггер, вход которого, подключен к выходу элемента ИЛИ предыдущего канала деления, вход резервного триггера подключен к выходу элемента ИЛИ последнего канала деления, а выходы через избирательный каскад — к выходам триггера последнего канала деления, о тл и ч а ю шийся тем, что, с целью повышения надежности работы устройства, при обеспечении требуемой кратности резервирования, в каждый канал деления введены дифференцирующие цепи, дополнительный элемент ИЛИ и элемент ИЛИ-НЕ, при этом в каждом канале деления выход дополнительного элемента ИЛИ через первую дифференцирующую цепь подключен к одному из входов элемента

ИЛИ, выход элемента ИЛИ-НЕ через вторую дифференцирующую цепь — к другому входу элемента ИЛИ, прямой выход триггера соединен с первым входом дополнительного элемента

750743

Составитель В.Глатман

Редактор В.Голышкина Техред А. Щепанская Корректор И.Муска

Вакаэ

4671/46 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

ИЛИ своего канала деления и со вторым входом дополнительного элемента

ИЛИ последующего канала деления, а инверсный выход — с первым входом элемента ИЛИ-НЕ своего канала деления и со вторым входом элемента

ИЛИ-НЕ другого канала деления.

Источники информации принятые во внимание при экспертиэе

1. Авторское свидетельство СССР

Р 465738, кл. Н 03 К 23/02, 1973.

2. Авторское свидетельство:СССР

Р 449449, кл. Н 03 К 23/00, 1972: