Устройство для обработки и разделения сигналов динамических процессов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О Il И (" А Н И Е ()750752

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

:.® (6l ) Дополнительное к авт. свил-ву (22) За я влено 17.03.78 (21) 2591235/18-09 (5! )М. Кл.

Н 04 1 25/16 с присоединением заявки М

Государственный комитет (28) Приоритет по делам нзабретеиий н открытий

Опубликовано 23.07.80. Бюллетень рр 27

Дата опубликования описания 25,07.80 (53) УДК

621.394.6 (088.8) Т. Д Пилипенко, И. И. Миронов и Ю. Н. Костин (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ И РАЗДЕЛЕНИЯ СИГНАЛОВ

ДИНАМИЧЕСКИХ ПРОЦЕССОВ

Изобретение относится к радиотехнике и может использоваться для обработки больших потоков информации.

Известно устройство для обработки и разделения сигналов динамических процессов на аддитивные составляющие, содержащее последовательно соединенные блок приема входных данных, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления статистических характеристик сигналов и блок графического отображения о информации, а также второй делитель сигналов и блок последовательного сравнения сигналов, выход которого через счетчик количества инверсий подключен к первым входам !

5 первого блока сравнения и второго блока сравнения, к вторым входам которых подключены соответствующие выходы блока оперативной памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого подключен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оперативной памяти и. к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вычисления статистических характеристик сигналов подключен к первому входу блока формирования выходной информации, а другой выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов (1l .

Однако известное устройство не обеспечивает достаточной точности разделения сигналов.

Цель изобретения — повышение точности разделения.

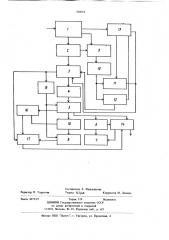

Для этого в устройство для обработки и разделения сигналов динамических процессов на аддитивные составляющие, содержащее последовательно соединенные блок приема входных данных, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления статистических характеристик сигналов и блок графичесИз блока 1 приема результаты измерения х; поступают в блок 2 задержки, где они задерживаются на время дескретизации И и в блок 9 последовательного сравнения, в который поступают результаты, задержанные в блоке 2 задержки. Блок задержки 2 пропускает результаты в блок 3 буферной памяти. В блоке 9 последовательного сравнения последовательно сравниваются измерения текущие со всеми предшествующими и формируется инверсия Т; .

Каждое измерение, получившее оценку инверсии, равную 1, пропускается в счетчик

10 количества инверсий (для текущего измерения). Результаты из счетчика 10 пропускаются в два блока 11 и 12 сравнения, в которые поступают результаты из блока

13 оперативной памяти. Блок 13 оперативной памяти связан с блоком 1 приема. В блоке 13 оперативной памяти содержатся вставки о величинах допустимого количества инверсий для текущего измерения: Тмакс у

Тмин.

В блоке 11 сравнения сравнивается текущее количество инверсий Т;, с максимальным

Тмакс, поступившим из блока 13 оперативной памяти, а в блоке 12 сравнения — с минимальным Тмин. Если в результате сравнения

Т будет больше Тмакс или меньше Тмин, то будет сформирован сигнал С, или С,.

Появление сигнала С или С> свидетельствует о конце интервала стационарности для заданного диапазона инверсий интервала стационарности.

Сигналы С, или С, направляются в блок

3 буферной памяти. В блоке 3 буферной памяти по этим сигналам открывается память от момента поступления сигнала, и все заломинаемые между сигналами измерения, т.е. измере ния продолжительностью стационарного участка передаются в сумматор 4, где они суммируются и передаются в делитель 5, в котором вычисляется величина математического Ожидания стационарного участка по информации от сумматора 4 и счетчика 15 о количестве измерений на участке стационарности. В дели50 теле 5 осуществляется операция деления реь зультата от сумматора 4 на результат от счетчика 15 и определяется величина математического ожидания стационарного участка. Этот результат для текущего математического ожидания m направляется в блок 16 задержки, где задерживается на время atm< и в вычитаи ющий блок 18, в котором определяется разность текущего математического ожидания Am c

3 75075 кого отображения информации, а также второй ° делитель сигналов и блок последовательного сравнения сигналов, выход которого через счетчик количества инверсий подключен к первым входам первого блока.сравнения и второго блока сравнения, к вторым входам которых подключены соответствующие выходы блока оперативной памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого подключен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оперативной памяти и к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вычисления статистических характеристик сигналов подключен к первому входу блока формирования выходной информации, а другой выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов, введены второй блок задержки и два вычитающих блока, при этом первый дополнительный выход первого делителя сигналов подключен через второй блок задержки к первому входу первого вычитающего блока, второй вход которого соединен с входом счетчика сигналов, выход которого через второй делитель сигналов подключен к третьему входу первого вычитающего блока, выход которого подключен к второму входу блока формирования выходной информации, к третьему входу которого подключен вы ход первого делителя сигналов, а выход блока формирования выходной информации подключен к другому входу блока графического отображения информации, причем второй дополнительный выход первого делителя сигналов подключен через второй вычитаюшнй блок к другому входу второго целителя сигналов, а дополнительный выход второго блока задержки подключен к другому входу второго вычитающего блока.

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для обработки и разделения сигналов динамических процессов содержит блок

1 приема входных данных, блок 2 задержки, блок 3 буферной памяти, сумматор 4, делител

5 сигналов, блок 6 вычисления статистических характеристик сигналов, блок 7 графического отображения информации, делитель 8 сигналов, блок 9 последовательного сравнения сигна лов, счетчик 10 количества инверсий, блоки

10 и 11 сравнения блок 13 оперативной памят блок 14 формирования выходной информации, 2 4 счетчик 15 сигналов, блок 16 задержки, два вычитающих блока 17 и 18.

Ус рой во работает следующим Образом

750752

15 юшего текущему.

От счетчика 15 поступают как суммарное количество измерений между математическими ожиданиями, так и количество измерений, начиная от предшествующего текущего m математическому

И ожидан ию, т.е. из мер ения р, В делителе 8 вычисляется величина надбавки, и направляется в вычитаюший блок 17, в который поступает величина предшествующего текущему моменту математического ожидания

m из блока задержки 16 и величина текущего измерения х; иэ блока 3 буферной памяти. В блоке 17 осуществляется операция вычисления стационарного остатка Ьх;, 2ьп р1 согласно выражению Лх; = х — (m + Р1

Г-1,п которая направляется в блок 14 формирования, в который поступают также результаты от делителя 5 о величине математического ожидания.

В блок 6 вычисления поступают результаты от блока 3 буферной памяти через делитель

5 и в блоке 6 вычисления вычисляются статистические характеристики. Результаты от блоков

6 и 14 вычисления и формирования направляются в блок 7 графического отображения, в котором исходная информация динамического 40 процесса разделяется на информацию в виде математического ожидания остатка, а также даются необходимые статистические характеристики процесса.

1. Заявка N 2584490/18-09, 1978, по которой принято положительное решение (прототип). предшествующим m, . Из блока 16 задержки результаты передаются в вычитаюший блок 17, а из вычитающего блока 18 и счетчика 15 в делитель 8, в котором определяется величина — коэффициент прямой меж2.лme

+- К ду вычисленнььми соседними математическими

2 д, пэ D 7 ожиданиями п и m и " — надбавка

Pyg к математическому ожиданию m для измерения р, начиная отсчет от измерения п .1, где 1; k — количество измерений стационарного участка, предшествующего текущему и текущего; р — номер измерения, начиная от математического ожидания предшеству45

Положительным качеством устройства является то, что сумм арны и сигнал динамического процесса разделяется на статическую и динамическую составляющуто, при этом учитывается наличие тренда в процессе — рост или убывание, 50 что позволяет снизить погрепщость при выделении динамической составляющей процесса.

Формула изобретения

Устройство для обработки и разделения сигналов динамических процессов на аддитивные составляющие, содержащее последовательно соединенные блок приема входных данных, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления статистических характеристик сигналов и блок графического отображения информации, а также второй делитель сигналов и блок последовательного сравнения сигналов, выход которого через счетчик количества инверсий подключен к первым входам первого блока сравнения и второго блока сравнения, к вторым входам которых подключены соответствующие выходы блока оператив. ной памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого подключен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оперативной памяти и к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вычисления статистических характеристик сигналов подключен к первому входу блока формирования выходной информапии, а .другой выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов, о т л и ч а ю ш е е с я тем, что, с целью повышения точности разделения, введены второй блок задержки и два вычитающих блока, при этом первый дополнительный выход первого делителя сигналов подключен через второй блок задержки к первому входу первого вычитаюшего блока, второй вход которого соединен с входом счетчика сигналов, выход которого через второй делитель сигналов подключен к третьему входу первого вычитающего блока, выход которого подключен к второму входу блока формирования выходной информации, к третьему входу которого подключен выход первого делителя сигналов, а выход блока формирования выходной информации подключен к другому входу блока графического отображения информации, причем второй дополнительный выход первого делителя сигналов подключен через второй вычитающий блок к другому входу второго делителя сигналов, а дополнительный выход второго блока задержки подключен к другому входу второго вычитающего блока.

Источники информации, принятые во внимание при экспертизе

750752

Составитель А. Меньшикова

Техред Н.Граб Корректор М. Демчик

Редактор П. Горькова

Заказ 4673/47

Филиал НПП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 729 Подлисное

ЦНИИПИ Государственного комитета СССР по делам изобретений н открытий

l 13035, Москва, Ж вЂ” 35, Раушская наб„д. 4/5