Цифровой измеритель действующего значения сигнала

Иллюстрации

Показать всеРеферат

1

Г тют НО- Ех Н к Е--НС т 1 о 1НМ -М " и и е

ИЗОБРЕТЕН ИЯ

Свюз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 19 06.78 (2I ) 2629521/18-21

Э (5l)M; Кл.

G 01 R 13/02 с присоединением заявки М

Гооудеротебииый комитет (23) Приоритет

an делам иаобретеиий и открытий

Опубликовано 30.07.80. Бюллетень Ж 28

Дата опубликования описания 01 08 80 (53) УД К 68 1. 325 (088.8) (72) Авторы изобретения

И. Я. Вилннский, П. Л. Корольков, А. В. Краузе н А, К. Мнкелсон (71) Заявитель

Институт электроники и вычислительной техники

AH Латвийской CCP (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ДЕЙСТВУЮШЕГО

ЗНАЧЕНИЯ СИГНАЛА

Изобретение относится к измеритель ной технике, а именно к цифровым приборам для измерения действующего значения детерминированных и случайных сигналов, и может быть использовано в

5 технике связи, в производстве и испытаниях различных радиоэлектронных при» боров и систем, а также в процессе научных исследований.

Известен цифровой коррелометр, используемый в качестве измерителя действующего сигнала к работающий в режиме измерения автокорреляционной функции сигнала при нулевой задержке времени с последующим извлечением квадратного корня нз полученного результатата, содержащий входной усилитель, генератор псевдослучайных чисел с коммутатором, два цифроаналоговых преобразователя, два компаратора, генератор тактовых импульсов, умножитель, интегратор, схему считывания и регист-., рирующее устройство (11.

Однако такой измеритель имеет двухканальную структуру, содержит много аналоговых узлов, относительно нестабилен, имеет большую погрешность результатов измерений и низкое быстродействие.

Известен также коррелометрнческнй цифровой измеритель действующего зна» чення сигнала, который содержит входное устройство, выход которого подключен к первым входам компараторов, генератор тактовых импульсов, первый выход которого через первый генератор псевдослучайных чисел подключен к цифроаналоговому преобразователю н K первому информационному входу арифметического устройства, последовательно соединенного с регистрирующим устройством

121.

Недостатком этого измерителя является сравнительно большое время измере» ния, которое ограничивается частотой стробировання компараторов н временем

2170 4

3 75 установления цифроаналогового преобразователя.

Пель изобретения — повышение быстродействия цифрового измерителя действующего значения.

Укаэанная цель достигается тем, что цифровой измеритель действующего значения сигнала, содержащий входное устройство, выход которого подключен к первым входам 2 и компараторов, генератор тактовых импульсов, первый выход которого через первый генератор псевдослучайных чисел подключен к цифроаналого-. вому преобразователю и к первому информационному входу арифметического устройства, последовательно соединенного с регистрирующим устройством введены два источника тока, два делителя из и -1 последовательно соединенных резисторов в каждой, два коммутатора, второй генератор псевдослучайных чисел и элемент ИЛИ, при этом выход первого источника тока и прямой выход цифроаналогового преобразорателя, а также выход второго источника тока и инверсный выход цифроаналогового преобразователя подключены к соответствующим выводам первого и второго делителей, один из выводов каждого резистора обоих делителей соединен со вторым входом соответствующего компаратора, входы стробирования компараторов подключены ко второму выходу генератора тактовых импульсов, соединенного со вхо. дом генератора псевдослучайных чисел, выход которого подключен ко второму информационному входу арифметического устройства и к управляющим входам о6оих коммутаторов, информационные входы которых соединены с выходами компара-, торов, прямой выход первого коммутатора и инверсный выход второго подключены соответственно к входам элемента

ИЛИ, выход которого соединен с управляющим входом а рифме тическо го устройства.

Это позволяет повысить частоту стробирования компараторов, без увеличения частоты переключения цифроаналогового преобразователя и, таким образом, сократить время измерения. Степень повыmenus быстродействия зависит от числа параллельно работающих компараторов, а также от их быстродействия. ПогpeIIIH0cTb измерения в предлагаемом измерителе остается такой же, как в изВестном òð0ÀcòBe, 5

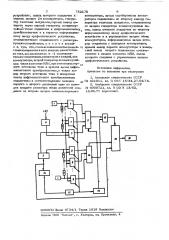

На чертеже представлена блок-схема предлагаемого цифрового измерителя действующего значения сигнала.

Измеритель содержит источник 1 тока, выход которого через делитель из (п-1) последовательно соединеннык резисторов 2, соединен с прямым выходом цифроаналогового преобразователя 3, Выход источника 4 тока через делитель из (и -1) последовательно соединенных резисторов 5 соединен с инверсным выходом цифроаналогового преобразователя 3.

Выход входного устройства 6 соединен с первыми входами всех компараторов двух групп 7 и 8 из и компараторов в каждой.

Второй выход каждого компаратора 7 соединен с рдним выводом соответствующего резистора 5. Выходы компараторов 7 подключены к информационным входам коммутатора 9, а выходы компараторов

8 - к информационным входам коммутатора 10. Первый выход генератора 11 тактовых импульсов соединен со входами стробирования компараторов 7 и 8 и со входом генератора 1 2 псевдослучайных чисел. Выход генератора 12 псевдослучайных чисел подключен к управляющим входам коммутаторов 9 и 10 и к одному информационному входу арифметического устройства 13. Второй выход генератора 11 тактовых импульсов соединен со входом генератора 14 псевдослучайных чисел, а выход генератора 14 подключен ко входу цифроаналогового преобразователя 3 и к другому информационному входу арифметического устройства 13.

Прямой выход коммутатора 9 и инверсный выход коммутатора 10 соединен соответственно со вкодом элемента 15 ИЛИ, выход которого подключен к управляющему входу арифметического устройства 13.

Выход последнего соединен с регистрирующим устройством 16.

Устройство работает следующим образом, Измеряемый сигнал х(1)Ц-с,п)центрируется, приводится к требуемому масштабу во входном устройстве 6 и поступает на первые входы всех компараторов 7 и 8. Каждый к мпаратор 7 и 8 работает со своим, отличающимся от соседнего на величину опорным уровнем. Такая "шкала опорных уровней создается подключением источников тока 1 и 4 через цепь последовательно соединенных резисторов 2 и 5 к соответствующим выходам преобразователя 3. Направление тока в источниках

752i

1 и 4 выбирается так, что группа из и компаоаторов 7 работает с опоиными vuoa-. нями, перекрывающими диапазон изменения сигнала от 0 до + q,а группа п компараторов 8 - с уровнями в диапазоне от 0 до -g . Шкалы опорных уровней модулируются i выходными псевдослучайными напряжениями цифроаналогового преобразователя 3. Модуляция опорных уровней для группы компараторов 7 происходит прямым о выходным напряжением преобразователяЗ, которое меняется в пределах от 0 до + о; модуляция опорных уровней группы компараторов 8 происходит инверсным выходным напряжением преобразователя 3, ко- 15 торое меняется в пределах от О до - оо

Напряжение на выходе цифроаналогового преобразователя 3 г опорционально псевдослучайному числу Г, код которого с выхода генератора псевдослучайных чисел 14 20 подается на вход преобразователя 3, После каждого переключения генератора псевдослучайных чисел 14, на выходе каждого компаратора 7 и 8 появляется результат сравнения измеряемого сигнала с опор25 ным уровнем данного компаратора.

В каждом такте измерения для вычисления оценки средней мощности сигнала используется выходной сигнал только одного компаратора из каждой группы.Для выбора 30 этого сигнала выходы всех компараторов каждой группы подключены ко входам соответствующих коммутаторов 9 и 10. С прямого выхода коммутатора 9 и с инверсного выхода коммутатора 10 выходной сигнал одного компаратора каждой группы

7 и 8 через элемент ИЛИ 15 поступает на управляющий вход арифметического устройства 13, Для осуществления псевдослучайного считывания информации с компараторов 7 и 8 на управляющие входы коммутаторов

9 и 10 подается код псевдослучайного числа Г д от генератора псевдослучайных чисел 12, который тактируется частотой со второго выхода генератора гактовых импульсов 11. Этой же частотой стробируются все компараторы 7 и 8. В каждом такте измерения на арифметическое устройство 13 поступает код псевдослу50 чайного числа, соответствующего опорному уровню, с которым в данном такте сравнивается измеряемый сигнал. В свою очередь опорный уровень на втором входе компара55 торов 7 и 8 зависит от псевдослучайного числа и от места подключения компа-7! К ратора к резисторному делителю, т. е. от номера компаратора в каждой группе 7 и 8.

70 6

Номерам компараторов, которые в определенном такте измерения подключены к выходам коммутаторов 9 и 10, соответствует код на управляющем входе коммутаторов - псевдослучайное число к, Таким образом, код числа Г ц, который характеризует опорный уровень в данном такте измерения, составляется из кодов двух чисел E „, и Цд„. При атом число анимает старшие разряды в коде числа („„a чиспо Г „- младшие разряды того же кода.

Если на каком- го такте измерения на управляющий вход арифметического устройства 13 поступает логическая 1", арифметическое устройство суммирует псевдослучайное число - „, имеющееся на обоих информационных входах с уже накопленной суммой чисел Ц . После окончания всего цикла измерения состоящего из и тактов, арифметическое устройство 13 накопленную сумму умножает на постоянный коэффициент 2q и > извлекает квадратный корень и код оценки эффективного значения сигнала передает в регистрирующее устройство 16.

Частота тактирования генератора 14 псевдослучайных чисел выбирается в и раз меньше частоты тактирования генератора

12 псевдослучайных чисел и стробирования компараторов 7 и 8. Таким образом, удается максимально использовать быстродействие компараторов и тем самым значительно сократить время измерения прибора при использовании цифроаналогового преобразователя среднего быстродействия. Кроме того, в предлагаемом устройстве выходной сигнал цифроаналогового преобразователя изменяется только в пределах 1/rl от диапазона изменения +q измеряемого сигнала, атакже разрядность цифроаналогового преобразователя на число разрядов кода Ц меньше по сравнению с известным устройством, что способствует увеличению быстродействия самого цифроаналогового преобразователя. При использовании в предлагаемом измерителе по 8 компараторов в каждой группе и цифроаналогового преобразователя с временем установления порядка 1 мкс, при одинаковой с прототипом точности, время измерения данного прибора почти на порядок меньше, чем у прототипа. формула изобр ет ения цифровой измеритель действующего значения сигнала, содержащий входное

7 752170 8 устройство, выход юторого подключен к компаратора, вводы стробирования юмпапервым входам 2п компараторов, генера- раторов подключены ю второму выходу ге тор тактовых импульсов, первый выход ко- нератора тактовых импульсов, соединенному торого через первый генератор псевдослу- со входом генератора псевдослучайных чичайных ччсел подключен к цифроаналоговому сел, выход которого подключен ко второму ервому ин рмацион- информационному входу арифметического ному входу арифметического устройства, устройства и к управляющим входам обоих цоспедовательно соединенного с регистри- коммутаторов, информационные входы котоРующимустройством, о т л и ч а ющий- рых соединены с выходами компараторов, с я, тем, что, с целью повышениябыстткяей- io прямой выход первого юммутатора и инверствия измерителя в него введены два источни- сный выход второго подключены соответка тока, два делителя из l1 -1 последова- ственно к входам элемента ИЛИ, выход тельно соединенных резисторов в каждой, два которого соединен с управляющим входом коммутатора, второй генератор псевдослучай арифметического ст и ар метического устройства. ных чисел и элемент ИЛИ, при этом выход пер15

so î источника тока и прямой выход цифро- Источники информации, аналогового преобразователя а также выФ принятые во внимание при экспе изе ход второго источника тока и инверсный рт выход цифроаналогового преобразователя 1. Авторское свидетельство СССР подключены к соответствующим выводам l4 421011, кл. G 06 f 15/34,27.03.74. первого и второго делигелей один из выво- 2. Авторское свидетельство СССР дов каждого резистора обоих делителей сое- % 6000721, кл. Н.ОЗ К 13/02, динен со вторым входом соответствующего 13.08.77 (прототип).

ЦНИИПИ Заказ 4734/1 Тираж 1019 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4