Амплитудно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

с а%г" и тон:и т о п и с - Х-"й и E

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (и>7522 1 6

К АВТОРСКОМУ СВИДНЕДЬСТВУ (61) Дополнительное к авт, свид-ву— (22) Заявлено 210378 (21) 2595132/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 300780, Бюллетень ¹ 28 51)м К„з

0 05 8 1/01

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 8 21. 374. 33 (088. 8) Дата опубликования описания 30.07.80 (72) Автор изобретения

Г.И.Никитин (71) Заявитель

Институт высшей нервной деятельности и нейрофизиологии АН СССР (54) АМПЛИТУДНО-ФАЭОВ61Й ДИСКРИМИНАТОР

Изобретение относится к импульсной технике и может быть использовано для выделения электрических сигналов определенной амплитуды, конфигурации и начальной фазы из популяции (потока) электрических сигналов при исследовании и анализе импульсных потоков в нейрофизиологии, исследовании космических частиц, в физических экспериментах и др.

Известен амплитудный дискриминатор, содержащий блок амплитудночастотного преобразователя исследуе- 15 мого сигнала, компараторы верхнего и нижнего уровня, датчик опорного сигнала нижнего и верхнего уровня, бистабильный элемент, дифференцирующие цепочки, электронный 20 ключ, формирователь длительности (11 .

Однако этот дискриминатор выбирает импульсы, амплитуда которых лежит в пределах двух уровней (дискриминация "окном"), а на форму и началь-25 ную фазу он не реагирует, а ведь в потоке импульсов встречаются монофазные, двухфазные и импульсы более сложной формы с разными амплитудами и начальными фазами. 30

Цель изобретения — расширение функциональных возможностей дифференциального дискриминатора и возможность проведения селекции сигналов не только по амплитуде, но и по форме, .и по начальной фазе, а также — повышение надежности.

Для достижения указанной цели в амплитудно-фазовый дискриминатор, содержащий блок амплитудно-частотного .преобразования, исследуемого сиг-; нала, компараторы верхнего и нижнего уровня, датчики опорного сигнала нижнего и верхнего уровня, выходы которых подключены соответственно ко входам компараторов нижнего и верх,него уровня, бистабильный элемент, первый вход которого подключен через первую дифференцирующую цепочку с выходом компаратора нижнего уровня, соединенного выходом через вторую дифференцирующую цепочку с первым входом электронного ключа, второй вход — к выходу компаратора верхнего уровня, и выход — ко второму входу электронного ключа, выход которого подключен через формирователь длительности к третьему входу бистабильного элемента, введены дополнитель752216

15

50 бО ные бистабильный элемент и компараторы верхнего и нижнего уровня, третья дифференцирующая цепочка и два переключателя, при этом информационные входы компараторов верхнего и нижне- го уровня подключены соответственно через размыкающий и замыкающий контакты первого переключателя к пря мому и инверсному выходам блока амплитудно-частотного преобразования, а информационные входы дОполнительных комйараторов верхнего и нижнего уровня подключены соответственно через размыкающий и замыкающий контакты второго переключателя к инверсному и прямому выходу блока амплитудно-частотного преобразования, причем выход датчика опорного сигнала верхнего уровня соединен со входом дополнительного компаратора верхнего уровня, выход которого соединен с первым входом дополнительного 2 бистабильного элемента, а выход датчика опорного сигнала нижнего уровня соединен со входом дополнительного компаратора нижнего уровня, выход которого подключен через третью диффе- 2 ренцирующую цепочку ко второму входу дополнительного бистабильного элемента, выход которого соединен с третьим входом электронного ключа, а третий вход — с выходом Формирователя длительности.

В дискриминатор с целью повышения надежности введены четвертая и пятая. дифференцирующие цепочки и чувствительный релейный элеь нт, вход которого подключен к информационному входу компаратора нижнего уровня, а выход через четвертую и пятую дифференцирующие цепочки — соответственно к четвертым входам основного и дополнительного бистабильных элементов.

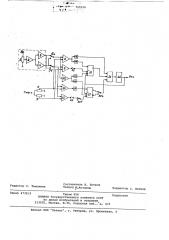

На чертеже представлена функциональная схема дискриминатора.

Устройство соцержит блок амплитудно-частотного преобразования, состоящий из аттенюатора 1 входного сигнала, перестраиваемый частбтноизбирательный усилитель 2,, неинвертирующий 3 и инвертирующий 4 усилители с единичным усилением, переключатель 5 выбора полярности входного сигнала, два датчика нижнего 6 и верхнего ? Уровней дискриминатора, четыре компаратора 8-11 и релейный усилитель 12, пять дифференцирующих цепочек 13-17, выделяющих передние и задние Фронты сигнала, два триггера 18 и 19,переключатель ?О выбора конфигурации исследуемого сигнала, электронный ключ 21, формирователь

22 выходного импульса . два выключателя блокнровок верхних (прямого.

23 и инвертирова> ного 24) уровней дискриминатора.

Устройство раб.та т следующим образом.

Входной сигнал, проходя аттенюатор 1, частотно-избирательный усилитель 2 и усилители 3 и 4, преобразуется по амплитуде и частоте в удобный для дальнейшего анализа сигнал. Выходы усилителей 3 и 4 разлив чаотся лишь полярностями выходных сигналов, а в остальном они идентичны. Переключателем 5 выбирается требуемая для анализа полярность исследуемого сигнала. Сигнал с переключателя 5 подается на компараторы

8-11, причем компараторы 8 и 9 работают с неинвертированным сигналом, а компараторы 10 и 11 — с инвертированным. На компараторы подаются и опорные сигналы, снимаемые с датчиков нижнего 6 и верхнего 7 уровней.

При достижении входным сигналом значений больше (равно) опорного на выходе компаратора формируется сигнал превышения заданного опорного уровня. Выходы компараторов 9 и 11верхних уровней подаются непосред твенно на входы бистабильных элементов .триггеров) 18 и 19, выходы же остальных — на дифференцирующие цепочки 13-17 для выделения передних и задних фронтов сигналов. Таким образом, на основе компараторов 8 и 9 организуется прямое, а на компараторах 10 и 11 инвертированные "окна" дискриминатора.

Два бистабильных элемента дискриминатора, триггеры 18 и 19 (каждый работает со своим "окном"), управляют электронным ключом 21, разрешая или запрещая прохождение импульса заднего фронта с компаратора 8 на выход дискриминатора. В зависимости от режима работы триггера 19 можно проводить анализ сигналов или с положительной начальной фазой или двуполярных с отрицательной начальной фазой.

При выборе первого режима работы входной сигнал начинается с положительной фазы, при достижении нижнего, уровня дискриминации происходит включение триггера 18 передним фронтом сигнала с компаратора 8. Если в дальнейшем сигнал, не достигнув верхнего .уровня дискриминации, начинает уменьшаться и становится меньше нижнего, компаратор 8 выдает импульс заднего фронта, который через открытый ключ

21 проходит на выход дискриминатора, он же производит и сброс обоих триггеров в исходное состояние. Если ам.плитуда сигнала превышает верхний уровень дискриминации, то сработавший компаратор 9 блокирует триггер

18 и тем самым блокируется выход дискриминатора.

Когда входной сигнал начинается с отрицательной полярности>то при до752216

Формула изобретения стижении им нижнего инвертированного уровня срабатывает компаратор 10 и передним фронтом своего сигнала включает триггер 19, который в этом режиме блокирует ключ 21 и, если теперь сигнал, инвертировав свою 5 полярность, вызывает срабатывание компаратора 8 и триггера 18, выход дискриминатора все равно оказывается заблокирован триггером 19.

При выборе режима анализа двуполяр1О ных сигналов исследуемый сигнал начинается с отрицательной полярности, и, достигнув нижнего инвертированного уровня, но не достигнув верхнего, включает : триггер 19, затем, сменив полярность, он таким же способом включает триггер 18, и уже после этого задний фронт сигнала компаратора 8 прсходит на выход дискриминатора.

Предусмотрена возможность блокировки как верхнего прямого 23, так и 20 верхнего инвертированного 24 уровней дискриминации, что также расширяет воэможности дискриминатора.

При каждой смене сигналом своей полярности элементом 12, аналогичным компаратору, генерируются импульсы переднего франта (для каждой полярности свой), KQTopblMH "абнуляются" триггеры 18 и 19, и тем самым, устройство более надежно подготавливается к приему и анализу следующего сигнала.

И, наконец, выходной импульс с электронного ключа 21 поступает на формирователь 22 длительности и мощ- 35 ности, а затем подается на выход дискриминатора.

Предлагемый амплитудно-фазовый дискриминатор позволяет проводить более тонкую селекцию сигналов и 4g повысить точность проводимых экспериментов .

1. Амплитудно-фазовый дискриминатор, содержащий блок амплитудно- частотного преобразования исследуемого сигнала, компаратары верхнего и нижнего уровня, датчики опорного сигнала нижнего и верхнего уровня, выходы которых подключены соответственно ко входам кампаратарав нижнего и верхнего уровня, бистабильный элемент, первый вход которого подключен через первую дифференцируащую цепочку с выходом компаратора нижнего уровня, соединенного выходом через вторую дифференцирующую цепочку с первым входом электронного ключа, второй вход — к выходу компаратора верхнего уровня, и выход — ко второму входу электронного ключа, выход которого подключен через формирователь длительности к третьему входу бистабильного элемента, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дополнительные бистабильный элемент и компараторы верхнего и нижнего уровня, третья дифференцирующая цепочка и два переключателя, при этом информационные входы компараторов верхнего и нижнего уровня подключены соответственно через размыкающий и замыкающий контакты первого переключателя к прямому и инверсному выходам блока амплитудно-частотного преобразования,а информационные входы дополнительных компараторов верхнего и нижнего уровня подключены соответственно через размыкающий и замыкающий контакты второго переключателя к инверсному и прямому выходу блока амплитудночастотного преобразования, причем выход датчика опорного сигнала верхнего уровня соединен со входом дополнительного компаратора верхнего уровня,выходом соединенного с первым входОм дополнительного бистабильнага элемента,а выход датчика опорного сигнала нижнего уровня соединен са входом дополнительного кампаратара нижнего уровня, выход которого подключен через третью дифференциальную цепочку ко второму входу дополнительного бистабильного элемента, выход которого соединен с третьим входам электронного ключа, .а третий вход — с выходом формирователя длительности.

2. Дискриминатор па п.1, о т л и ч а ю шийся тем, чта, с целью повышения надежности, в него введены четвертая и пятая дифференцирующие цепочки и чувствительный релейный элемент, вход которого подключен к информационному входу компаратора нижнего уровня, а выход через четвертую и пятую дифференцирующие цепочки — соответственно к четвертым входам основного и дополнительного бистабильных элементов.

Источники информации, принятые во внимание при экспертизе

1. EEG Clin. Neurophysiology, 1967, 23, 5, ч77-ч80. Spala L.T., Bodreau I.Ñ. "А sclid State differential amplitude discriminator for

single unit recording" (прототип).

Составитель В. Бугров

Техред И.Лсталош

Корректор C. Шекмар

Редактор С. Тимохина

Тираж 956

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Заказ 4739/3

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4