Компаратор абсолютных величин

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП-И САН И Е

ИЗОБРЕТЕНИЯ

<1т752217

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву з (22) Заявлено 170778 (21) 2646852/18-24 (51) М с присоединением заявки № (23) Приоритет

G 05 В 1/01

Государственный комитет

СССР ко делам изобретений и открытий

Опубликовано 300780. Бюллетень ¹ 28 (5Ç) УДК 621. 17 (088. 8) Дата опубликовани я описания 3 0,0 7.80 (72) Авторы изобретения

В.М. Беляков, E.Á. Елагин, P.Н. Югай и В.Л. Буденный

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (7i) Заявитель (54)КОМПАРАТОР АБСОЛЮТНЫХ ВЕЛИЧИН

Изобретение относится к электронной аналоговой вычислительной технике и предназначено для сравнения абсолютных.величин двух электрических сигналов, заданных в виде тока или напряжения, и выдачи на одном выходе сигнала о результате сравнения.

Известны компараторы, выполненные на дифференциальном операционном 10 усилителе, охваченном положительной обратной связью (1) .

Недостаток известных компараторов состоит в том, что они сравнительно громоздки. 15

Наиболее близким по технической сущности к предлагаемому является гистереэисный компаратор на дифференциальном операционном усилителе, охваченном положительной обратной 20 связью, осуществляющий сравнение двух электрических сигналов, заданных в виде тока или напряжения на немнвертирующем входах усилителя и обладающий скачкообразным изменением вы- 25 ходного сигнала при увеличении разности входных сигналов до значения, большего порогового (21 .

Такие компараторы имеют два порога переключения, различающиеся на 30 ширину петли гистерезиса, и осуществляют сравнение сигналов лишь при опрецеленном сочетании их знаков,зависящем or расположения петли гистерезиса к оси входных сигналов.

Недостаток таких компараторов заключается в их относительной сложности, поскольку при выделении абсолютных значений сигналов требуется дополнительный дифференцйальный операционный усилитель.

Цель изобретения — упрощение устройства.

Для достижения цели в компаратор абсолютных величин, содержащий дифференциальный операционный усилитель, инвертирующий и неинвертирующий входы которого соединены с входами компаратора соответственно через первые и вторые последовательно соединенные входной масштабный резистор и разделительный диод, неинвертирующий вход дифференциального операционного усилителя через первый масштабный резистор обратной связи соединен с шиной нулевого потенциала и через второй масштабный резистор обратной связи — с выходом дифференциального операционного усилителя, третий мас752217

5 (О

20

60 штабный резистор обратной снязи включен между иннертирующим входом дифференциального операционного усилителя и шиной нулевого потенциала, ннедены третий и четвертый разделительные диоды, причем общий вывод первых входного масштабного резистора и разделительного диода через третий разделительный диод соединен с инвертирующим входом дифференциального операционного усилителя„ а общий нынад вторых входного. масштабного резистора и разделительного диода через четвертый разделительный диод подключен к неинвертирующему входу дифференциального операционного усилителя.

Такое включение диодов обеспечивает скачкообразное изменение выходного напряжения при достижении разностью абсолютных значений двух входных сигналон величины большей половины ширины петли гистереэиса.

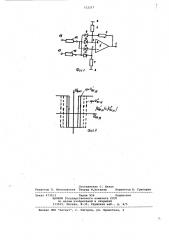

На фиг. 1 приведена принципиальная схема гистерезисного компаратора абсолютных величин, на фиг. 2 — статическая характеристика компаратора, построенная как зависимость выходного напряжения от входного сигнала по первому входу.

Двухвходоной гистерезисный компаратор абсолютных неличин содержит дифференциальный операционный усилитель {Оу) 1 с неиннертирующим входом

2, инвертирующим входом 3 и выходом

4. Масштабный резистор 5 обратной связи включен между выходом 4 и входом 2 ОУ, масштабные резисторы б и 7 обратной связи включены соответственно.между входами 2 и 3 ОУ и шиной 8 нулевого потенциала. Разделительные диоды 9-12 включены в кольцевую схему так, что анод диода 9 и катод диода 12 соединен со входом 2 ОУ, а анод диода 11 и катод диода 10 соединены с входом 3 ОУ, причем между общим выводом разделительных диодов

11 и 12 и входной клеммой 13 включен входной масштабный резистор 14, а между общим выводом разделительных диодов 9 и 10 и нходной клеммой 15 входной масштабный резистор 16.

Устройство работает следующим образом.

Предположим, что сигнал на входе

13 имеет положительную полярность и меньшую абсолютную неличину, чем сигнал отрицательной полярности на входе 15 компаратора. При этом диоды

9 и 12 открыты, а диоды 10 и 11.— закрыты. Если разность абсолютных значений напряжений на входах больше полонины ширины петли гистерезиса компаратора, то на его выходе — напряжение отрицательной полярности.

Ф

Если сигнал на входе 13 при положительной полярности больше по абсолютной величине сигнала на входе 15 при отрицательной его полярности на величину, превышающую половину петли гистереэиса компаратора, то при этом диоды 9 и 12 открыты, диоды

10 и 11 закрыты, а сигнал на выходе компаратора имеет положительную полярность.

Таким образом, эа счет применения укаэанного нключения диодов достигается расширение функциональных воэможностей гистереэисных компараторов описанного типа при упрощении схемного решения задачи выделения абсолютного значения величины входных сигналов.

Формула изобретения

Компаратор абсолютных величин,содержащий дифференциальный операционный усилитель, иннертирующий и неиннертирующий входы которого соединены с входами компаратора соответственно через первые и вторые последовательно соединенные входной масштабный резистор и разделительный диод, неиннертирующий вход дифференциального операционного усилителя через первый масштабный резистор обратной связи соединен с шиной нулевого потенциала и через второй масштабный резистор обратной связи — с выходом дифференциального операционного усилителя, третий масштабный резистор обратной связи включен между иннертирующим входом дифференциального операционного усилителя и шиной нулевого потенциала, о т л и ч а ю шийся тем, что, с целью упрощения устройства, в него введены третий и четвертый разделительные диоды, причем общий нынад первых входного масштабного резистора и разделительного диода через третий разделительный диод соединен с инвертирующим входом дифференциального операционного усилителя, а общий вывод вторых входного масштабного резистора и разделительного диода через четвертый разделительный диод подключен к неиннертирующему входу дифференциального операционного усилителя.

Источники информации, принятые во внимание при экспертизе

1. Сlayton G.8, Voltage совраra"

tors and multivibrators, "Wireless

Чог10", 1969, и 1406.

2. Авторское свидетельство СССР

Р 329505, кл. G 05 В 1/01, 1970 (прототип)„

752217

Составитель С. Белан

Редактор Л. Веселовская Техред И,йсталош Корректор Н. Григорук

Закаэ 4739/3 Тираж 956 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4