Устройство для сопряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()?52321 (61) Дополнительное к авт, свид-ву

{22) Заявлено28.07.78 (2() 2651507/18-24

Э (5l)M. Кл.

G 06 F 3/04 с присоединением заявки ¹

Гасударственный камитет (23) Приоритет

Опубликовано 30.07.80. Бюллетень №28

Ito делам изобретений и открытий (53) УДК 681,327..7(088.8) Дата опубликования описания 02.08.80 (72) Авторы изобретения

А. Ю. Борисова, В, И. Коньков и Г. А. Садовский

Рязанский радиотехнический институт (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может найти применение в автоматизированных системах управления в качестве буферного устройства памяти.

Известны устройства для сопряжения, 5 содержащие регистры, элементы И, элементы ИЛИ, распределители ввода и вывода информации, схемы сравнения, сумматор и узел управления и выполняющие функции буферизации входящих кодов $1(.

Недостаток этих устройств обусловлен их сложной структурой и большим объемом оборудования.

Наиболее близким к предлагаемому по 15 сущности технического решения является устройство для сопряжения, содержащее матрицу элементов памяти, счетчик записи и счетчик считывания, элемент И и элементы ИЛИ, реверсивный счетчик, ком-2о мутаторы и дешифратор, причем выходы элементов памяти j -ой строки материалы подключены к соответствующим входам

j -го элемента ИЛИ, выход которого

2 соединен -тым информационным вы. ходом устройства, первые входы элементов памяти -ой строки матрицы являются -тым информационным входом устройства, второй, третий и четвертый входы элементов памяти -oO строки матрицы подключены соответственно к тым выходам первой и второй групп дешифратора и выходу ) -т о хоммутато ра, первый и второй входы которых подключены соответственно к первым выходам счетчика записи и счетчика считывания, вторые выходы которых подключены соответственно ко входам реверсивного счетчика, а входы -являются соответст» венно управляющими входами записи и считывания, выходы реверсивного счетчика соединены с соответствующими входами дешифратора, выходы первой группы которого соединены с соответствующими входами элемента И, выход которого является управляющим входом записи устройства, выходы второй группы дешифратора подключены к соответствующим вхо»

3 дам выходного элемента ИЛИ, выход которого является управляющим входом счи. тывания устройства(= i,M, j - 3 Ц) (2), Недостаток этого устройства состоит в больших затратах оборудования.

Бель изобретения - снижение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство содержащее группу элементов ИЛИ, группу элементов памяти, информационные входы которых являются соответствующими информационными входами устройства, счетчики записи и считывания, входы которых являются соответственно управляющими входами записи и считывания устройства, реверсивный счетчик, соединенный выходом со входом дешифратора нуля, введены триггер, два элемента задержки и три группы элементов И, причем вход счетчика считывания соединен с первым входом реверсивного счетчика и через первый элемент задержки с управляющими входами элементов И первой группы, информационные входы которых соединены с выходами соответствующих элементов памяти группы, а выходы являются соответствующими информационными выходами устройства, вход счет» чика записи подключен ко второму входу реверсивного счетчика и через второй 30 элемент задержки к управляющим входам записи элементов памяти группы, адресные входы которых соединены с выходами элементов ИЛИ группы, выходы счетчика записи подключены к информационным 55 входам соответствующих элементов И второй группы, управляющие входы которых соединены с нулевым выходом триггера, а выходы - с первыми входами соответствующих элементов ИЛИ группы, выходы счетчика считывания соединены с информационными входами соответствующих элементов И третьей группы, первый и второй управляющие входы которых подключены соответственно к выходу дешифратора ну- 45 ля и единичному выходу триггера, соединенного соответственно нулевым и единичным входами с входами счетчика записи и счетчика считывания.

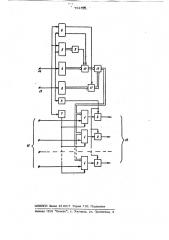

На чертеже представлена блок-схема устройства.

Устройство содержит элементы 1 памяти группы, элементы 2 И первой группы, первый элемент 3 задержки, счетчик

4 считывания, реверсивный счетчик 5, триггер 6, второй элемент 7 задержки, счетчик 8 записи, дешифратор 9 нуля, элементы 10 И третьей группы, элементы 11

21 4

И второй группы, элементы 12 ИЛИ группы, управляющие входы 13 записи и 14 считывания устройства, информационные входы 15 и выходы 16 устройства.

Устройство работает следующим образом.

В исходном состоянии элементы 1 памяти, счетчики 8 и 4, реверсивный счетчик 5 обнулены, триггер 6 находится в произвольном состоянии, на всех адресных входа х элементов 1 памяти на ходится потенциал, соответствующий "О", на выходе дешифратора 9 находится запирающий потенциал.

При поступлении в произвольный момент времени на вход 15 параллельного кода, на вход 13 приходит сигнал, который записывает единицу в счетчик 8 и в реверсивный счетчик 5, устанавливает триггер 6 в нулевое положение и через элемент 7 задержки разрешает запись информации в элементы 1 памяти. Код адреса, по которому происходит запись, подается на элементы 1 памяти с выхода счетчика 8 через элементы 11 И, открытые потенциалом с триггера 6, и элементы 12 ИЛИ.

При поступлении следующего кода на вход 15 и сигнала на вход 13 в реверсивный счетчик 5 и счетчик 8 записывается еще по единице, и на входе адреса элементов 1 памяти выставляется соответствующий адрес, по которому в них записывается код со входа 15. Аналогичным образом происходит дальнейшее заполнение элементов памяти.

При подаче на вход 14 первого сигнала Считывание" триггер 6 устанавливается в единичное состояние из содержимого реверсивного счетчика 5 вычитается единица, в счетчик 4 записывается единица и выходной сигнал элемента 3 задержки разрешает считывание информации. и выдачу кода на выход 16, причем код первого адреса, по которому происходит считывание, подается с выхода счетчика

4 через элементы 10 И, открытые потенциалом с единичного выхода триггера

6, и элементы 12 ИЛИ. При поступлении следующего считывающего сигнала из содержимого реверсивного счетчика 5 вычитается еще единица, в счетчик 4 записывается единица и на входах адреса элементов 1 памяти выставляется код второго адреса. Значение информации, записанной по этому адресу, снова считывается и через открытые элементы И выдается на выход 16.

5 75

Принципиально считывание и запись информации может производиться в любом порядке важно лишь, чтобы момент считывания не совпадал по времени с моментом записи. Это можно осуществить, например,. путем формирования импульсов

"Запись и "Считывание из переднего и заднего фронтов сигналов опорной частоты.

При считывании всей информации из элементов памяти содержимое реверсивного счетчика становится равным нулю, вследствие чего дешифратор 9 нуля формирует сигнал, блокирующий элементы

10 И. После записи хотя бы одного кода блокировка снимается и разрешается дальнейшее считывание.

Таким образом, устройство имеет более простую конструкцию и обеспечивает запись и вывод информации.

Формула изобретения

Устройство для сопряжения, содержащее группу элементов ИЛИ, группу элементов памяти, информационные входы которых являются соответствующими информационными входами устройства, счет« чики записи и считывания, входы которых являются соответственно управляющими входами записи и считывания устройства, реверсивный счетчик, соединенный выходом со входом дешифратора нуля, о т « личающееся тем, что, сцелью снижения аппаратурных затрат, в устройство введены триггер, два элемента за-. дежки и три группы элементов И, причем

2321 вход счетчика считывания соединен с первым входом реверсивного счетчика и через первый элемент задержки с управляющими входами элементов И первой группы, информационные входы которых соединены с выходами соответствующих элементов памяти группы, а выходы являются соответствующими информационными выходами устройства, вход счетчика записи подключен ко второму входу реверсивного счетчика и через второй элемент задержки к управляющим входам записи элементов памяти группы, адресные входы которых соединены а выходами элементов ИЛИ группы, выходы счетчика записи подключены к информационным входам соогветствующих элементов И второй группы,управляющие входы которых соединены с нулевым выходом триргера, а выходы— с первыми входами соответствующих элементов ИЛИ группы, выходы счетчика считывания соединены с информационными входами соответствующих элементов И третьей группы, первый и второй управляд5 ющие входы которых подключены соответ ственно к выходу дешифратора нуля и единичному выходу триггера, соединенного соответственно нулевым и единичным входами с входами счетчика записи и счетчика считывания.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке М 2166167/18-24, 3 кл. 6 06 Р 3/04, 1975, 35

2. „Авторское свидетельство СССР по заявке М 2561920/18-24, кл. С 06 Г 3/04, 1977 (прототип).