Преобразователь двоично-десятичной дроби в двоичную дробь

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

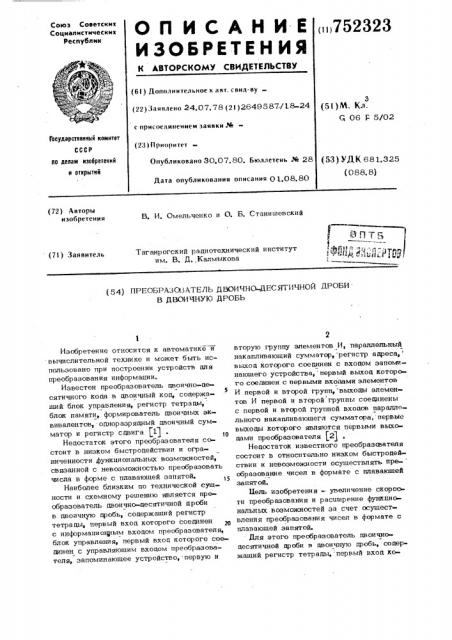

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<»>752323

Ф«

« (61) Дополнительное к авт. свнд-ву— (22) Заявлено 24.07.78 (2I ) 2649587/18-24

3 (5т)М. Кл. 06 ).= 5/02 с присоединением заявки,%

Государственный комитет (23) Приоритет пп делам изооретений и открытий

Опубликовано 30,07.80. Бюллетень ¹ 28

Дата опубликования описания 01.08.80 (53) УДК 681.325 (088. 8) (72) Авторы изобретения

В. И. Омельченко и О. Б, Станишевский

Таганрогский радиотехнический институт им. В. Д..Калмыкова (7! ) Заявитель (54) ПРЕОЬРАЗО!ЗАТЕЛЬ ДИОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ

В ДВОИЧНУЮ ДРОБЬ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для преобразования информации.

Известен преобразователь двоично-цесятичного кода в цвоичный коп, содержа5 ший блок управления, регистр тетрацы, блок памяти, формирователь пвоичных эквивалентов, опноразрядный двоичный сумматор и регистр спвига 11 .

1О

Недостаток этого преобразователя состоит в низком быстродействии и ограниченности функциональных возможностей, связанной с невозможностью преобразовать числа в форме с плаваюшей запятой.

Наиболее близким по технической сущности и схемному решению является преобразователь двоично-десятичной дроби в двоичную пробь, сопержаший регистр тетрады, первый вход которого соединен с информациощтым вхоцом преобразователя, блок управления, первый вхоц которого соединен с управляюшим вхоцом преобразователя, запоминаюшее устройство, первую и вторую группу элементов И, параллельный накапливаюший сумматор, регистр адреса, выход которого соединен с входом запоминаюшего устройства, первый выхоц которого соединен с первыми входами элементов

И первой и второй групп, выходы элементов И первой и второй группы соединены с первой и второй группой входов параллельного накапливаюшегл сумматора, первые выходы которого являются первыми выходами преобразователя )2)

Нецостаток известного преобразсвателя состоит в относительно низком быстродействии и невозможности осуществлять пре- образование чисел в формате с плаваюшей запятой.

Цель изобретения - увеличение скорости преобразования и расширение функциональных воэможностей за счет осушествления преобразования чисел в формате с плавающей запятой.

Для этого преобразователь двоичнодесятичной дроби в двоичную дробь, содержаший регистр тетрадьт, первый вход ко2323 4

Регистр 6

Тип передачи

0

ПК

3 75 торого соецинен с информационным вхоцом преобразователя, блок управления, первый вхоц которого соединен с управляющим входом преобразователя, запоминающее устройство, первую и вторую группу элементов И, параллельный накапливающий сумматор, регистр адреса, выход которо. го соединен с входом запоминающего уст ройства, первый выход которого соединен с первыми вхоцами элементов И первой и второй группы, выходы элементов И первой и второй группы соепинены с пер вой и второй группой входов параллельного накапливающего сумматора, первые выходы которого являются первыми выхс дами преобразователя, выход блока управления соединен с первым входом регистра appeca, дополнительно содержит регистр старших разрядов, распределитель импуль сов, регистр поряцков, третью группу элементов И, коммутатор порядков, первый и второй входы которого соединены соответственно с входами. порядка и знака порядка преобразователя, а первый и второй его выходы соединены соответственно с вто,зыми вхоцами регистра адреса и блока управления, выход регистра старших разрядов соецинен с вторым вхоцом регистра тетрацы, выхоц которого подключен к первому входу распределителя импульсов, второй вхоц которого соединен с выхопом запуска блока управления, первый выход ра. спределителя импульсов соединен с третьим входом, регистра тетрады и первым вхоцом регистра старших раэряцов, второй вход которого соединен со вторым выходом параллельного нак апливаюшего сумматора и четвертым вхоцом регистра тетрацы, второй и третий выходы распре-. пелителя импульсов соединены соответственно с третьим вхоцом параллельного накапливающего сумматора, с вторым вхоцом элементов И первой и второй группы и с первыми входами элементов И третьей группы, вторые входы которых соединены с первым выходом запоминающего устройства, второй выхоп которого через регистр порядка соединен со вторыми выходами преобразователя, выхоць элементов

I .И третьей группы соединены с четвер ьтм вхопом параллельного накапливающего сумматораа.

На чертеже представлена структурная схема предлагаемого преобразователя, соцержашая информационный вход 1, вход 2 знака порядка, вход 3 поряпка, управляющий вход 4, регистр 5 старших раэряцов, регистр 6 тетрацы,коммутатор 7 поряцка, блок 8 управления, регистр 9 апреса, распрецелитель 10 импульсов, запоминающее устройство 11, регистр 12 порядка, вторые выходы 13, первая, вторая, третья группы 1 4, 1 5и1 6 элементов параллельный накапливающий сумматор

17, первые выходы 18, Информационный вход 1 служит цля записи тетрац преобразуемой дроби. Вход

2 знака порядка необходим пля подачи зчака порядка. Бхоц 3 порядка предназначен цля занесения порядка. Управляющий вхоц

4 служит цля подачи синхроимпульса. Регистр 5 старших раэряпов предназначен цля хранения старших разрядов с

-(n -4

2 -2 множителя при умножении на константу умножения.

Регистр 6 тетрацы необходим цля хранения либо очерецной тетрацы преобразуемой цвоично-десятичной дроби либо младших разрядов множителя с 2 " ® по 2 ".

Коммутатор 7 порядков служит пля устаI новки адреса константы умножения и подачи управляющего сигнала в блок 8 управления, обеспечивающего работу всего устройства в целом. Регистр 9 адреса хранит либо адрес цвоичного эквивалента преобразуемой тетрапы, либо адрес константы умножения. Распределитель 10 импульсов вырабатывает сигналы, необходимые цля управления группами элементов 14-16 И, параллельным накапливающим сумматором 17, регистром 5 стар« ших разрядов и регистром 6 тетрацы.

Умножение производится на пва разряда множителя (начиная с младших разрядов).

Все передачи, которые производятся в зависимости от состояния анализируемой пары разрядов, представлены в табл.l.

Табл ица 1

752323

Продолжение табл. 1

Тиц передачи

0 1

2р

Пп

1р

Л1

0

Л1

<=x

+K. Ь Ъ 2 (10 ) В первом столбце таблицы указываются возможные состояния анализируемой пары разряцов. Второй столбец соцержит перенос Пп от предыдушей анализируемой BBpbL Третий столбец указывает тип передачи через группы элементов И

14-16 ПК вЂ” прямой код, Л1 — передача прямым копом со сдвигом на одну позицию в сторону старших разрядов. Информация четвертого столбца указывает на возможный перенос П и+1 в следуюшую пару разрядов множителя в зависимости от состояния разряцов анализируемой пары разрядов множителя.

Код 11 можно представить как единицу более старшего разряда и отрицательную единицу в первом разряде. Поэтому при коде 11 следует вычесть множимое из суммы частичных произведений, n0Tlyченный результат в сумматоре 17 сдвинуть на два разряда в сторону старших разрядов запомнить, что в слецуюшей паре разрядов нужно учесть дополнительную единицу, что и указано в четвертой, седьмой и восьмой строке четвертого столбца.

Запоминаюшее устройство 11 хранит

К двоичных эквивалентов и 2р + 1 констант умножения и двоичных порядков.

Регистр 12 порядка необходим для хранения двоичного порядка искомой мантиссы. Вторые выходы 13 обеспечивают съем двоичного порядка. Первая, вторая, третья группы элементов 14,15,16 И передают поступившую на вход информацию прямым кодом, прямым кодом со сдвигом влево на один разряд, дополнительным коцом соответственно. Параллельный накапливаюший сумматор 17 служит для сложения и хранения двоичной информации. Первые выхоцы 18 необходимы для съема преобразованной

10 мантиссы

Любое число У2 „в двоично-десятичной системе счисления можно представить в формате с плаваюшей запятой как

+p

4* ц., = т„ о =5 где Т; — тетр аца двоично-десятичного числа;

3o K — число разрядов двоично-десятичной дроби;1

-4

10 — двоичные эквиваленты млад-. ших разрядов преобразуемых тетрад.

Первое выражение в двоичной системе счисления имеет виц

+Щ 2 9(Z

)ф дробивши

K2 — константа умножениц

m - двоичный порядок.

Учитывая, что тетрада цвоично-деся45 тичного числа имеет вид Т =Ъ Я».

<2 <1 где Ь - разряды тетрацы нуль или ° единица, а запоминающее устройство 11 хранит эквиваленты младших двоичных разрядов тетрад, сдвинутые на цве позиции a сторону старших разрядов, то двоичную дробь (Ц 2 0 )2 можно представить так

i-x (9,-(О)2 Е,2 Ь,.2Ъ;, 2 (iO 2+

7 75232

Учитывая, чтоЬ,„Ь; 2 (!О } и Ь g, г ()О- ) есть соответственно функции Г„и г; умножения соответствующих пар разрядов тетрады, на двоичный эквивалент, то второе выражение можно представить в виде m 92- о) 2

Из этого следует, что процесс преобразования двоично-десятичной дроби складывается из двух этапов — преобразования мантиссы исходной дроби и умножения 1S полученной двоичной мантиссы на константу умножения К с присвоением произведения соответствующего порядка.

Этот алгоритм реализуется в предлагаемом преобрпзователе в следующей пос- 20 ле дов ательн ости.

С информационного входа 1 поочередно, поступают тетрады преобразуемого числа, начиная с младшей (старшей). Одновременно в блок 8 управления поступает по уп- 25 равляющему входу 4 сигнал, запускающий все устройство в целом. Блок 8 управления вырабатывает сигналы, необходимые для функционирования всего устройства. ЗО

Синхронно с поступившей тетрадой в регистре 9 адреса устанавливается адрес необходимого двоичного эквивалента, поступающего из запоминающего устройства

11. Допустим, что преобразуется тетра- да двоично-десятичного числа% . Тог-да параллельный накапливающий сумматор

17 хранит результат преобразования младших тетрад. В первом такте на регистр 6 тертады поступает тетрада Т, . Парал- 46 лельный накапливающий сумматор 17 производит сдвиг на две позиции в сторону старших разрядов хранящейся в нем информации. Из запоминающего устройства

3.

11 поступает двоичный эквивалент вида

2 (10 )

Во втором такте распределитель 10 импульсов анализирует состояние первого и второго разряда регистра 6 тетрады и вырабатывает сигналы, управляющие иере. дачей выбранного двоичного эквивалента из запоминающего устройства 11. Сумматор 17 складывает результат сдвига с первым частичным произведением Р,, < - 1

В третьем такте производится сдвиг на две позиции в сторону младших разрядов содержимых регистра тетрады 6 и параллельного накапливающего сумматора 17.

В четвертом такте производится анализ третьего и четвертого разрядов тетрады, а из запоминающего устройства 11 в соответствующем коде поступает двоичный эквивалент 2 ° (10 ) на первую, вторую, третью группу элементов 14-16

И. Параллельный накаплившощий сумматор

17 складывает второе частичное произвеление Р ; 1 с результагом сдвига, по лученным в предыдущем такте. На этом один цикл преобразования заканчивается, После произведенных двух умножений на два разряда, поступает следующая тетрада и осуществляется следующий цикл умножения ее на выбранный двоичный эквивалент из запоминающего устройства

11. Процесс преобразования мантиссы преобразуемой дроби производится К раз, в результате чего на параллельном накапливающем сумматоре 17 хранится преобразованная дробь.

В табл. 2 представлено преобразование двоично-десятичной дроби 0,987654. Первый столбец указывает номер цикла, второй столбец — вид операции, третий сголбец содержит два знаковых и двадцать один числовой разряды сумматора 17.

Каждый цикл представлен шестью строками.

752323

10 лица 2

Разряцы

Вид операции

Л2,00000000000 0 0 О 0 О 0

Р 00000000000 О О 0 О 0 0

М

НИХ ла

Пр2

Ф

Ь2

Л2

Ф

Пр2

БО

Л2 .

Ф

Д

Пр2

Л2

Пр2 Э

Л2

Пр2

1 2, 1 2 3 4 5 6 7 8 9 10 11 12,13 14 1

00000000000 О О О О О О

OOOOOOOOOOO О 0 О О О 0

00000000000 О О О О О О

00000000000 О О О О О О

00000000000 О О 0 О О О

00000000000 О О О О О 1

0OOOOOOOOO0 0 О О О О

00000000000 О О 0 О О

00000000000 О 0 0 О О

00000000000 О 0 О О О

00000000000 0 0 О 1 1

O OOOOOuOOOO О 1 1 О 1

00000000000 1 О О О О

00000000000 О О 1 О О

00000000000 О О 1 1 О

OOOOOOOO 000 О 1 О 1 О

00000000 001 О 1 О i О

1 1 1 1 1 1 1 1 1 О 1 1 j. 1 1 О

1111111111101001

1 1 1 1 1 1 1 1 1 1 1 1 1 О 1 О

000000001 О О О О О 1 1

0OO OOOO 0011 1 1 1 O

0000000 1 1 1 1 1 О 1 О 1

00000000 О О О О О О О О

0000000111 1 i О 1 О 1

0000000001 1 1 1 1 О 1

00000 1 01О0011110

00000101100111000

752323

Разряды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 1

10110011100000101

110011001 1 О 0 1 1 Q 0 1

1100000000 1 О 0 1 1 1 1 1

011000000-0 0 1 0 0 1 1 1

100110011 0 0 1 1 0 0 1 1

111110011 0 1 0 1 1 0 1 0

Таблица 3

Константа умножения Кр

Кр8

Кр10

00,9999999990,7777777777

0,5000000000

0,625

2 0,781 2 5, О, 6 1 7 7 7 7 77 7 7

0,7637777777

30,9765625

В первой строке представлено содержимое сумматора 19, сдвинутое на две позиции в сторону старших разрядов. Эта операция обозначена во втором столбце как Л2. Во второй строке представлено первое частичное произведение младших разрядов F (< s -той тетрады на соответствующий двоичный эквивалент 2 (10 ),. Третья строка указывает результат суммирования двух предыдуших строк.. В четвертой строке результат суммирования сдвинут вправо на две позиции в сторону младших разрядов Пр2. В пятой строке представлен результат умножения двух старших разрядов тетрады на соответствующий двоичный эквивалент

2 (10 " ) . Эта операция обозначена во втором столбце как F4 . Шестая строка есть результат суммирования четвертой и пятой строк.

После этого в коммутатор 7 порядков поступают знак и десятичный порядок, по которым в регистре 9 адреса устанавливается адрес соответствующей константы

Продолжение табл. 2

l умножения К и производится пуск рас

?0 пределителя 10 импульсов.

Одновременно производится передача двоичных величин (g < ) в регистр

6 тетрады и регистр 5 старших разрядов, а из запоминающего устройства 11 выбирается константа Kg умножения и двоич- ный порядок, поступающий на регистр порядка 12, Затем производится умножение величины (Ч ) на константу ум.ножения К, Умножение ничем не отличается от умножений при преобразовании мантисс двоично-десятичной дроби. После

П /2 умножений результат произведения хранится на параллельном накапливающем сумматоре 17.

М Окончательный результат снимается с параллельного двоичного сумматора 17 с помощью вторых BbIxoAoB 18, а двичный порядок считывания с регистра 12 порядка и поступает на первые выходы 13.

40 Константы умножения К и двоичные порядки N представлены в табл. 3. В первом столбце указывается десятичный порядок Р с соответствующим знаком.

7 52323

14

Продолжение табл. Э онстанта умн

035 1 56

293945

367431

604644

132257

Кр10

9 2

4288

388608

7 10886

368700

Во втором столбце представлена константа .умножения в десятичном коде

Кр10 и в восьмеричном коде, В третьем

45 помещен двоичный порядок m в восьмеричной системе счи ления, Для выявления техник -экономического эффекта сравним оба устройства по быстродействию, для чего рассмотрим временные диаграммы предлагаемого устройства и преобразователя.

Алгоритм. преобразования в предложенном устройстве состоит из четырех тактов, повторяемых (К вЂ” 1) раз,-тогда как преобразователь требует пяти тактов, также повторенных (К-1) раз, Следовательно, имеет место увеличение скорости преобразованим в 1,25 раза.

Это повышение быстродействия особенно важно при работе машины в режиме разделения времени.

Преобразование двоично-десятичной дроби в двоичную дробь в формате с плавающей запятой позволяет значительно расширить диапазон представления чисел.

Формула из обретения

Преобразователь двоично-десятичной дроби в двоичную дробь, содержащий регистр тетрады, первый вход которого соедини с информационным входом преобразователя, блок управления, первый вход которого соединен с управляющим входом

15 7523 преобразовагеля, запоминающее устройство, первую и вторую группу элементов И, параллельный накапливающий сумматор, регистр адреса, выход которого соединен с входом запоминающего устройства, первый выход которого соединен с первыми входами элементов И первой и второй групп, выходы элементов И которых соединены соответственно с первой и второй группой входов параллельного накапливающего сумматора, первые выходы которого являются первыми выходами преобразователя, выход блока управления соединен с первым входом регистра адреса, отличающийся тем, что, с целью повышения скорости преобразования и расширения функциональных возможностей, заключающихся в преобразовании дробей в форме с плавающей запятой, он содержит регистр старших разрядов, распределитель импульсов, регистр порядков, третью группу элементов И, коммутатор по pBllKoB) первый и второй входы которого со аинены соответственно с входами порядка и знака порядка преобразователя, а д первый и в1орой его выходы соединены со ответственно со вторыми входами регистра адреса и блока управления, выход регистра старших разрядов соединен со вторым входом регистра тетрады, выход которого подключен к первому входу распределителя импульсов, второй вход которого соединен с выходом запуска блока управления, первый выход распределителя импульсов соединен с третьим входом регистра тетрады и первым входом регистра старших разрядов второй вход которого соединен со вторым выходом параллельного накапливающего сумматора и четвертым входом регистра тетрады, второй и третий выходы распределителя импульсов соединены соответственно с третьим входом параллельного накапливающего сумматора, со вторыми Йодами элементов И первой г и второй групп и с первыми входами элементов И третьей группы, вторые входы которых соединены с первым выходом запоминающего устройства, второй выход которого через регистр порядка соединен со вторыми выходами преобразователя, выходы элементов И третьей группы соединены с четвертым входом параллельного накапливающего сумматора.

Источи ики информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Мо 473179,кл, С 06 F 5/02, 1974.

2. Авторское свидетельство СССР

No. 572781, кл, G 06 F 5/02, 1975

ИИ11И Заказ 4746/7 раж 751 Подписное лиал ПГ1П Патент, r. Ужгород, ул. Проектная, 4