Устройство для преобразования последовательного двоичного кода в десятичный код

Иллюстрации

Показать всеРеферат

(iii 752324

И Е

N3QSPE7

Союз Советскмх

Соцмалкстмческкх

Реслублмк

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт. свид-ву Ке 622076 (22)Заявлено 19 06.78 (2I) 2655599/18-24 (51) М. Кл.

Cj 06 F 5/02 с присоединением заявки Ж—

ГооударстввнныИ комитет

СССР (23) Приоритет

l30 делам изобретений к открытий

Опубликовано 30.07.80. Бк ллетень ¹ 28

Дата опубликования описания 01 08.80 (Бд) уду 681.325 (088.8) (72) Авторы изобретения

А. 3. Подколзин, Н. A. Подколзина и Г. А, Венедиктова (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПОСЛЕДОВАТЕЛЬНСГО ДВОИЧНОГО КОДА В

ДЕСЯТИЧНЫЙ KOL1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для преобразования информации.

Ф

По основному авт. св. % 622076 известно устройство для преобразования последовательного двоичного кода в десятичный код, содержащее коммутатор, генера -. тор последовательностей импульсов, блок шифраторов, двоично-десятичный счетчик

t0 и элемент ИЛИ., Недостатком этого устройства является ограниченность функциональных возможностей, связанная с невозможностью преобразования двоичного кода в процентную форму.

Бель изобретения — расширение функциональных возможностей, заключающееся в преобразовании двоичного кода в процентную форму.

Бель достигается за счет того, что устройство для преобразования последовательного двоичного кода в десятичный код содержит коммутатор, генератор последовательностей импульсов, блок шифраторов, двоично-десятичный счетчик, причем выходы коммутатора соединены со входами шифратора и элемента ИЛИ, выход которого соединен со входом генератора последовательностей импульсов, выходы блока шифраторов соединены со BxollBMH двоично-десятичного счетчика, выходы генератора последовательностей импульсов соединены с тактовыми входами блока шифраторов и в него введена группа дополнительных элементов ИЛИ и блок шифраторов эквивалентов в процентной форме, входы которого соединены с соответствующими выходами входного коммутатора, а выходы через группу дополнительных элементов ИЛИ соединены с входами двоично десятиАного накопительного счетчика, вы.ходы генератора последовательностей импульсов соединены с тактовыми входами блока шифратора эквивалентов в процентную форму.

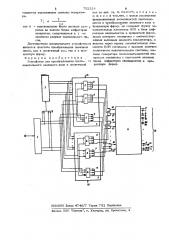

На чертеже показана блок-схема пред лагаемого устройства, содержащая входноя коммутатор l, элемент 2 ИЛИ, генера24 4 кодом, начинается с младшего разряда.

По потенциальному тактовому сигналу C на информационный вход входного коммутатора подается младший двоичный разряд преобразуемого кода, поступающий в случае равенства этого разряда "1" через коммутатор, на элемент 8 И и 9 ИЛИ, блока -шифраторов процентов в коде 22221.

При этом остальные элементы И блока шифраторов процентов подготавливаются к открытию по очереди импульсами генератора последовательностей импульсов 3, который запускается сигналом с элемента

ИЛИ, С выхода элемента 9 ИЛИ через элемент 10 ИЛИ сигнал поступает на вход младшей декады накапливающего счетчика.

3 :7523 тор 3 последовательностей импульсов, блок

4 шифраторов эквивалентов в коде 22221, шифратор 5 эквивалентов кода 22221, элемент 6 ИЛ:И, блок 7 шифраторов эквивалентов в процентной форме, шифратор 8

5 эквивалентов в процентной форме, элемен ты 9 и 10 ИЛИ, двоично-накопительный счетчик 11, входной, информационный вход

12, выход десятичного кода (процентов)

13, вход 14 управления преобразователем 1о двоичного кода в десятичный, вход 15 управления преобразованием двоичного кода в проценты.

Устройство может осуществлять либо преобразование последовательного двоичного кода в десятичный (при этом на вход 14 подается управляющий потенциал на время преобразования), либо преобразование двоичного кода в проценты (при этом на вход 15 подается управляющий потенциал на время преобразования).

Преобразование двоичного кода в проценты осуществляется с использованием дпя представления двоичных разрядов десятичных процентных эквивалентов„выраженных с определенной точностью. Так при точности 0,1% между двоичными раз.рядами и их десятичными процентными эквивалентами существует следующая зависимость 30

2 = 50 % = 1 6 %

2 = 25% 2 .=-08%

2п-2 125 % 2 = 04 %

2 и 3 6 r> РУ 2 и 8 0 2 0r

3,1 ог -> n-9 0 1 -об

Преобразование десяти шых процентных эквивалентов осуществляется в устройстве с использованием для представления десятичных разрядов двоично-десятичного кода 22221 — разряд единиц" десятичного эквивалента представляется суммой целых весов 2, 2, 2, 2, 1; разряд "десятков - суммой весов 20, 20, 20, 20, 10; разряд сотен" — суммой весов 200, 200, 200, 200, 100 и 45 т.д., разряд десятых — суммой дробных весов 0,2 — 0,2 — 0,2 - 0,2 — О, 1 и

T.д.

В процессе преобразования каждый разряд десятичного процентного эквива-« лента двоичного разряда представляется, в коде 22221 и подается на накапливающий двоично-десятичный счетчик.

Перед началом преобразования двоично-десятичный накопительный счетчик и генератор 3 устанавливаются в нулевое состояние.

Преобразование двоичного (целого) числа, представляемого последовательнымПреобразование j -го разряда двоичного кода происходит аналогично. По потенциальному тактовому сигналу " на информационный вход входного коммутатора подается j -й двоичный разряд. В случае равенства этого разряда " 1" потенциальный сигнал с j -oro выхода коммутатора поступает на элемент ИЛИ

2 и те элементы 8 И блока шифраторов процентов, KOTopbte cooTBeTcòâóþò разрядам десятичного эквивалента j --го двоичного разряда в форме процентов, Управляющие импульсы с выходов генератора поочередно в течение действия 7 открывают выбранные элементы И блока шифраторов процентов. При этом с их выходов в соответствии со значениями разрядов десятичного эквивалента j -го двоичного разряда в форме процентов nooseредпо на соответствукицие входы накопительного счетчика поступают через элементы 8 ИЛИ блока шифраторов процентов сигналы с весами 0,2 — 0,2 — 0,2—

02 — 01;3,2,2,2, 1;20,20,20, 20, 10. В двоично-десятичном счетчике

11 происходит накопление этих весовых . сигналов.

Накопленный двоична-десятичный процентный эквивалент переводимого числа преобразуется с помощью дешифраторов, входящих в состав двоично-десятичного счетчика 11 в десятичный процентный эквивалент, поступающий на выход 13.

На выходах генератора 3 в течение л, действия сигнала c > вырабатывается только по одному управляющему импульсу.

Лля обеспечения надежной работы уст ройства необходимо соблюдение следуюI щего соотношения для длительности тактирующих сигналов Т, по которым. выраба5 752З тываются управляющие сигналы генератоPQ„ г

Т .с

2п где 0 — максимальное число весовь раз- рядов на выходе блока шифраторов процентов, содержащееся в -м двоичном разряде переводимого ясла. достоинством предлагаемого устройства 10 является простота преобразования двоичных чисел, как в десятичный код, так и в процентную форму.

Формула изобретения

Устройство для преобразования после- . довательного двоичного кола в десятичный

24 6 код по авт. св. No 622076, о т л и ч а— ю щ е е с я тем,что, с целью расширения функциональных воэможностей заключающееся в преобразовании двоичного кода в процентную форму, он содержит группу дополнительных.элементов ИЛИ и блок шифраторов эквивалентов в процентной форме, входы которого соединены с соответствующими выходами входного коммутатора, а выходы через группу дополнительных элементов ИЛИ соединены с входами двоичнодесятичного накопительного счетчика, выходы генератора последовательностей импульсов соединены с тактовыми входами блока шифраторов эквивалентов в про центную форму.

ЦНИИПИ Заказ 4746/7 Тираж 751 Подписное филиал ППП Патент, r. Ужгород, ул. Проектная, 4