Множительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<11> 752335 (б)) Дополнительное к авт. свид-ву (22) Заявлено 31.07.78 (21) 2650827/18-24 с присоединением заявки ¹ (57)М. Кл.

G 06 F 7/52

Госуларетвениый комитет

СССР по хелам изобретений и открытий (23) Приоритет

Опубликовано 30.0780. Бюллетень ¹ 28

Дата опубликования описания 3007.80 (53) УДК 681 325 (088. 8) (72) Авторы изобретения

А. П. Кондратьев и B М. Ленкова (71) Заявитель (54 ) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычисли.тельной технике и может быть использовано в арифметических устройствах цифровых ЭВМ малого и среднего класса.

Известны устройства для умножения двоичных чисел, содержащее параллельный сумматор и сдвиговые регистры.

Умножение в таких устройствах выполняется одновременно на несколько

10 разрядов множителя (1).

Известно множительное устройство, умножение в котором выполняется одновременно на четыре разряда множи теля за счет образования в каждом шаге умножения двух простых кратных множимого, соответствующих двум парам разрядов множителя (2).

30

Недостаток устройства — использование громоздкого трехвходового сумматора с приведением переносов.

Известны также множительные устройства, в которых одновременное умножение на 4 разряда множителя обеспечивается предварительным вычислением кратных множимого.

Кратные хранятся в специально отведенных ячейках местной памяти.

Число кратных выбирается таким, чтобы в процессе умножения на каждую тетраду множителя выполнялось меньше подсуммирований к текущему частичному. произведению, причем для значений тетрад множителя от

1000 до llll вместо сложения производится вычитание кратных (3).

Недостатком известных устройств является невысокое быстродействие вследств ие необходимости на каждом i шаге умножения производить несколько циклов суммирования. дополнительные циклы требуются для подсуммирования старших разрядов кратных, так как по разрядности кратные больше множимого и занимают обычно две ячейки местной памяти.

Наиболее близким по техническому исполнению является множительное устройство, содержащее сумматор, па" мять кратных множимого, первый и второй сдвиговые регистры, узел управления, первый вход сумматора подключен к выходу памяти кратных, второй вход сумматора подключен к выходу первого сдвигового регистра, выход сумматора подключен ко входам сдвиговых регистров, выход младшей тетрады второго.сдвигового регистра

752335

6Î

Л подключен ко входу узла управления, выход которого подключен к адресному входу памяти кратных (4).

Недостатком данного устройства является невысокое быстродействие.

Цель изобретения — .повышение быстродействия.

Для достижения поставленной цели в устройство, содержащее сумматор, память кратных множимого, первый и второй сдвигоные регистры, узел управления, причем выход сумматора подключен ко входам и рного и второго сдвиговых регистров и ко входу памяти кратных, выход младшей тетрады второго сдвигового регистра соединен со входом узла упранления, первый выход которого подключен к адресному входу памяти кратных, введены ренерсинный счетчик, узел хранения старших разрядов кратных множимого, первый и второй входные регистры, причем счетный вход реверсивного счетчика соединен с выходом неренсса старшего разряда сумматора, установочный вход реверсивного счетчика соединен с выходом узла хранения старших раэрядон кратных, разрешающий вход реверсивного счетчика соединен со вторым выходом узла управления, третий выход которого соединен с разрешающим входом старшей тетрады первого сдвигоного регистра, а четвертый выход — с выхо„,ной шиной устройства, выхсд реверсивного счетчика соединен с информационным входом старшей тетрады первого сдвигового регистра и со входом узла хранения старших раэрядон кратных, управляющий вход узла хранения старших разрядов кратных соединен с первым выходом узла управления, выход младшей тетрады первого сдвигоного регистра соединен с информационным входом старшей тетрады второго сдвигового регчстра, первый вход первого входного регистра соединен с первой входной шиной устройства,ВТорой вход первого входного регистра соединен с выходом памяти кратных, а выход - с первым входом сумматора первый нход второго входного регистра соединен с второй входной шиной устройства, второй вход второго входного регистра соединен с выходом первого сдвигового регистра, а выход - со вторым входом сумматора.

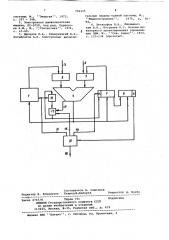

На чертеже представлена схема множительного устройства.

Множительное устройство содержит память 1 кратных множимого, первый входной регистр 2, первую входную шину 3 устройства, сумматор 4, второй входной регистр 5, вторую входную шину 6 устройства, первый регистр 7 сдвига, второй . регистр Э сдвига, à óå тетраду

9 второго регистра сдвига, узел 10. управления умножением, первый выход ll узла упранления умножением, узел 12 хранения старших разрядов кратных, реверсивный счетчик 13, старшую тетраду 14 первого регистра сдвига, второй 15 и третий 16 выходы узла управления умножением, выход 17 переноса из старшего разряда сумматора, ныходную шину 18 устройства.

Умно. кение н устройстве выполняется одновременно на четыре разряда множителя, начиная с младших разрядов.

Разрядность сумматора 4 ранна разрядности ячейки памяти 1 кратных и регистрон 7,8 сдвига.

В начале операции вычисляются кратные множимого A. Так, для кратного 2А множимое А подается на первый 2 и второй 5 входные регистры (с первой 3 и второй б входных шин устройства) и складываются н сумматоре 4. Результат с выхода сумматора 4 записывается в определанную ячейку памяти кратных, а выходной перекос, если он появится, запомнится н реверсивном счетчике

13 (преднарительно сброшенном н 0 ), и оттуда записывается в соответствующую ячейку узла 12 хранения старших разрядов кратных, представляющего собой группу ад,>есуемых регистров (ячеек). При вычислении кратного ЗА, кратное 2А считывается из памяти 1 кратных и узла 12 хранения старших раэрядон, Разряды кратного, считанные из памяти 1 кратных, подаются на первый входной регистр 2, а старший разряд из узла 12 поступает на установочный вход реверсивного .счетчика 1 3.

На второй входной регистр 5 снона подается по входной шине 6 множимое

А. После сложения н сумматоре 4 и добавления выходного переноса (если он появится) к содержимому реверсивного счетчика 13 получившееся кратное

ЗА запишется в ячейки памяти 1 кратных и узла 12 хранения старших разрядов.

Подобным же образом вычисляются и следующие кратные. Если, например вычисляются кратные, соответствующие кодам 0010 - 1000 тетрады множителя (2A, ЗА, 4А, 5Ai 6А, 7А и SA), то узел 12 хранения должен иметь семь ячеек для запоминания в них старших разрядов кратных.

Разрядность ячеек узла 12 меняется от одного бита (для 2A) до четырех бит (длЯ 8A). ДлЯ кодов 1001 — 1111 в тетраде множителя кратные не нычисляются, так как при этих кодах суммирование заменяется вычитанием из частичного произведения кратных, соответствукщих кодам 0111 — 0001 в тетраде множителя.

Перед начат м основных циклов умножения, кратные хранятся в па"752335 мяти 1 и узле 12, множитель заносится (через сумматор) во второй регистр 8 сдвига, а первый регистр

7 сдвига обнуляется.

В каждом цикле умножения, в зависимости от содержимого младшей тетрады 9, узел 10 управления умножением выдает на выход 11 соответствующий адрес. По этому адресу считывается иэ памяти 1 кратных и узла 12 соответствующее кратное, все разряды которого, кроме старших, занесутся на первый входной регистр

2. Старшие разряды этого кратного с выхода узла 12 занесутся в реверсивный счетчик через его установочные входы. На второй входной регистр 5 подается частичное произведение (нули в первом цикле) с первого регистра 7 сдвига.

В з ав ис имос ти от кода в младшей тетраде регистра 8, сумматор 4 выполнит или сложение или вычитание (кратного из частичного произведения). При появлении переноса на выходе 17 сумматора 4, он поступит на счетный вход реверсивного счетчика 13 и, в зависимости от сигнала на выходе 15 узла управления умножением, произойдет или добавление или вычитание единицы из содержимого реверсивного счетчика )3.

После сложения (вычитания) результат с выхода сумматора 4 заносится в первый регистр 7 сдвига, в котором затем произойдет сдвиг полученного частичного произведения вправо на четыре разряда. При сдвиге в старшую тетраду 14 регистра 7 сдвига передается по сигналу с выхода 16 узла 10 управления умножением содержимое реверсивного счетчика 13. Одновременно множитель храняшийся в регистре 8 также сдвинется на четыре разряда вправо. В младшей тетраде 9 этого регистра окажется следующая тетрада множителя, а в старшую тетраду регистра 8 заносится содержимое младшей тетрады регистра 7 сдвига. После умножения на последнюю (старшую) тетраду множителя узел 10 управления умножением выдаст сигнал окончания операции на выходную шину

18 устройства.

Старшая часть произведения находится в регистре 7, младшая часть произведения — в регистре 8.

Предлагаемое иэобретечие обеспечивает увеличение быстродействия множительного устройства за счет сокращения в два раза количества циклов суммирав ания на каждом шаге умножения, Если принять разрядность операндов равной 32, та при умножении одновременно на четыре бита множителя, в предлагаемом устройстве потребуется восемь циклов суммирования, вместо шестнадцати.

В два раза также уменьшится количество циклов суммирования при вычислении кратных множимого. Если учесть время фазы выборки команды, то полное время выполнения команды . умножения сократится примерно на

30-50% по сравнению с прототипом.

Формула изобретения

Множительное устройство, содержащее сумматор, память кратных множимого, первый и второй сдвиговые регистры, узел управления, причем выход сумматора подключен ко входам первого и второго сдвиговых регистров и ко входу памяти кратных, вы:.ход младшей тетрады второго сдвиговаго регистра соединен со входом узла управления, первый выход которого подключен к адресному входу памяти кратных, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия в устройство введены реверсивный счетчик, узел хранения старших разрядов кратных, первый и второй входные регистры, причем счетный вход реверсивного счетчика соединен с выходом переноса старшего разряда сумматора, установочный вход реверсивного счетчика соединен с выходом узла хранения старших разрядов кратных„ разрешающий вход счетчика соединен со вторым выходом узла управления, третий выход которого соединен с разрешаюшим входом старшей тетрады первого сдвигового регистра, а четвертый выход — с выходной шиной устройства, выход реверсивного счетчика соединен с информационным входам старшей тетрады первого сдвигового регистра и со входом узла хранения старших разрядов кратных, управляющий вход узла хранения старших разрядов кратных соединен с первым выходом узла управления, выход младшей тетрады первого сдвигового регистра соединен с информационным входом старшей тетрады второго сдвигового регистра, первый. вход первого входного регистра соединен с первой входной шиной устройства, второй вход первого входного регистра соединен с выходом памяти кратных, а выход — с первым входом сумматора, .первый вход второго входного регистра соединен с второй входной шиной устройства, второй вход второго входного регистра соединен с выходом первого сдвиговага регистра, а выход - со вторым входом сумматора.

Источники информации, принятые во внимание при экспертизе

1. Каган Б.M. Каневский Н.M.

Цифровые вычислительные машины и

752335

Составитель Н. Слюсарев

Техред Н»Бабурка

Редактор И. Ковальчук

Корректор И. Муск

Заказ 4747/8 Тираж 751

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подпис ное

Филиал ППП Патент., r. Ужгород, ул. Проектная, 4 системы; М., Энергия, 1973, с. 327 - 346.

2. Электронная вычислительная машина, ЕС-. 1050, под ред. Ларионова A,Ì., М., Статистика, 1976, с. 67-69.

3. Дроздов Е.A. Камарницкий В.A.

Пятибратов A.П. Электронные вычислительные машины единой системы. М., Машиностроение, 1976, с. 819;4 °

4 . Хетагуров Я . А,, Малишевский В . В ., Потураев О . С . Основы инженерно го проектирования управляющих ЦВМ, М ., Сов . радио, 1 9 7 2, с . 1 2 3-1 3 4 (прототип ) .