Логарифмический аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Ф ч.

Ой ИКАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (i» 752370

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I) Дополнительное н авт. свид-ву— (22) Заявлено 02.08.77 (21)2513679/18-24 с присоединением заявки И— (23) Приоритет— Опубликовано 30.07.80. Бюллетень И 28

Дата опубликования описания 02.08.80 (51)M. Кд.

Cj 06 Ci 7/24

Государстееииый комитет

СССР по делам изобретений и открытий (53) УДК 681,335 (088.8) (?2) А вторы изобретения

П. М. Сопрунюк и A. А. Пац

Физико-механический институт АН Украинской ССР (?I) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к функциональным преобразователям электрических сигналов и может быть использовано в аналоговых вычислительных машинах.

Один из известных функциональных преобразователей аналоговых сигналов содержит интегратор, ключевые элементы, компаратор, генератор тактовых сигналов, блок управления, блок цифровой индикации Pl) .

Это устройство характеризуется отt0 носительно низкой точностью функционального преобразования сигналов.

Наиболее близким к предлагаемому является логарифмический аналого-цифро15 вой преобразователь, содержащий усилительный блок, инвертирующий вход которого через шунтирующий ключевой элемент соединен с шиной нулевого потенwana, вход устройства через последовательно соединенные входной ключевой алемент и масштабнрующнй резистор подключен к инвертирующему входу усилительного блока, между неинвертирующим входом которого и шиной нулевого потенциала включен запоминающий элемент, между инвертирующим входом и выходом усилительного блока подключены интегрирующий конденсатор, а также соединенные последовательно разрядный резистор и разрядный ключ, выход усилительного блока присоединен к одному входу компаратора, другой вход которого соединен с шиной нулевого потенциала, выход компаратора подключен ко входу триггера, а через ключевой алемент обратной связик неинвертирующему входу усилительного блока, выход триггера присоединен ко входу блока цифровой индикации, выход генератора тактовых сигналов подключен ко входу блока управления, первый выход которого соединен с управляютцим входом входного ключевого алемента, второй выход блока управления подключен к допол нительному входу блока цифровой индикации $2(.

Это устройство имеет невысокую точность работы из- эа погрешности, вызван752370

4 руюшей цепи, образованной масштабируюшим резистором 14 и интегрирующим конденсатором 16.

В следующем такте работы устройст5 ва такте преобразования, сигналами с блока 10 управления размыкается входной ключевой элемент 1, шунтируюший ключевой элемент 2 и ключевой элемент

3 обратной связи остаются в разомкну10 Гом состоянии, триггер 8 устанавливает.ся в исходное состояние, а разрядный ключевой элемент 4 замыкается. На выходе усилительного блока 5 формируется убывающее напряжение экспоненциальной формы, определяемое разрядом интегрирующего конденсатора 16 через разрядные резистор и ключевой элемент

15и4.

3 ной ложным срабатыванием компаратора при малых значениях выходного напряже ния интегрирующего узла.

Цель изобретения — повышение точнос ти работы.

Поставленная цель достигается тем, что в него введены модулятор и генера тор опорной частоты, вход которого соединей с выходом блока цифровой индикации, выход генератора опорной частоты через модулятор подключен к дополнител ному входу усилительного блока, третий выход блока управления присоединен к управляющим входам шунтируюшего ключевого элемента и ключевого элемента. обратной связи, четвертый выход блока управления подключен к управляющему входу разрядного ключевого элемента и второму входу триггера.

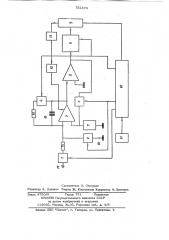

Функциональная схема логарифмического аналого-цифрового преобразователя изображена на чертеже.

Устройство содержит входной ключевой элемент 1, шунтируюший ключевой элемент 2, ключевой элемент 3 обратной связи, разрядный ключевой элемент

4, усилительный блок 5, компаратор 6, запоминающий элемент 7, триггер 8, блок 9 цифровой индикации, блок 10 управления, генератор 1 1 тактовых сигналов, модулятор 12, генератор 13 опорной частоты, масштабируюший резистор

14 разрядный резистор 15, интегрирую) ший конденсатор 16, вход 17 устройства.

Устройство работает следуюшим образом.

Цикл работы устройства разбит на четыре равных по времени такта, определяемых блоком 10 управления, который по сигналам генератора 11 тактовых сигна- 40 лов в определенной последовательности формирует сигналы управления, подаваемые на связанные .с ним функциональные блоки.

В такте измерения входной сигнал, со входа 17 устройства через замкнутый входной ключевой элемент 1 поступает на вход усилительного блока 5, и интегрируется на интегрирующем конденсаторе

16. При этом шунтируюший ключевой

BJIBMBHT 2, ключевой элемент 3 обратной связи и разрядный ключевой элемент

4 разомкнуты. Интегрирующий конденсатор 16 заряжается до напряжения, вели55 чина которого прямо пропорциональна величине входного сигнала устройства, вре лени такта измерения и обратно пропор циональна. постоянной времени интегриНапряжение на интегрирующем конденсаторе 16 убывает до нулевого уровня; при этом на выходе компаратора 6 формируется нарастающее автоколебательное напряжение. Амплитуда выходного напряжения компаратора 6 и время достижения его максимального значения зависит от величины выходного напряжения усилительного блока 5. Триггер 8 отмечает начало генерации выходного напряжения компаратора 6 и конец преобразования. Длительность импульса на выходе триггера 8 соответствует началу и концу преобразования и пропорциональна произведению постоянной времени разрядной цепи, образованной разрядным резистором 15 и интегрирующим конденсатором 16 на логарифм от выходного напряжения усилительного блока 5 (интегрируюшего узла).

Блок 9 цифровой индикации регистрирует результат преобразования.

При работе устройства в такте компенсации блок 10 управления формирует сигналы, согласно которым входной ключевой элемент 1 и разрядный ключевой элемент 4 разомкнуты, а шунтируюший ключевой элемент 2 и ключевой элемент обратной связи 3 замкнуты. На запоминающем элементе 7 происходит запоминание напряжения дрейфа нуля усилительного блока 5 и компаратора 6 c òî÷íîñòüþ до произведения их коэффициентов усиле» ния (передачи).

В такте измерения из обшего напряжения (измеряемое напряжение плюс . напряжение дрейфа) вычитается напряже-, ние дрейфа нули.

5 7523

В четвертом такте работы устройства, подготовительном такте, устанавливается в исходное состояние блок 8 цифровой индикации.

При больших значениях сигнала на входе 17 устройства увеличивается вре» мя преобразования и время близкого рас положения около нуля хвоста экспоненциального убывающего напряжения на выходе усилительного блока 5. 10

При таких значениях входного сигнала генератор 13 опорной частоты через модулятор 12 осуществляет подмодуляцию выходного напряжения усилительного блока 5. Вследствие этого уменьшается вероятность ложного срабатывания компаратора 6, т. е. уменьшается погрешность логарифмического преобразования входного сигнала.

Таким образом, предлагаемый логариф- 20 мический аналого-цифровой преобразователь обладает более высокой точностью работы.

Формула изобретения

Логарифмический аналого-цифровой преобразователь, содержащий усилительный блок, инвертирующий вход которого через шунтирующий ключевой элемент соединен с шиной нулевого потенциала, вход устройства через последовательно соединенные входной ключевой элемент и масштабирующий резистор подключен к 35 инвертирующему входу усилительного блока, между неинвертирующим входом которого и шиной нулевого потенциала включен запоминающий элемент, между инвертирующим входом и выходом усиди- 40

70 6 тельного блока подключены интегрирующий конденсатор, а также соединенные последовательно разрядный резистор и разрядный ключевой элемент, выход усилительного блока присоединен к одному входу компаратора, другой вход котороto соединен с шиной нулевого потенциала, выход компаратора подключен ко входу триггера, а через ключевой элемент обратной связи — к неинвертирующему входу усилительного блока, выход триггера присоединен ко входу блока цифровой индикации, выход генератора тактовых сигналов подключен ко входу блока управления, первый выход которого соединен с управляющимвходом входного ключевого элемента, второй выход блока управления подключен к дополнительному входу блока цифровой индикации, о т л и ч а ю щ и й« с я тем, что, с целью повышения точности работы, в него введены модулятор и генератор опорной частоты, вход которого соединен с выходом блока цифровой индикации, выход генератора опорной частоты через модулятор подключен к дополнительному входу усилительного блока, третий выход блока управления присоединен к управляющим входам шунтирующего ключевого элемента и ключевого элемен та обратной связи, четвертый выход блока управления подключен к управляющему входу разрядного ключевого элемента и второму входу триггера .

Источники информации, принятые во внимание при экспертизе

1. цифровые электроизмерительные приборы. Под ред. Шлянндина Н. М. М., Энергия, 1972, с. 161-164, рис. 3-1

2. Электроника, Мнр, 1973, )4 14, с. 57-58 (прототип).

782370

Составитель О. Отраднов

Редактор А. Йолинич Техред Ж. Кастелевич Корректор Н. Григорук

Закаэ 4750/9 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул, Проектная, 4