Полупостоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ изовеитения

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскмк

Соцмалмстмчесник

Реслублмн

< 752467

\, / (61) Дополнительное K акт. свнд-ву (22) Занвлено31.07.78 (21) 2651884/18-24 (5() Щ, Кл, 5 11 С 11/00 с прнсоеанненнем заявки РЙ йеударстееииый комитет

СССР (23) Приоритет ио делам изобретений. и открытий

Опубликовано 30.07.80. Бюллетень .% 28 (53) УДК 681.327. .6(088,8) Дата опублнковамня описания 30.07.80 (72) Авторы изобретения

Г. М. Рылешников, Л. К. Сафронов и A. А. Гунько (7!) Заявитель

Ленинградский институт киноинженеров (54) ПОЛУПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислигельной технике и может быть использовано при изготовлении полупостоянных запоминеоших устройств, применяемых в системах автоматики, телемеханики и контроля функционирования радиоэлектронной anna-

5 ратуры.

Известны полупостоянные запоминающие устройства, построенные на основе матричных схем. В качестве буферных

1О устройств, связывающих их с внешним источником информации, служат либо регистр, либо матрица Ii) и (21.

В подобных запоминающих устройствах информация предварттгельно накапли15 вается в регистре или матрйце, а затем в нужный момент перезаписывается в основную матрицу.

Недостатком упомянутых полупостоянных запоминающих устройств является раз20 деление во времени процесса записи и считывания и относительно большое время

- перезаписи информации в основную матрицу. Кроме того, перед считыванием ин2 формации иэ накопителя требуется дополнительное время на проверку достоверности произведенной записи.

Прн применении в качестве буферного устройства регистра, равного по обьему памяти столбцу илн строке матрицы, время, затрачиваемое на перезапись информации в матрице может увеличиваться иэ-аа малого быстродействия внешнего источника информации. Если же в качестве буферного устройсгва применена матрица, то нз-эа присущих ей недостатков, например большое количество входов, сбой дешифратора адреса, схемная чувствительность матрицы к виду информации, запоминаюшее устройство в целом усложняется, а его надежность снижается.

Бель изобретения — повышение надежности записи информации., Поставленная цель достигается тем, что в полупостоянное запоминающее устройство, содержащее регистр адреса, дешифраторы адреса, входы которых подключены к соответствующим шинам управле2467 4 связи с тем, что информация из накопителя переэаписывается в регистр за один такт, дальнейший процесс контроля мс» жет проводиться практически независимо

5 от процесса считывания. Точно также независимо от процесса считывания в матрице может быть проверена и работа регистра. Для этого контроль информации в регистре проводится до ее перезаписи из

1р регистра в матрицу.

Основным преимушеством полупостоянного запоминающего устройства является прямая связь регистра и элементов памяти накопителя, благодаря чему обес15 печиваИся надежность записи при большой скорости воспроизведения и перезаписи информации.

Полупостоянное запоминающее устройство, содержащее регистр адреса, дешифраторы адреса, входы которых подключе25 ны к соответствуюшим шинам управления, накопитель, входы элементов памяти кото рого соединены с соответствуюшими выходами дешифратора, и усилитель считывания, входы которого подключены к соот30 ветствуюшим выходам накопителя, о чл и ч а ю ш е е с я тем, что с целью повышения надежности записи информации, оно содержит стробируемые ключи-формирователи, управляющие входы которых

35 псдключены к соответствующей шине управления, а выходы соединены с соответствуюшими входами регистра адреса и элементов памяти накопителя с одинаковым адресом.

40 Источники НН МВННН принятые во внимание при экспертизе

1. Шигин А. Г. и Дерюгин А. А. цифровые вычислительные машины М., тр, "Энергия", 1975.

45 2. Патент США М 3740723, кл. 340-172.5, заявл. 28.12.70> опублик. 19.06.73 (прототип).

3 75 ния, накопитель, входы элементов памяти которого соединены с соответствующими выходами дешифратора, и усилитель считы,вания, входы которого подключены к соот ветствукшим выходам накопителя, введены стробируемые ключи-формирователи, управляюшие входы которых подключены к шине управления, а выходы соединены с соответствуюшими входами регистра адреса и элементов памяти накопителя с одинаковым адресом.

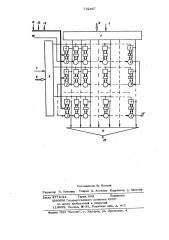

На чертеже представлена структурная схема полуг:остоянчого запоминающего устройства.

Устройство включает в себя накопитель 1, стробируемые ключи-формирователи 2, регистр 3 адреса, дешифраторы строки 4 и столбца 5 шины 6,7 и 8 управления дешифраторами, усилитель 9 считывания, шина 10 ввода информации, шины 11, 12 и 13 управления ключамиформирователями шины 14 вывода информации из матрицы, шина 15 вывода информации из регистра.

В режиме стирания перед записью информации на шину управления подается команда, по которой все элементы накопителя устанавливаются в ноль. Регистр в этом режиме работает независимо от накопителя.

В режиме записи информация предварительно вводится через шику 10 в регистр 3. Затем на шину 10 подается команда Прямая запись, и вся информация хранимая в регистре, перезаписывается с помошью ключей-формирователей 2 в соответствующие по адресу элементы на; копителя 1.

В режиме контроля информация, записанная в накопителе, проверяется в следуюшем порядке. По шине 11 в запоминающее устройство подается команда Обратная запись". При этом информация иэ накопителя перезаписывается в регис после чего она выводится иэ регистра для сравнения с "эталонной" информацией, находящейся во внешнем устройстве. В

20 Фор мула изобретения

7 52467

Составитель В. Костин

Редактор И. Нанкина Техред И. Асталош Корректор С. Шекмар

Закаэ 4774/24 Тираж 662 Подписное

ЦНИИПИ Государственного комитете СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4