Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига

Иллюстрации

Показать всеРеферат

(б1) Дололнительиое к авт. сеид-ву(22) Заявлено 18. 07. 78 (21) 2646976/18-24 с присоединением з а явки Ио— (23) Приоритет—

Опубликовано 30.0780. Бюллетень Йо 28

Дата опубликования описания 04.0880 51 М ) „а

6 11 С 19/00

Государственный комитет

СССР но делам изобретений и открытий

if 53) УД)(б 8 1 ° 3 2 7 ° 6 6 (088.8) (72) Авторы изобретения

В.И.Вешняков, B.Ã.Bàcèëüåâ и B.И.Корнейчук (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ МНОГОТАКТОВОГО

ЗАПОМИНАЮЩЕГО УСТРОИСТВА НА РЕГИСТРАХ СДВИГА

Изобретение относится к области запоминающих устройств ЗУ и может быть использовано как составная часть бункерного ЗУ, основным назначением которого является накопление высокоскоростной спорадической информации, например в телеметрии, совмещение цифровых устройств с различными пропускными способностями и т.п.

Известен распределить импульсов для бункерного ЗУ с раздельными цепями сдвига в накопителе, содержащий двухступенчатый статический триггерный регистр P1) .

В указанном устройстве управление сдвигом в регистрах накопителя осуществляется от распределителя импульсов по раздельным цепям.

Недостатком этого распределителя является неполная его асинхронность.

Наиболее близким из известных по технической сущности к предлагаемому является распределитель, содержащий первую и вторую группы триггеров, шины управления сдвигом, накопительные элементы t21 .

К недостаткам этого распределителя следует отнести сложность структуры и низкое быстродействие по занесению информации (в указанном известном устройстве высокое быстродействие достигнуто средствами особой технологии, но не оптимизацией структуры распределителя}.

Цель изобретения — повышение быстродействия и упрощение распределителя.

Поставленная цель достигается тем, что в распределителе импульсов для многотактового регистрового запоминающего устройства Hà perистрах сдвига, содержащем две группы триггеров, накопительные элементы, например, первый и второй конденсаторы, одни из обкладок которых соединены с шиной нулевого потенциала, шину занесения информации и шины управления сдвигом, нулевой выход i-го триггера первой группы соединен с нулевым входом i-ro триггера и единичным входом (i + 1)-го триггера второй группы и с другой обкладкой первого конденсатора, нулевой выход i-го триггера второй группы соединен с нулевым входом (i — 1)-го триггера и единичным входом i-го триггера первой группы, с другой обкладкой второго конденсатора и i-ой шиной управления сдвигом.

752488

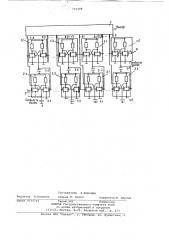

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит триггеры 1.

1.1-1 0 первой группы, триггеры

2.1-2 второй группы, накопительные элементы, например, первые и вторые конденсаторы 3.1-3 0 и 4.1-40, шину

5 занесения информации, шины 6.1-60 упранления сдвигом, накопитель 7 регистрового ЗУ, шину 8 считынания, шину 9 нулевого потенциала. Каждый триггер выполнен на четырех ключевых МДПтранзисторах и других резисторах.

Накопитель 7 регистрового ЗУ состоит из одноступенчатых 3 — разрядных (или 6 -позиционных, где глубина бункера) сдвиговых регистров с раздельными шинами сдвига и содержит, кроме того, усилителей импульсов, входы которых подключены к соответствующим шинам управления сдвигом (на чертеже не показаны).

Распределитель импульсов работает следующим образом.

Первое слово выводится первым. По мере поступления новые данные продвигаются по регистрам накопителя 7 и занимают позиции вплотную к выходу.

Если в накопителе заполнены от 1-ой до -ой позиции, то триггеры 1. i-1.0 распределителя установлены в "1" (на нулевых их выходах низкие потенциалы), а триггеры 1.1-1.(< — 1) установлены в "0". Триггеры 2.1-2(i — 1) при этом блокированы, так как на нулевых и единичных их входах высокие потенциалы, и соответственно на их выходах низкие потенциалы. Триггеры

2.i — 2. 3 при этом установлены в

"1".

Занесение нового информационного слова осуществляется подачей отрицательного импульса на шину 5 занесения информации. На нулевом выходе триггера 2.1 при этом с задержкой, определяемой узловой емкостью, появляется импульс, который производит занесение входного слова на первую позицию в накопителе 7 и устанавливает в "1" триггер 1.1. По окончании входного импульса на шине 5 триггер

2.1 переключается н "1". Отрицательным потенциалом на выходе триггера

1.1 переключается с задержкой в "0" триггер 2.2 и импульс действует по

2-ой цепи. управления сдвигом, производя при этом переключение с определенной задержкой триггера 1.1 в "0", а триггера 1.2 — в "1". Аналогично происходит дальнейшее последовательное возбуждение шин 6.1-6.0,управления, маркерная "1" "пробегает" по распределителю слева направо, а усилители формируют импульсы по раздель ным шинам сдвига н накопителе. Когда импульс управления действует íà шине б.i, то он переключает н "1" триг гер 1.i и возвращает в "0" триггер

1.(i — 1). При этом длительность импульса обуславливается суммарной эа держкой последовательного переключения цепочки элементов двух транзисторов триггера 1.(i — 1) зарядом конденсатора 3.(— 1) на его выходе, од.ного из транзисторов 2 триггера 2.i и разрядом емкости на его выходе.

Время задержки между возбуждениями двух соседних шин, например (i — 1)-ой и -ой, обуславливается задержкой на лереключение одного транзистора 4 триггера 1.(i — 1), разрядом екости на его выходе, переключением одного транзистора 3 триггера 2.i и зарядом емкости на его выходе. Длительность импульса равна или немного больше нремени задержки между импульсами на двух соседних шинах управления, а усилители отрабатывают входной сигнал с некоторой задержкой по заднему

20 фронту, таким образом, что импульсы по шинам сдвига в накопителе частично перекрываются.

Если импульс действует на

6.(i — 1)-ой шине, переключая триггер 1. (i — 1) в "1", а триггер 1. i уже находится в "1", то импульса на шине б не будет и триггер 1.(i — 1) останется в "1". Это означает, что новое слово продвинулось по регистрам накопителя 7 на нужную позицию вплотную к ранее заполненным данным.

Занесение данных осуществляется асинхронно при наличии сигнала "Готовность входа", указывающего на неполное заполнение бункера.

Считывание из Зу осуществляется подачей короткого положительного импульса на шину 8 при наличии информации в ЗУ, на что указывает сигнал

"Готовность выхода". При этом триг40 гер 1. 0 переключается с некоторой задержкой в "0", далее с некоторой задержкой переключается в "0" триггер 2. E и на шине б. 6 действует импульс, производя сдвиг слова в накопителе 7 с E — 1-ой позиции в ую (на выход). При этом с задержкой переключается в "0" триггер

1 (6 - 1) и возвращается н "1." триггер 1.0. Дальнейшее последовательное возбуждение шин управления сдвигом происходит аналогично и маркерный "0" "пробегает" по распределителю справа налево. Когда импульс действует на шине б.i, то он переключает н "0" триггер 1.(i — 1)

55 и возвращает в "1" триггер 1.1. Длительность импульсов при считывании формируется той же цепочкой элементов, что и при занесении, а задержка между импульсами двух сосед60 них шин, например б i-ой и 6(i — 1)ой, обуславливается суммарной задержкой последовательного переключения следующих элементов: двух транзисторов триггера 1(» — 1) зарядом емкости на его выходе, переключени752488 ем двух транзисторов триггера

2 (i — 1), а также зарядом емкости на его выходе. Это время больше, чем длительность импульса (так как основная задержка за счет заряда емкости), и последовательное возбуждение шин управления сдвигом 6.8 -б.i при считывании и соответственно шин сдвига в накопителе происходит неперекрывающимися импульсами.

Если импульс действует на шине б.i, устанавливая в "0" триггер

1.(i - 1), а триггер 1.(i — 2) находится также в "0", то импульса на шине б.i — 1, не будет, и триггер

1.(i — 1) останется в "0". Это означает, что вес массив данных в ЗУ сдвинулся на одну позицию к выходу.

Считывание и занесение данных могут осуществляться асинхронно независимо одно от другого, возможно, например, одновременное считывание 20 и занесение данных на разных частотах. При этом происходит встречное продвижение маркерных "0" и "1", а в нужном месте дальнейшее продвижение их прерывается, как и в ðàñ- 25 смотренных случаях.

Таким образом, предложенный распределитель осуществляет управление по раздельным шинам сдвига в накопителе: импульсы, "пробегая" справа Зр налево, в двух соседних шинах не перекрываются, что необходимо для исключения воэможности сквозных переносов в накопителе, а импульсы, "пробегающие" слева направо, в двух соседних шинах частично перекрываются, но в этом случае ошибок не происходит, а быстродействие по занесению данных повышается, так как процессы сдвига информационного сло- 4 ва при этом частично совмещены.

В предлагаемом распределителе импульсов достигнута высокая скорость по занесению данных, что является основным показателем для бункерного

ЗУ. Структура распределителя проста и регулярна.

Весь распределитель мультиплицирован из единственного топологического фрагмента: статического

R-5-триггера с подключенным к одному из его выходов конденсатором. Такой распределитель вместе с накопителем (структура которого так же регулярна) размещаются на одном полупроводниковом кристалле, представляющем автономное, удобное в применении, ЗУ. Из отдельных таких кристаллов можно свободно наращивать большую емкость ЗУ. изобретения формула

Распределитель импульсов для иноготактового запоминающего устройства на регистрах сдвига, содержащий две группы триггеров, накопительные элементы, например, первый и второй конденсаторы, одни из обкладок которых соединены с шиной нулевого потенциала, шину занесения информации и шины управления сдвигом, о т л ич а ю шийся тем, что, с целью повышения быстродействия и упрощения устройства, в нем нулевой выход i-ro триггера первой группы соединен с нулевым входом i-ro триггера и единичным входом (i+ 1)-го триггера второй группы и с другой обкладкой первого конденсатора, нулевой выход

i-го триггера второй группы соединен с нулевым входом (i †1)-го триггера и единичным входом t-го триггера первой группы, с другой обкладкой второго конденсатора и i-ой шиной управления сдвигом.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 630643, кл.G 11 С19/00, 01.08.76.

2. "Электроника", 1976, Р 23, с. 80-81 (прототип).

l с

752488

Составитель A. Воронин

Техред М. Петко Корректор М. Шароши

Редактор И.Нанкина

Заказ 4775/25

Тираж бб2 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ф илиал ППП "Патент" г. Ужгород ул. П

I ул. роектная, 4