Ячейка памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

О- - Й-"-И-" :— --А Н И Е

ИЗОБРЕТЕНИЯ

Союз Советскнк

Соцнапнстнческнк

Республнн оо752491

К АИТОРСКОА4У СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 24. 07. 78 (2t) 2651458/18-24 с присоединением заявки ¹(23) Приоритет публиковано 30,07.80.Бкзллетень № 28

Дата опублинования описания 04,0880 (51)м. кл.з

G 11C 19/28

Государственный комитет

СССР но делам изобретений и открытий (5З) д (681. 327. 66 (088.8) (72) Авторы изобретения (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА эами следующего триггера. Ках цый иэ инжекторов, общий для двух совмешенных структур каждого триггера, соединен с соответствующим источником тактовых импульсов. Прием информации на основной триггер происхо,дит по переднему фронту тактового имйульса Т . После окончания тактового импульса основной триггер продол10 жает находиться в одном иэ устойчивых состояний эа счет остаточных зарядов, накопленных на узловых базовых емкостях основного триггера 2 j, Прием информации в дополнительный триггер иэ основного происходит также по переднему фронту тактового импульса Т . Состояние дополнительного триггера определяется состоянием основного триггера, находящегося во включенном состоянии, как уже отмечалось раньше, эа счет остаточных зарядов на узловых базовых емкостях, которые так же определяют интервал

АЙ между тактовыми импульсами.

25 Недостатком данного регистра является то, что для работ необходимо формировать- два тактовых импульса с определенной последовательностью и интервалом между импульсами.

3О На интервал между импульсами наклаИзобретение относится к вычислительной технике, в частности, к .микроэлектронным регистрам сдвига.

Известна ячейка памяти для регистра сдвига на элементах интегральной инжекционной логики (1) .

Регистр сдвига, выполненный на известной ячейке памяти, имеет следующие недостатки.

Кроме тактового питания необходим постоянный источник питания для хранения информации в основном и дополнительном триггере каждого разряда регистра. в цепь подачи информации включены дополнительные транзисторы, два инвертора, вносящие задержку при переносе информации из одной ячейки в другую.

Наиболее близкой по технической сущности является ячейка памяти, на базе которой выполнен регистр сдвига, содержащий в каждом разряде два триггера, основной и дополнительный.

Каждый из триггеров содержит два двухколлекторных п-р-п транзистора.

Первые коллекторы каждого иэ транзисторов соединены с базами противоположных транзисторов в триггерную схему с непосредственными связями.

А вторые коллекторв соединены с баИ.И.Бычков, А,В.Барышников, B.N.Êëèìàøèí и Л.В.Попов

7524 1 дываются жесткие требования, выражающиеся в определение времени передачи информации из одного триггера в другой. Время передачи информации выбирается равным рассасыванию накопленного заряда на узловых базовых емкостях основного или дополнительного триггеров, что накладывает ограничения на частоту тактовых импульсов питания. В случае изменения тока тактового питания, величина заряда базовых емкостей тоже будет меняться, что вызывает необходимость изменения интервала между тактовыми импульсами.

Регистр сдвига не имеет возможности нормально функционировать в случае появления импульса помехи на инжекторе перекрывающейся по времени с присутствующим импульсом питания на инжекторе соседнего триггера, вследствие чего происходит передача информации на несколько разрядов.

Цель изобретения — расширение области применения за счет повышения тактовой частоты и повышение помехоустойчивости.

Поставленная цель достигается тем, что в ячейку памяти для регистра сдви га,содержащую основной триггер,выполненный на первом и втором и-р-и транзисторах, к базам и первым коллекторам которых подключены выходы первого инжектора, входы первого инжектора соединены с первой тактовой шиной, дополнительный триггер, выполненный на третьем и четвертом и-р-и транзисторах, к базам и пер-. вым коллекторам которых подсоединены выходы второго инжектора, входы которого соединены со второй тактовой шиной, эмиттеры и-р-п-транзисторов соединены с шиной нулевого потенциала, вторые коллекторы первого и второго и-р-п-транзисторов соединены с базами четвертого и третьего п-р-ll-Tðàíýèñòîðoâ соответственно, вторые коллекторы третьего и четвертого n-p-и-транзисторов соединены с первыми выходами ячейки памяти, базы первого и второго и-р-и-транзисторов соединены с первыми входами ячейки памяти, введены девятый и десятый п-р-и-транзисторы и седьмой и восьмой р-и-P òðàíçèñòoðû, базы которых соединены с эмиттерами девятого и десято-.î п-р-и-транзисторов с шиной нулевого потенциала, коллек.торы девятого и-р-п òðàíçèñòîðà соединены соответственно с базами первого и второго и-р-и-транзисторов, база девятого и-р-п-транзистора подключена к коллектору седьмого р-п-р-транзистора, эмиттеры которого соединены с базами третьего и четвертого и-p-n-транзисторов соответственно, а их базы соединены со вто-. рыми входами ячейки памяти, коллекторы десятого и-р-и-транзистора соединены со вторыми выходами ячейки па25

65 мяти соответственно, база десятого .n-p-п-транзистора подключена к коллектору восьмого р-п-р-транзистора, эмиттеры которого соединены с базами первого и второго -р-и-транзисторов соответственно.

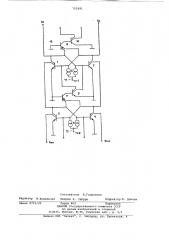

На чертеже представлена электрическая схема предложенной ячейки памяти.

Она содержит первый и второй и-р-и-транзисторы 1, 2, на которых выполнен основной триггер, третий и четвертый 3, 4 п-р-п-транзисторы, на которых выполнен дополнительный триггер, инжекторы 5 и 6, р-и-р-транзисторы 7 и 8, п-р-и-транзисторы 9 и

10Ä тактовые шины 11 и 12, шина 13 нулевого потенциала.

Ячейка памяти работает следующим образом.

При подаче тактового импульса

TH-1 на шину 11 инжектора 5 информация со входа перепишется в основной триггер, выполненный на транзисторах 1 и 2, после окончания тактового импульса ТИ-2. После приема информации на основной триггер и независимо от включения транзистора 1 или 2 основного триггера двухколлекторный и-р-п-транзистор 10 откроется через вторичную инжекцию и замкнет остаточные заряды в предыдущем разряде регистра (на чертеже не показано) с узловых базовых емкостей дополнительного триггера, выполненного íà n-p-и-транзисторах 3 и 4 на шину 13 нулевого потенциала через открытые коллекторы.

После установления информации в основном триггере (транзисторы 1 и 2), она готова к передаче в дополнительный триггер (транзисторы 3 и

4), но информация не будет передана в дополнительный триггер, даже если на шине 12 инжектора 6 дополнительного триггера будет присутствовать тактовый импульс ТИ2, так как обратные связи от основного триггера не позволяют дополнительному триггеру включиться. Вследствие этого не только повышается частота тактового питания за счет снижения накопленных зарядов на узловых базовых емкостях, но и увеличивается надежность работы схемы и помехоустойчивость по тактовому питанию. При присутствии ТИ2 на шине 12 инжектора 6 дополнительного триггера, когда еще не кончился ТИ1 на основном триггере, дополнительный триггер подготовлен к приему информации, но не принимает ее. Прием и включение дополнительного триггера, выполненного на транзисторах 3 и 4, будет не по переднему фронту присутствующего на шине 12 инжектора 6 дополнительного триггера ТИ2, а по заднему фронту окончания тактового импуль7524"-1 са ТИ1 на инжекторе 5 основного триг,гера.

После приема и установки информации в дополнительном триггере и независимо от включения транзистора 3 или 4, двухколлекторный и -р-и-транзистор 9 откроется через вторичную инжекцию и замкнет остаточные заряды с узловых базовых емкостей основного триггера на шину нулевого потенциала 13 через открытые коллекторы, од- 10 новременно заставив основной триггер быть включенным на время присутствия тактового импульса ТИ2 на дополнительном триггере. На это время основной триггер будет не чувствителен по входу, даже если на его шине 11 инжектора 5 будет присутствовать тактовый импульс помехи.

Положительный эффект от применения ячейки памяти для регистра сдвига с инжекционным питанием состоит в простоте изготовления регистра сдвига в одном кристалле со схемами интегральной инжекционной логики, обеспечении высокой степени интеграции на кристалле, минимальном произведении потребляемой мощности на время переключения, изготовлении по технологии биполярных интегральных схем.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая основной триггер, выполненный на первом и втором и-р-и-транзисторах, к базам и первым коллекторам которых подключены выходы первого инжектора, входы первого ин. жектора соединены с первой тактовой шиной, дополнительный триггер, выполненный на третьем и четвертом п-р-п-транзисторах, к базам и первым gg коллекторам которых подсоединены выходы второго инжектора, входы которо го соединены со второй тактовой шиной

f эмиттеры и-р-и-транзисторов соединены с шиной нулевого потенциала, вто-. рые коллекторы первого и второго и-р-и-транзисторов соединены с базами четвертого и третьего и-р-и-транзисторов соответственно, вторые коллекторы третьего и четвертого и-р-и-транзисторов соединены с первыми выходами ячейки памяти, базы перного и второго и-р-и-транзисторов соединены с первыми входами ячейки памяти. отличающаяся тем, что, с целью расширения области применения за счет повышения тактовой частоты и повышения помехоустойчивости, в нее введены девя-.ый и десятый и-р-и-транзисторы и седьмой и восьмой р-п-р-транзисторы, базы которых соединены с змиттерами девятого и десятого и-р-и-транзисторов и с шиной нулевого потенциала, коллекторы девятого и-р-и-транзистора соединены соответственно с базами первого и второго п-р-п-транзисторов, база девятого и-р-и-транзистора подключена к коллектору седьмого р-п-р-транзистора, эмиттеры которого соединены с базами третьего и четвертого и-р-и-транзисторов соответственно, базы последних соединены со вторыми входами ячейки памяти, коллекторы десятого и-р-и-транзистора соединены со вторыми выходами ячейки памяти соответственно, база десятого

n-p-n-транзистора подключена к коллектору восьмого р-п-р-транзистора, змиттеры которого соединены с базами первого и второго n-p-n-транзисторов соответственно.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции Р 2131960, кл.G 11С 19/00, 1973.

2. Патент Франции 9 2284223. кл. G 11C 19/28, 1976 (прототип) .

752491

Заказ 4775/25

Тираж 662 Подписное

ЦНИИПИ Государственного комитеТа СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В.Гордонова

Редактор И.Ковальчук Техред Н. "абурк . Корректор N. Демчик