Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

О Й И- - 4;"- -А-.Н И Е

ИЗОБРЕТЕНИЯ

Союз Соаетскик

Соцналнстнческик

Вес у

<п752495

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б3) Дополнительное к авт. свир-ву— (22) Заявлено 15 . 08. 78 (2! ) 2656735/18-24

С ПРИСОЕДИНЕНИЕМ ЗаЯВКИ Нов (23) Приоритет—

Опубликовано 300780. Бюллетень М 28

{5f)M. Кл.

611 С 27/00

Государственный комитет

СССР по делам изобретений н открытий

{5З) УД) 6 8 1 . 3? 7 . 66 (088. 8}

Дата опубликования описания 030880

Ю.И.Дзибалов, A.È.Kîïîòèëaâ, M.Ã. Ëèòâèíåíêo, A.Т.Лукьянов и В. И. Щербак (72) Авторы изобретения (7 1 ) За яв итель

Казахский ордена Трудового Красного Знамени государственный университет им. С.M.Кирова (54} АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к аналоговой технике и предназначено для использования в точных аналоговых вычислительных и измерительных устрой5 ствах в различных областях науки и техники.

Известны схемы выборки и хранения, построенные на операционных усилителях (ОУ), в которых применяются для повышения точности передачи уровня различные методы коррекции нуля.

Простейшая схема ручной коррекции осуществляется с помощью регулировки делителя напряжения, подключенного к специальным клеммам балансировки нуля ОУ (1) .

Однако величина смещения нулевого уровня испытывает дрейф во времени при изменении напряжения питания, 29 сигнала и температуры., Предлагаемая схема статической коррекции не в состоянии продолжительно обеспечивать точность коррекции нуля. Известна также схема коррекции 25 нуля, в которой предпринята попытка обойти недостатки статического метода. Коррекцию производят путем подключения к инвертирующему входу основного Оу второго ОУ, напряжение. фЦ смещения нуля и дрейф которого согласован с аналогичными параметрами основного ОУ (2) .

Реализация предложенной схемы со пряжена с трудностями отбора ОУ по близким характеристикам .

Наиболее близким иэ известных по технической сущности является устройство выборки и хранения, которое выполнено в виде интегральной схемы (ИС) и представляет собой неинвертирующую схему с единичным усилением, состоящую из двух высокоимпедансных входного и выходного буферных усилителей, соединенных с помощью мостового диодного переключателя P3) .

Диодный мостовой переключатель обеспечивает высокую точность заряда потенциометрического конденсатора, но имеет малый ток заряда. Поэтому в схему включен для форсированного заряда потенциометрического конденсатора дополнительный усилитель., Этот усилитель форсированного заряда отрабатывает разность между выходными напряжениями двух буферных усилителей схемы. Когда это раэностное напряжение превышает определенный

752495 уровень, усилитель форсированного заряда включается и формирует на своем выходе вытекающий и втекающий ток для перезаряда потенциометрического конденсатора. Как только напряжение на этом конденсаторе достигнет своего конечного значения, усилитель форсированного заряда выключается и процесс окончательного заряда конденсатора завершается током диодной мостовой схемы.

Элементов для автоматической дианамической коррекции в ИС не предусмотрено, но имеются выводы для ее проведения. Таким образом с помощью внешних дополнительных элементов можно осуществлять коррекцию нулевого уровня, например по ранее описанному методу.

Применявшийся изготовителями метод коррекции нуля на стабилитронах при испытании дал значение максимальной ошибки установки уровня нуля 1

2,5 MB и величину температурного дрейфа нуля 20 мкВ/"С.

Основным недостатком схемных решений повышения прецизионности в прототипе и аналогах является отсутствие в схемах элементов для компенсации ошибки в передаче уровня при

его выборке, возникающей из-за при" близительно единичного коэффициента буферных усилителей в схемах выборки и хранения.

Целью настоящего изобретения является повышение точности и быстродействия устройства за счет коррекции нулевого уровня напряжения и компенсации ошибки передачи напряжения.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, другая обкладка конденсатора соединена с выходами первого и второго ключей, первый и второй усилители, выходы которых соединены соответственно со входами первого и второго ключей, третий усилитель, выход которого соединен с выходом устройства, вход второго усилителя соединен со входом устройства, введены третий и четвертый ключи, первый и.второй пассивные элементы, соединенные через третий ключ по схеме делителя напряжения, причем один из выводов первого пассивного элемента соединен с другой обкладкой конденсатора и первым входом третьего ключа, другой вывод первого пассивного элемента соединен со входом третьего усилителя и выходом третьего ключа, второй вход которого соединен с первым выводом второго пассивного элемента, второй вывод второго пассивного элемента подключен к его третьему выводу и шине нулевого потенциала, второй вход третье го ключа соединен с первым входом четвертого ключа, второй вход которого соединен со входом устройства. выход четвертого ключа соединен со входом первого усилителя.

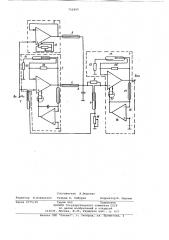

На чертеже изображена функциональная схема предложенного устройства.

Оно содержит усилители 1, 2 и 3, ключи 4-7, накопительный элемент, например конденсатор 8, первый пассивный элемент 9, второй пассивный элемент 10, динамический корректор

11 нулевого уровня третьего усилителя 3, статический корректор 12

15 нулевого уровня второго усилителя 2, ключ 13 усилителя 3, ключ 14 усилителя 1, ключ 15, интегратор 16 и полевой транзистор 17 усилителя 3.

Устройство работает следующим образом.

Из режима хранения устройство переводится в режим форсированного заряда конденсатора 8 и коррекции нуля. При этом замыкаются контакты ключей 5 и 15, а также ключей 6, 7, 13 и 14. Напряжение U поступает на усилитель 3 и через ключ 5 на конденсатор 8 и на делитель напряжения, состоящий из элементов 9, 10 и ключа б.

Часть напряжения сигнала U постуЗО пит на вход усилителей 1 и 3, переведенных ключами 14 и 13 в режим усиления с коэффициентом R„/R

Одновременно, замкнутая через ключ

15, интегратор 16 и полевой транзис35 тор 17, петля обратной связи осуществляет отстройку нулевого уровня усилителей 3, 2 и 1 с учетом напряжения с делителя напряжения, образованного элементами 9, б и 10.

4р С окончанием режима форсированного заряда конденсатора 8 и коррекции нуля ключи 5-7, 13-15 переключаются в нормальное состояние, а ключ 4 замыкается. При этом усилители 3 и 1 переводятся в режим с коэффициентом

45 усиления "1", делитель напряжения, образованный элементами 9, б и 10, исключается из схемы, а найденное напряжение коррекции хранится до следукщег периода в интеграторе 16.

Этими переключениями устройство переводится в режим прецизионной выборки заряда конденсатора 8 через скорректированный усилитель 1.

По окончании прецизионного заряда

55 конденсатора 8 устройство размыканием ключа 4 переводится в режим хранения уровня. В это время скорректированный усилитель 3 может прецизионно передавать хранимый уровень для даль-, нейшего использования.

Возвращение устройства в режим коррекции нуля .соответствует началу очередного периода — режим форсированного заряда конденсаторов и кор65 рекции, режим прецизионной выборки

752495

1О

20 заряда, конденсатора 8 режим хранения и т.д.

Придание новых функций известным усилителю форсированного заряда и элементам динамической коррекции нулевого уровня путем введения делителя напряжения образованного, элементами 9, б и 10 с регулируемым питанием,создающегося на время коррекции и исключающегося из схемы устройства в остальных режимах, позволяет производить простую подстройку нулевого уровня с учетом начального смещения нуля в усилителях и интеграторах, дрейф его величины во времени и ошибки, вносимой реальным усилителем при" повторении уровня напряжения сигнала. В результате повышается прецизионность (точность) работы схемы устройства выборки и хранения, а также ее быстродействие.

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопительный элемент, 25 например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, другая обкладка конденсатора соединена с выходами первого и второго ключей, первый и второй 30 усилители,.выходы которых соединены . соответственно со входами первого и второго ключей, третий уселитель,выход которого соединен с выходом устройства, вход второго усилителя соединен со входом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения точности и быстродействия устройства за счет коррекции нулевого уровня напряжения и компенсации ошибки передачи напряжения, в него введены третий и четвертый ключи, первый и второй пассивные элементы, соединенные через третий ключ по схеме делителя напряжения, причем один из выводов первого пассивного элемента соединен с другой обкладкой конденсатора и первым входом третьего ключа, другой вывод перво" го пассивного элемента соединен со входом третьего усилителя и выходом третьего ключа, второй вход которого соединен с первым выводом второго пассивного элемента, второй вывод второго пассивного элемента подключен к его третьему выводу и шине нулевого потенциала, второй вход третьего ключа соединен с первым входом четвертого ключа, второй вход которого соединен со входом устройства, выход четвертого ключа соединен со входом первого усилителя.

Источники информации, принятые во внимание при экспертизе

1. Рутковски Дж. Интегральные операционные усилители. М., "Мир", 1978 с. 72.

2. "Электроника", 1972, Р 7, c . .58.

3. "Электроника", 1977, 9 21, с. 7б (прототип).

752495

Составитель А.Воронин

Заказ 4775/25 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Редактор И.Ковальчук Техред Н. Бабурка Корректор N. К!ароши