Устройство для защиты блоков памяти

Иллюстрации

Показать всеРеферат

НИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Соцналнстнческих

Республик

«i>752498

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к &$7, саид-ву(22) Заявлено 03; 07. 78 (21) 2639101/18-24 с присоединением заявки М-. (23) Приоритет—

Опубликовано 300780, Бюллетень М 28

Дата опубликования описания 030880 (51)М. Кл.З

G 11 С 29/00

Государственный комитет

СССР по делам иэобретеиий и открытий (53) УДК 681.327.6 (088. 8) (72) Авторы изобретения

М.Н.Бобов, А.А.Обухович и Г.А.Семавин (71) Заявитель (94) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ БЛОКОВ ПАМЯТИ

Изобретение относится к запомина- . ющим устройствам и может быть использовано для защиты блоков памяти.

Известны устройства для защиты блоков памяти $1(.

Наиболее близким к предлагаемому по техническому решению является устройство, содержащее блок регистрации, коммутатор, датчик времени, дешифратор, триггеры и элементы И и ИЛИ, причем первый вход блока регистрации соединен со входом дешифратора, выходы которого подключены к соответсвующим входам коммутатора, выходы коммутатора подключены к соответст» вующим входам триггеров, второй вход блока регистрации подключен к выходу элемента И, входы которого соединены с выходом элемента ИЛИ и с первым выходом датчика времени соответствен-20 но, второй выход датчика времени подключен к третьему входу блока регистрации, а соответствующие входы элемента ИЛИ и датчика времени объединены (2) .

Однако известные устройства не обеспечивают выход на резервные ячейки в случае наличия неисправностей в защищаемых ячейках блоков па° мяти. 30

Цель изобретения — расширение функциональных возможностей путем переключения неисправных ячеек на резервные.

Эта цель достигается тем, что предлагаемое устройство содержит дополнительный дешифратор и дополнительные элементы И и ИЛИ, причем выходы дополнительного дешифратора подключены к соответствующим входам коммутатора, выходы которого подключены к соответствующим входам дополнительных элементов И и ИЛИ, а выходы триггеров подключены к соответствующим входам дополнительных элементов И, выходы которых соединены со входами элементов ИЛИ соответственно, выход дополнительного элемента ИЛИ подключен к четвертому входу регистрации и к одному из входов датчика времени.

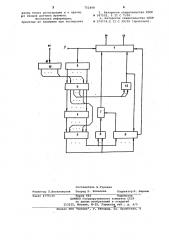

На чертеже представлена блок-схема устройства для защиты блоков памяти.

Устройство содержит блок 1 регистрации, дешифратор 2, коммутатор 3, триггеры 4, дополнительные элементы

5 И, датчик 6"времени„ элемент 7 И, элемент 8 ИЛИ, первый вход 9 устройства, дополнительный дешифратор

752498

10, второй вход 11 устройства, дополнительный элемент 12 ИЛИ, первый выход 13 устройства, второй выход

14 устройства.

Устройство работает следующим образом.

Устройство работает в двух режимах: режиме безаварийного функционирования (сигнал о неисправности яче-, ек не поступает) и режиме аварийного включения (сигнал о неисправности ячеек поступает) .

B н ачальном состоянии производится установка триггеров 4, для чего на шины 9 подаются коды адресов ячеек памяти, подлежащих защите. При этом на соответствующих выходах дешифратора 2 появляются сигналы, которые через коммутатор 3 (первые выходы коммутатора) устанавливают соответствующие триггеры 4 в единичное состояние, подготавливая тем самым срабатывание элементов 5 И. Триггеры 4 в единичном состоянии определяют допуск к соответствующим ячейкам памяти.

Кодовый адрес запрашиваемой ячейки поступает по шине 9 в блок 1 регистрации и дешифратор 2. На соответствующем выходе дешифратора ? появляется сигнал, который через вторые выходы коммутатора 3 поступает на вторые входы элемента 5 И. Если к запрашиваемой ячейке памяти разрешен допуск, то на вход этого элемента

5 И подается разрешающий сигнал с соответствующего триггера 4. Элемент

5 И срабатывает и через элемент 8 ИЛИ открывает элемент 7 И, а также запускает датчик 6 времени. Датчик 6 времени формирует временной интервал, в течение которого разрешается допуск к запрашиваемой ячейке памяти. Этот сигнал через открытый элемент 7 И поступает в блок 1 регистрации, выдающий сигнал разрешения допуска в течение сформированного интервала времени.

В случае, если в процессе выполнения программы вышли из строя одна или несколько ячеек из защищаемой области памяти, то по входной шине 11 на дополнительный дешифратор 10 поступают адреса неисправных ячеек. Дешифратор

10 вырабатывает соответствующий сигнал, поступающий на вторые входы ключевых элементов 3.

В этом случае на третьих выходах кощиутатора 3 появляется сигнал, который подается на входы дополнительного элемента 12 ИЛИ. Выходной сигнал с дополнительного элемента

12 ИЛИ поступает на блок 1 регистрации, в котором происходит регистрация неисправности ячейки по адресу, пришедшему в этот блок по входной шине 9.

По сигналу с выхода дополнительного элемента 12 ИЛИ включается датчик б времени, который выдает стандартный интервал времени для всех неисправных ячеек памяти. Этот интервал времени регистрируется в блоке 1 регистрации.

Сигнал с выходной шины 14 подключает резервные ячейки памяти в течение интервала времени, определенного для обращения к резервным ячейкам памяти.

Таким образом, предлагаемое устройство кроме защиты памяти позволяет переключать неисправные ячейки памяти на резервные. Обращение к резервным ячейкам памяти осуществляется в течение определенного для них ин15 тервала времени, сформированного датчиком интервалов времени.

Использование предлагаемого устройства позволяет сократить объем оборудования в управляющих устройст20 вах ЭВМ за счет устранения необходимости иметь два типа защитных устройств, а именно, устройства для обхода неисправных ячеек памяти и устройства для защиты ячеек памяти от

25 неправомочного к ним обращения. Предлагаемое устройство выполняет обе защитные функции, что расширяет область его применения.

Формула изобретения

Устройство для защиты блоков памяти, содержащее блок регистрации, коммутатор, датчик времени, дешифратор, триггеры и элементы И и ИЛИ, причем первый вход блока регистрации соединен со, входом дешифратора, выходы которого подключены к соответствующим входам коммутатора, выходы ком40 мутатора подключены к соответствующим входам триггеров, второй вход блока регистрации подключен к выходу элемента И, входы которого соединены с выходом элемента ИЛИ и с первым выходом датчика времени соответственно, второй выход датчика времени подключен к третьему входу блока регистрации, а соответствующие входы элемента ИЛИ и датчика времени объединены, о т л и ч а ю щ е е с я тем, то что с целью расширения функциональных возможностей путем переключения неисправных ячеек на резервные, оно содержит дополнительный дешифратор и дополнительные элементы И и ИЛИ, причем выходы дополнительного дешифратора подключены к соответствующим входам коммутатора, выходы которого подключены к соответствующим входам дополнительных элементов И и ИЛИ, а

Щ выходы триггеров подключены к соответствующим входам дополнительных элементов И, выходы которых соединены со входами элементов ИЛИ соответственно, выход дополнительного

65 элемента ИЛИ подключен к четвертому

752498

Составитель В.Гуркина

Редактор Л.Веселовская Техред Н. Ковалева

Корректор М. Шароши

Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4775/25

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 входу блока регистрации и к одному рз входов датчика времени.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 587502, G 11 С 7/00.

2, Авторское свидетельство СССР

У 574774,G 11 С 29/00 (прототип).