Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

1 т нтаб П т::1 си К;ь

4t Г.

ОЙИCAHИЕ

ИЗОБРЕТЕНИЯ

Союз СОВетских

Социапистических

I BCfl 6J1éé

1 752500 (6I ) Дополнительное к авт. свид-ву (22) Заявлено 13.07.78 (2I ) 2646830/1 8-24

3 (5I)M. Кл.

С 11 С 29/00 с присоединением заявки №

Гасударстаеннмй комитет (23) Приоритет (5З) УДК 881,327 (088.8) до делам иаооретений н открытий

Опубликовано 30.07.80. Бюллетень № 28

Дата оптбаииоааиня описания 02.08.80

И, В, Огнев, 10. М. Шамаев, К, Ф. Сарычев и Н. И. Гарбузов (72) Авторы изобретения

Московский ордена Ленина энергетический институт (71) Заявитель

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство с автономным контролем, содержащее накопители, схемы формирования проверочного слова и дешифратор одноразрядных

5 ошибок (LJ.

Недостатком этого. устройства являеэся невозможность обнаружения многоразрядных пакетных ошибок, которые могут

10 возникать при использовании в запомнив ющем устройстве многоразрядных блоков ттамяти ь

Наиболее близким техническим решением и изобретению является запомина15 ющее устройство с автономным контролем, содержащее накопитель, формирова тель контрольных разрядов Хэмминга, формирователи проверочного слова, дешифратор одноразрядных ошибок, блок обнару.жения двукратных ошибок, входные и выходные формирователи четности, причем контрольные . входы накопителя подключены к выходам формирователя контрольных раз2 рядов Хэмминга, информвдионные входы накопителя соединены с входными шинами, которые подключены ко входам входных формирователей !четттости и входам всех формирователей контрольных разрядов Хемминга, за исключением одного, вход которого подключен к выходам входных формирователей четности, выходы накопителя соединены со входами формирователей проверочного слова, выходы которых под ключены к одним из входов дешифратора одноразрядных ошибок и блока обнаружения двукратных ошибок, другие входы кото рых соединены с выходами выходных формирователей четности f2).

Недостатком этого устройства являеъся невозможность обчаружения многоразрядных пакетных ошибок, которые могут возникнуть при использовании многоразрядных блоков памяти, что снижает надежность работы устройства.

Бель изобретения — повышение надежности устройства путем обнаружения многоразрядных пакетных ошибок. (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

3 75250

Поставленная цель достигается тем, что устройство содержит сумматор и эпе;: мент ИЛИ ; входы которого подключены к выходу блока обнаружения двукратных ошибок и выходу сумматора, входы которого соединены с выходами выходных формирователей четности, выходы входных и входы выходных формирователей четнос-, ти подключены соответственно к контроль, Ным входам и выходам накопитепя. р

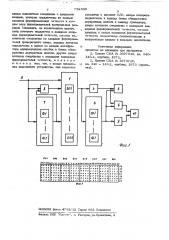

На фиг. 1 изображена блок-схема устройства; на фиг.- 2 — Н-матрица используемого корректирующего кода.

Устройство содержит (фиг. 1) накопитель 1, состоящий из восьми четырехразрядных блоков памяти, формирователи 2 контрольных разрядов Хемминга, входные шины 3, являюшиеся числовыми шинами, формирователи 4 роверочного слова, дешифратор 5 одноразрядных ошибок, блок

6 обнаружения двукратных ошибок, входные 7 и выходные В формирователи четности, сумматор 9 и элемент 10 NJM, Одни контрольные входы накопителя 1 подключены к выходам формирователей 2, а информационные входы накопителя 1 соединены с входными шинами 3, которые подключены также ко входам входных формирователей 7 четности и входам всех формирователей контрольных разрядов Хэм- р минга, за исключением одного, вход которого подключен к выходам формирователей

7, соединенным с другими контрольными входами накопителя 1. Выходы накопителя

1 соединены со входами формирователей

4 проверочного слова и выходных формирователей 8 четности., Выходы формирователей 4 подключены к одним из входов дешифратора 5 одноразрядных ошибок и блока 6 обнаружения двукратных ошибок, 4р друд е входы которых соединены с. выходами формирователей 8. Входы элемент

ИХ1И подключены к выходу блока 6 и выходу сумматора 9, входы которого соеди нОны с выходами формировате JAR 8 в . 45

На фиг, 2 посредством Н-матрицы показана схема подключения числовых входНых шиН 3 K формирователям 2 контроль ных разрядов Хэмминга, входным формирователям. 7 четности, накопителю 1, а также выходов формирователей 2 и 7 к входам накопителя 1 и выходов накопителя 1 к входам формирователей 4 проверочного слова и выходных формирователей

8 четности. Здесь обозначееы разряды 55 чисел БП1..-. БП8, хранящихся в соотвев0

4 ствуюших .блоках накопителя 1, дополнительный контрольный разряд Хэмминга

СО, контрольные разряды Хэмминга С4 -

С6, контрольные разряды C1 ... С3, образуемые входными формирователями 7 четности, информационные разряды

1 ... 25 (столбцы Н-матрицы), дополни тельный разряд проверочного слова бО и разряды проверочного слова б 4 ...56 образуемые формирователями 4, разряды проверочного слова 51 ... 53, образуемые выходными фор мирователя ми 8 четности, Устройство работает следующим образом.

При записи число с входных шин 3 поступает на информационные входы накопителя 1, формирователи 2 контрольных разрядов Хэмминга и входные формирователи 7 четности в соответствии с Н - матрицей (СО, С4 ... С6) . Входные формирователи 7 четности образуют контрольные разряды (Cl ... СЗ,). Контрольные разряды с формирователей 2 и 7 поступают на контрольные входы накопителя 1. При считывании разряды числа из накопителя 1 поступают на формирователи 4 проверочного слова и выходные формирователи 8 четности в соответствии с Н-матрицей. Выходные формирователи 8 четности образуют разряды (Gl .. 53) проверочного слова, которые поступают на дешифратор 5, блок 6 обнаружения двухкратных ошибок и сумматор 9. Разряды (50,54 ...56) проверочного слова с выхода формирователя

4 поступают на дешифратор 5 и блок 6 обнаружения двукратных ошибок.

B табл. 1 представлены значения разрядов проверочного слова.

Количество блоков памяти, составляющих контролируемый накопитель 1, в которых могут быть обнаружены пакетные ошибки, в зависимости от разрядности блоков и числа контрольных разрядов приведено в табл. 2.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно практически исключает возможность появления необнаруживаемых ошибок, позволяя исправлять одноразрядные ошибки и обнаруживать все двукратные и пакетные ошибки в блоках памяти, при незначительном повышении затрат оборудования, что существенно повышает надежность работы запоминающих устройств с автономным контролем.

752500

Таблица 1

Ошибки нет

Номер отказавшего разряда на выходе дешифратора 5

Любое значение Не более одной

У 1Р

Не менее одной ю 1 Ф

Любое значе0 ние

Сигнал пакетной ошибки нечетной

Любое значе- Не менее двух ние 1"

Та бл ица 2

8 4 2 1

16 8 4 2 1

32 16 8 4 2 1

64 32 16 8 4 2 1

128 64 32 16 8 4 2 1

256 128 64 32 16 8 4 2 1 дешифратор одноразрядных ошибок> блок обнаружения двукратных ошибок, вхсдные

g вы;ходные формирователи четности, при-» чем контрольные входы накопителя подключены к выходам формирователя контрольных разрядов Хэмминга, информационные

Формула изобретения

Запоминакнпее устройство с автоном 55 ным контролем, содержашее накопитель, формирователь контрольных разрядов Хэм минга, формирователи проверочного слова, Сигнал двукратной или пакетной ошибки четной разрядности на выходе блока 6.

Сигнал неисправляемой ошибки на выходе элемента ИЛИ

10. разрядности на выходе сумматора 9.

Сигнал неисправляемой ошибки на выходе элемента ИЛИ

7 52500 бГГГ ЯГЦ ФГго 504 бМО бОО БОГ 6ОО

odcrdJedgg о о $ о г g d rdckrrrtrsrk

О0 О0 ее ее

Фо er оо го

Ф lee

lrrl

o0ed гггг

O OOl оогФ

Е lee

Г Г l ееос

Г ГГГ

О de 0 оо Or о ого

Ф lee

ГГГГ

ГГ ll

0 000 г г гг о оог

00 Го

ГО 0 г г г гг гг

rrrr

00 О 0 ооог

ОО Го о leo гггг

f 5

5О

SS

5с

5r

0 00 гггг гггг ооог о ого

ОГ Оо гг гг ггг

Р 000

О 000

OO Ю Г

ООГ0

О Г 00

l lГ гrr г

rrrr

rrr r

00 о Г оа le огоо

lr lr

ЦНИИПИ Заказ 47 53/12 Тираж 662 Подписное

Филиал ППП Пат нт", г. Ужгород, ул. Проектная, 4 входы накопителя соединены с входными шинами, которые подключены ко входам входных формирователей четности и входам всех формирователей контрольных разрядов Хэмминга, за исключением одного, 5 вход которого подключен к выходам входных формирователвй четности BbIxollM 88 ко ителя соединены со входами формирова.телей проверочного слова, выходы которых подключены к одиим из входов дешифра- >о тора одноразрядных-Ошибок и блока обнаружения двукратных ошибок, другие входы которых соединены с выходами выходных формироватеизй четности,:, о т л и ч аю щ е е с я тем, что, с нелью повыше- Is ния надежности устройства, оно содержит

8 сумматор и элемент ИЛИ, входы котороуо юдключены к выходу блока обнаружения двукратных ошибок и выходу сумматора, входы которого соединены с выходами выходных форькрователей четности, выходы входных и входы выходных формирователей четности подключены соответственно к контрольным входам и выходам накопителя.

Источники ив ормшщи, принятые во внимавие щзи экспертизе

1. - Патент США Мо 3697949, кл. 340146 1, опублик. 1971.

2..Патент США _#_ 3573728, кл. 340 - 146.1, опублик. 1970 (прототип).