Устройство для контроля двухпроводных запоминающих матриц

Иллюстрации

Показать всеРеферат

Союз Советски к

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

r»> 752503 (6! ) Дополнительное к авт. свил-ву(51) M. Кл. (22) Заявлено 10.07.78 (2l ) 2652940/18-24

Ст 11 С 29/00 с присоединением заявки ¹вЂ”

Государственный комитет (23) Приоритет— до делам изобретений и открытий

Опубликовано 30,07.80. Бюллетень № 28

Дата опубликования описания 02.08.80 (53) УДК 681.827 (088. 8) (72) Авторы изобретения

Н. П. Епихин и К, Ф. Сарычев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВУХПРОВОДНЫХ

ЗАПОМИНАЮШИХ МАТРИЦ

Изобретение относится к запоминающим устройствам и может быть использовано в испытательной аппаратуре для проверки магнитных запоминающих устройств.

Одно из известных устройсв предна:-ьначено для проверки магнитных запоминающих устройств с совмещенной обмоткой запрета-считывания и содержит согласутощий трансформатор, усилитель воспроизведения и формирователи токов выборки.

Совмещенные обмотки магнитного запоми10 нающего устройства включаются по мостовой схеме и подсоединяются ко входу усилителя воспроизведения через согласующий трансформатор, к каждой паре

15 совмещенньгх обмоток, образующих плечи моста, подключается свой формирователь тока выборки (11

- Недостатком этого устройства являел ся невозможность проверки двухпроводных о матриц.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля двухпроводных запоминающих матриц, со- держащее блок управления, выходы которого подключены соответственно ко входам блоков выборки запоминающих элементов по каждой. координате и блоку считывания информации, выход которого соединен со входом блока управления (2).

Недостатками этого устройства являются ненадежность контроля двухпроводных матриц с возвратным разрядным проводом при некоторых видах неисправностей в матрице, а также наличие формирователя полного тока чтения и полутока записи по адресному проводу и отсутствие диодного матричного переключателя для выборки разрядного провода, что увеличивает количество электронного оборудования и усложняет устройство.

Цель изобретения - упрощение устройства за счет уменьшения количества электронного оборудования и расширение, возможностей устройства при выявлении неисправностей двухпроводных запоминающих матриц.

3 752503 4 управления, Каждая из первичных обмоток трансформатора Тр одним выводом соединена с выходом одного из формирователей

6 полутоков выборки по одной из координат, а другим выводом, через разделитель ный элемент Д5 (или Д6) подключена к выходу другого формирователя 6 полутоков по той же координате. Вторичная обмотка трансформатора Тр одним выводом и подключена через дифференцируюший элемент С к первому входу дифференциалн нсн о усилителя 9 считывания и другим выводом соединена со вторым входом усилителя 9, параллельно первому и второ 5 му входам которого встречно включены элементы с нелинейной вольтамперной характеристикой и l16 и lj,7. При этом цел есо об разно входы формирователя 6 полутоков выборки по каждой координате соединить со входами блока выборки зепоминакших элементов, а выходы — со входами диодного матричного переключателя 7, выходы которого соединены с выходами устройстУстройство работает следуюшим образом.

Поставленная цель достигается тем, что в устройстве блок считывания информации содержит дифференциальный усилитель считывания и разделительный трансформатор, каждая из первичных обмоток которого одним выводом соединена с выходом из формирователей полутоков выборки, е другим выводом через разделительный элемент подключена к выходу другого формирователя полутоков выборки, а вторичная обмотка разделительного трансформатора одним выводом подключена. через дифференцируюший элемент к первому входу дифференциального усилителя считывания и другим выводом соединена со вторым входом дифференциального усилителя считывания, параллельно первому и второму входам которого встречно включены элементы с нелинейной вольч амперной характеристикой, третий вход и выход дифференциального усилителя считывания соединены соответственно со входом и выходом блока считывания информации, 25

При этом целесообразно выполнить блок выборки зепоминаюшихэлементов по каждой

:-..о ".ипате содержащим формирователь полутоков BbIGopKH, входы которых соединены со входами блока выборки запоминаюших

S0 элементов, е выходы — со входами диодного матричного переключателя, выходы которого соединены с выходами устройства.

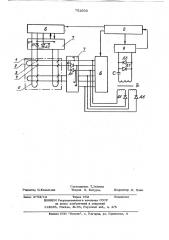

На чертеже изображена блок-схема пс;эдложенного уст ойстве, 35 устройство coDGpiKHT числовой IIpoBQJ1

1, разрядный провод 2, сердечники 3 и

4 указаны не схеме двухпроводной матрицы 5, подключенной ко входам устройства, Устройство содержит блоки выборки запоминеюших элементов, состояшие из формирователей 6 полутоков выборки и диодных матричных переключателей 7с разделительными элементами, например диодами Gl и Д2 по одной координате и ДЗ и lj,4 по другой координате, блок

8 управления и блок считывания информации, содержаший дифференциальный усилитель 9 воспроизведен я, разделительный трансформатор Тр, разделительные эле50 менты Д5 и Д6, элементы с нелинейной вольтам перной характеристикой, например диоды Д7 и Д8 и дифференцируюший элем ент, например конденсатор С.

Выходы блока 8 управления подключены соответственно ко входам блоков выборки запоминаюших элементов и входу дифференциального усилителя 9 считывания, выход которого соединен со входом блока 8

Блок управления вырабатывает сигналы, возбуждаюшие формирователи 6 полутоков выборки, подключенные через диодный матричный переклкчетель 7 к обмоткам

1 и 2, осушествляюшие сначала запись, а затем чтение "1", например в сердечнике 3, При записи информации возбуждаются формирователи 6 полутоков и открываются разделительные элементы Д1 и Д3.

На сердечнике 3 действует сумма полутоков по двум координатам; и онперемагничивает ся в состояние 1" ° При этом на сердечник 4 действует разность полутоков, сердечник 4 своего состояния не меняет, При чтении информации из сердечника

3 направление обоих полутоков меняется на противоположное. Элементы Дl и Д3 запираются, элементы Д2 и Q4 отпирают ся, На сердечник 3 действует сумма считываюших полутоков, При этом полуток в обмотке 1 задержан относительно полутока в обмотке 2 на время успокоения переходных процессов от воздействия фронта в обмотке 2 на входе усилителя

9. На сердечник 4 действует разность полутоков, и сердечник 4 состояние не меняет, Считанный с сердечника 3 сигнал ч рез разделительнь и трансформатор ТР, служаший также для подавления сиифазной помехи, поступает на пифференцируюший элемент С, служаший для выделения

503 б прототипом, что значительно упрощает устройство.

Ф орму ла изобретения

1. Устройство для контроля двухпроводных запоминающих матриц, содержашее блок управления, вь.ходь. которого подключены соответственно К0 входам блоков выборки запоминающих элементов по каждой координате и блоку считывания информации, выход которого соединен со входом блока управления, о т л и ч а ю щ е е с я тем что с целью упрощения устройства, в нем блок считывания информации содержит дифференциал ьны и ус илител ь считывания и разделительный трансформатор, каждая из первичных обмоток которого одним вы,— водом соединена с выходом одного из формирователей полутоков выборки, а другим выводом через разделительный элемент подключена к выходу другого формирователя полутоков выборки, а вторичная обмотка разделительного трансформатора одним выводом подключена через дифференцируюший элемент к первому входу дифференциального усилителя считывания и другил< выводом сое динена со вторым в ходом дифференциал ьн ого усилителя считывания, параллельно первому и второму входам которого встречно включе. ны элел енты с нелинейной вольтамперной характеристикой, третий вход и выход дифференциального усилителя считывания соединены соответственно со входом и выходом блока считывания информации.

2. Устройство для контроля двухпроводных запоминающих матриц по п.1, о т л и—

1 ч а ю ш е е с я тем, что в нем по каждой координате содержится формирователь полутоков выборки, входы которых соединены со входами блока выборки запоминающих эл ментов, а выходы — со входами диодного матричного переключателя, выходы которого соединены с выходами устройства, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N402068, кл. Q 11С 29/00, 1971

2. Крупский А.А„Татур В.Е. Аппаратура для контроля элементов, узлов и устройств памяти 31IBN (отчет), М, 1967, с. 101 (прототип).

5 752 быстро меняющегося на фоне медленно меняющейся помехи от вершины полутока в координатном проводе 2, Дифференциро\ванный сигнал с элемента С поступает на вход усилителя 9 считывания. Элементь: Д7 и Д8 служат для защиты усилителя 9 считывания от выбросов на фронтах тока в обмотке 2. Во время появления счиганного сигнала элементы

Д7 и Д8 запергы, Элементы Д5 и Д6 препятствуют шунтированию возбужденной обмотки 2 невозбужденными обмотками, подключенными к другим первичным об моткам трансформатора.

Если с сердечника 3 считывается сигнал 15

"1", то блок 8 управления организует запись "1 и чтение в сердечнике 4, Если с сердечника 3 нет сигнала, то блок 8 управления останавливает проверку с индикацией неисправного сердечника. 20

Запись и чтение информации при проверке сердечника 4 отличается от рассмотренного случая направлением полутока в обмотке 1. Далее блок 8 управления организует проверку остальных сердечников матрицы.

Технико экономические преимушества описываемого устройства заключаются в том, что оно позволяет проверять двухпроводные запоминающие матрицы, один из проводов . которых возвратный и сердечники в которых одинаково ориентированы и расположены на каждом пересечении обоих координатных про водов, и выявляет неисправность, когда раско лоты илиобойдены прошивкой один, два или Ç5 более сердечников, независимо с г их расположения в матрице, что значительно расширяет возможности устройства по сравнению и прототипом.

Кроме того, применение диодных мат- ричных переключателей выборки по обоим координатам позволяет сократить количество формирователей полутока1 применение многообмоточных разделительных трансформаторов позволяет сократить количество усилителей считывания пропорционально числу первичных обмоток трансформатора, а отсутствие формирователей полного тока выборки также сокращает количество электронного оборудования по сравнению с 0

752503

С оставитель Т.Зайцева

Техред Н. Бабурка

Редактор И.Коваль шк

Корректор М. Пожо

Подписное

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4

Заказ 4753/12 Тираж 662

ЫНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауиская наб., д. 4/5