Универсальный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«»752793

Ф

Ф (63) Дополнительное к авт. свид-ву— (22) Заявлено 280778 (21) 2670991/18-21 с присоединением заявки ¹â€” (23) Приоритет

Опубликовано 300780, Бюллетень ¹ 28 (53)М. Кл з

Н 03 К 13/17

Государственный комитет

СССР но делам изобретений и открытий (53) УДК681.325 (088. 8) Дата опубликования описания 30,07.80 (72) Авторы изобретения

В.П.Школин, С.Ф.Михайлов, Ю.П.Орлов и И.Г.Солдатов (71) Заявитель (54) УНИВЕРСАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычисли. тельной технике и может быть использовано для построения универсальных аналого-цифровых комплексов сбора 5 и обработки первичной информации °

Известен универсальный аналогоцифровой преобразонатель, содержащий компараторный коммутатор, первые входы которого соединены со входными клеммами преобразователя,.вторые входы — c выходом преобразователя кода в напряжение, входы разрядов которо" го соединены с выходами счетчика,и генератор импульсов Pl) .

Недостатком устройства является отсутствие воэможности обработки сигналов переменного напряжения при различных частотах и их девиации.

Цель изобретения — расширенйе функциональных воэможностей.

Поставленная цель достигается тем, что в универсальный аналогоцифровой преобразователь, содержащий компараторный коммутатор, первые входы которого соединены со входными клеммами преобразователя, вторые входы — с выходом преобразонателя кода в напряжение, входы разрядов которого соединены с выхо- З() дами счетчика генератора импульсов, введены регистр адреса, дешифратор, генератор одиночного импульса, -В триггер, дна блока элементов И-ИЛИ, элементы И,ИЛИ, И-НЕ, дна иннертора, три 7 †триггера и дополнительный счетчик, причем выходы компараторного коммутатора соединены с первыми входами первого блока элементов

И-ИЛИ, вторые входы которого соединены с выходами дешифратора и входами первого элемента ИЛИ, выход кото рого подключен к первому входу элемента И-НЕ, первому входу первого— элемента И и через первый инверторк первому входу второго блока элементов И-ИЛИ, второй вход последнего соединен с выходом генератора импульсов, первым входом второго элемента

И, первым входом третьего элемента И, третьим входом второго блока элементов И-ИЛИ, четвертый вход которого соединен с выходом генератора одиночного импульса, первым входом первого

J - K триггера, вторым входом второго элемента И, перным входом дополнительного счетчика, второй вход последнего соединен с выходом второ-, го блока элементов И-ИЛИ, пятый вход

752793

tcoeegera соединен с выходом второго

3 - К триггера, первый вход которого подключен к,выходу второго элемента

И, вас рой вход — к третьему входу дополнительного счетчика, первому входу третьего 3 -К триггера, шине Приенан адреса первому входу

R-Á — триггера, первому входу счетчика, вворай вход которого соединен с выходом третьего элемента И, а третий вход — c вторым входом элемента

М-НЕ,первым входом генератора одиночного импульса и выходом первого блока элементов И-ИЛИ, второй вход первого элемента И соединен с шиной Признак адреса, а выход подключен. ко второму входу первого 3- V триггера, выход которого соединен со вторым входом третьего элемента И и шестым входом второго блока элементов И-ИЛИ, третий вход третьего элемента И соединен с выходом элемента

И-HE и через второй инвертор подключен к первому входу второго элемента ИЛИ, второй вход последнего соединен с первым выходом К - б триггера, а выход — c вторым входом третьего

3 - К триггера, и третьим входом первого 3-К триггера, второй выход Й-б триггера соединен с четвертым входом третьего элемента И, а вход дешифратора соединен с выходом регистра адреса, входы которого соединены соответственно с шинами Признак адреса и 1(од адреса .

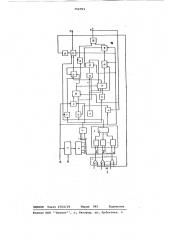

На чертеже схематически изображено устройство.

Универсальный аналого-цифровой преобразователь содержит компараторный коммутатор 1, регистр 2 адреса, дешифратор 3, блок 4 элементов И-ИЛИ„ элемент 5 ИЛИ, Э-К триггер 6, элемент И-HE 7, генератор 8 одиночного импульса, генератор 9 импульсов, 3- К триггер 10, элементы 11, 12 И, блок 13 элементов И-ИЛИ, 3- К триггер 14, элемент 15 И, преобразователь 16 Код -напряжение, реверсивный счетчик 17, реверсивный дополнительный счетчик 18 Ч-5 триг-, гер 19, элемент 20 ИЛИ, инвертор 21

НЕ, магистраль 22 информации, шину 23 Признак информации, шину 24 Признак адреса, шину 25 Кодаадреса, шину 26 аналоговых каналов, инвертор 27 НЕ.

Устройство работает следующим образом.

С приходом сигналов Признак-адреса и Код адреса по шинам 24 и 25 дешифратор 3 подключает выходы компараторного. коммутатора 1 к блоку

4 элементов H-ИЛИ, устанавливаются в нулевое состояние триггеры 14, 19, счетчики 17, 18 ° Выходы дешифратора

3, соответствующие коду каналов постоянного напряжения, поданы на элемент 5 ИЛИ, выход которого подготавливает к работе элемент 7 И-НЕ, и

16

2О

55 бО выход инвертора 27 отключает прохождение серии импульсов с выхода генератора 9 импульсов через блок 13 элементов И-ИЛИ, на дополнительный счетчик 18. Высокие уровни с выхода элемента 5 ИЛИ и сигнал с шины 24 проходят элемент 11 И и до входу устанавливают триггер 10 в единицу.

По заднему фронту импульса Признак адреса генератора 9импульсов сигнал проходит элемент 15 И. Подсчет импульсов на счетчике 17 происходит до момента сравнения на выбранном компараторе входного и эталонного набора напряжений. При равенстве их на выбранном компараторе возникает высокий уровень, который проходит блок 4 элементов И-ИЛИ,элемент 7

И-НЕ вырабатывает низкий уровень, запирающий элемент 15 И. Инвертор

21 подает высокий уровень через элемент 20 ИЛИ на шину ?3, по которому организуется сигнал Признак информации,устанавливающий в исходные ,состояния триггеры 6 и 10,а также разрешающий процесс обмена с IU3N информацией, полученной на счетчике 17.

При подключении каналов переменного напряжения на выходе элемента

5 ИЛИ возникает низкий уровень, который подготавливает к работе элемент 15 И, подавая на один из его четырех входов высокий уровень элемента 7 И-HE. Проходя инвертор 27, этот сигнал высоким уровнем подается на блок 13 элементов И-ИЛИ. Далее устройство находится в ожидании срабатывания выбранного компаратора при сравнении нулевого уровня напряжения выхода преобразователя 16 Код-напряжение с переходом нулевого состояния переменным напряжением на входе компараторного коммутатора 1 из области положительного значения в область отрицательных значений. Предварительно задним фронтом импульса Признак адреса (шина 24) взводится в единичное положение 3 - К триггер б. При сравнении нулевых уровней измеряемого и эталонного напряжений блок 4 элементов И-ИЛИ подает высокий потенциал с выхода блока 1 на вход генератора 8 одиночного импульса. Высокий уровень, появляющийся на выходе последнего, открывает элемент

12 И и серия импульсов с выхода генератора 9 импульсов, делясь на два на 3- K триггере 14, подается на вход блока 13 элементов И-ИЛИ. Высокий уровень с выхода генератора 8 поступает на блок 13 И-ИЛИ, а также запускает реверсивный счетчик 18 в . режим счета (сложения) импульсов.

Заполнение счетчика 18 продолжается в течение отрицательного полупериода входного напряжения. Переход нулевой точки входного переменного напряжения вызывает отключение блока 4 элементов И-ИЛИ по реакции

752793 компараторного коммутатора 1, сброс в 0 генератора 8, переключение серии импульсов генератора 9 импульсов с делителя (3-К триггера 14) навход блока 13 элементов И-ИЛИ, установку 3 - К триггера 10 в 1 . 3oполнительный счетчик 18 работает в режиме вычитания частоты серии импульсов с выхода генератора 9. Счетчик 17 работает в следующем режиме при положительной полуволне входного сигнала. Обнуление счетчика 18 происходит в момент прохождения входным сигналом максимального значения. Сигнал обнуления на выходе счетчика 18 установлен R- 6 тРиггер 19 в 1, сигнал с нулевого плеча которого перекроет элемент 15 И, счетчик 17 хранит кодовый набор, соответствующий максимуму входного напряжения.

Высокий уровень с единичного плеча

К -5 триггера 19 пройдет элемент

20 ИЛИ и является Признаком информации,на шине 23. Этот сигнал обнуляет триггеры 6 и 10, Формула изобретения

Универсальный аналого-цифровой преобразователь, содержащий компа- . раторный коммутатор, первые входы ЗО которого соединены со входными клеммами преобразователя, вторые входыс выходом преобразователя кода в напряжение, входы разрядов которого соединены с выходами счетчика, гене- З5 ратор импульсов,о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных возможностей, в него введены регистр адреса, дешифратор, генератор одиночного импульса, Ч-5 щ триггер, два блока элементов И-ИЛИ, элементы И, ИЛИ, И-НЕ, два инвертора, три 3-К триггера и дополнительный счетчик, причем выходы компараторного коммутатора соединены с первыми входами первого блока элементов И-ИЛИ, вторые входы которого соединены с выходами дешифратора и входами первого элемента ИЛИ, выход которого подключен к первому входу элемента И-НЕ, первому входу первого элемента И и через первый инвертор — к первому входу второго блока элементов И-ИЛИ, второй вход последнего соединен с выходом генератора импульсов, первым входом второго элемента И, первым входом третьего элемента И, третьим входом второго блока элементов И-ИЛИ, чет- вертый вход которого соединен с выходом генератора одиночного импульса, первым входом первого Э -К триггера, вторым входом второго элемента И, первым входом дополнительного счетчика, второй вход,последнего соединен с выходом второго блока элементов И-ИЛИ,пятый вход которого соединен с выходом второго 3 - К триггера, первый вход которого подключен к выходу второго элемента И, второй вход — к третьему входу дополнительного счетчика, первому входу третьего 3 -К триггера, шине Признак адреса, первому входу Р-Ь триггера, первому входу счетчика, второй вход которого соединен с выходом третьего элемента И, а третий вход— с вторым входом элемента И-НЕ, первым вход м генератора одиночного импульса и выходом первого блока элементов И-ИЛИ, второй вход первого элемента И соединен с шиной Признак адреса, а выход подключен ко второму входу первого - К триггера, выход кЬторого соединен со вторым входом третьего элемента И и шестым входом второго блока элементов И-ИЛИ, третий вход третьего элемента И соединен с выходом элемента

И-НЕ и через второй инвертор подключен к первому входу второго элемента ИЛИ, второй вход последнего соединен с первым выходом R -5 триггера, а выход — co вторым входом третьего 7 -K триггера и третьим входом первого 3-K триггера, второй выход

Ч-Ь триггера соединен с четвертым входом третьего элемента И, а вход дешифратора соединен с выходом регистра адреса, входы которого соединены соответственно с шинами Признак адреса и Код адреса °

Источники информации, принятые во внимание при экспертизе

1. Дроздов А.П. и др. Электронные цифрбвые вычислительные машины, 1968, с. 510-511 (прототип) °