Резервированный делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1 ) 752809 (б1) Дополнительное к авт. свид-ву 499672 (22) Заявлено 2401.78 (21) 2572476/18-21 с присоединением заявки ¹ (23) Приоритет (51)М. Кл.

Н 03 К 21/34

Государственный комитет

СССР по делам изобретений и откр ыти й

Опубликовано 300780. Бюллетень М9 28 (53) УДК 621 374,44 (088.8) Дата опубликования описания 300780 (72) Авторы изобретения

И.A.Íoâèêoí и A.A,Øåáàíoâ (71) Заявитель (54) РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к электронным цифровым системам с резервированием и может быть использовано в качестве хранителя времени в сочетании с высокостабильным генератором. 5

По основному авт.св, 9 499672 известен резервированный делитель частоты, содержащий два канала деления, каждый из которых состоит из делителя частоты, схемы контроля и элемента памяти, причем входы элемента памяти каждого канала подключены к выходам схемы контроля, а выход — ко входу схемы контроля и входу установки де)тителя частоты, выход которого 15 соединен со входом элемента памяти другого канала деления. Схема контроля включает в себя контрольный делитель частоты и выходную логическую схе (ту (1) . 20

Дпя эффективности контроля исправности делителя частоты, входящего в . состав контроля, делают взаимно простым по отношению к коэффициенту деле-25 ния основного делителя частоты. При этом, если оба делителя перед качалом. работы устанавливаются в нулевое состояние, то при появлении на выходе основного делителя частоты вы- 30 ходкого импульса на контрольном делителе зафиксируется состояние, зависящее от соотношения коэффициентов деления основного и контрольного делителей частоты. С помощью выходной схемы контрольного делителя частоты импульсов с основного делителя. частоты спрашивается это состояние и формируется сигнал, свидетельствующий об исправной работе канала. Для того, чтобы на следующем цикле деления, т.е. при появлении следующего импульса с выхода основного делителя частоты, было зафиксировано то же состояние, необходимо, чтобы следующий цикл деления начинался снова при нулевых состояниях основно=а и контрольного делителей частоты. Следовательно, за один период частоты вход входного сигнала по импульсу с выхода основного делителя частоты необходимо осущес твл я ть и опрос с ос то яния контрольного делителя частоты, и сброс его в исходное состояние. Это накладывает ограничение сверху на частоту входного сигнала при заданном быстродействии элементной базы и требует построения сложных схем сброса контрольных делителей частоты, включающих в себя дифференцирующие

752809 цепи, элементы "-адержки и логические схе>.ы, Цель изобретения — повышение быстродейс=ви я, Цель достигается тем, что в рез ервированном делителе частоты, содержащем два канала деления, каждый из которых состоит из делителя частоты, схемы контроля и элемен — à памяти, в каждый канал деления введен элемент . запрета, первый вход которого подключен к входной шине, второй вход— к выходу делителя частоты, а выход— ко входу схемы контроля.

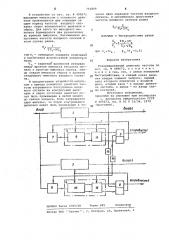

На чертеже представлена структурная схема резервированного делителя частоты, Делитель состоит из делителей 1 и

2 частоты, схем 3 и 4 контроля, элементов 5 и б памяти, элементов 7 и 8 запрета, контрольных делителей 9 и 10 частоты„ выходных схем 11 и 12, элементов 13 "и 14 задержки.

Вхадн B я последов атель ность импульсов поступает на входы делителей 1 и

2 частоты и через элементы 7 и 8 запрета на входы контрольных делителей

9 и 10 частоты и схем 3 и 4 контроля, Выходы делителей 1 и 2 частоты соединены соответственно " входами выходных схем 11 и 12, схем 3 и 4 контроля и входами элементов 7 к 8 запрета свое-о канала деления и с входами элементов 5 и б памяти другого канала деления„ Выходы контрольных делителей 9 и 10 соединень". соответственна со эх;.дами в:-1хадных cxe>- и 12 и элементов 13 и 14 эадер>кки, выходы схем 11 и 12 соединены са входами эле;:e.:.;то= 5 и 6 памяти ка:кдага канала чер - элементы ° 3 и 14 задер>кки. Выходы элементов 5 и 6 памяти соединены соответственна "o входами делителей 1 и 2 частоты и элеменьав

3 и 4 контроля, Резервированный делитель частоты работает следующим Образом.

Поскольк Оба какала работают аналогично, рассмстрим оабату адногс, ка.нала„ Входная последовательность импульcoB пОстpпает на вхОд делителя

1 acтаты и через элемент 7 эапр=-.=:а на вход контрольного делителя 9, Импульс с выхода делителя 1 "-;астаты поступает на вход выходной схемы ll и вход элемента 7 запрета, На другие входы выходной схемы 11 поступают

СИГ !cglbI С РаЗРЯДОВ КОНТРОЛЬНОГО ДЗлителя 9. Еслй на момент прихода импульса с выхода делителя частоты выходная схема i i фиксирует требуемое, состояние кантральчога дели— теля 9 частоты, раьнае остатку ат деления основного делителя на коэф-фициент,деления контра>.ьнаго делителя,.та на выходе выходной схемы ll вырабатываются сигналы, подтверждающие состояние элемента 5 памяти, oooTíåòñòàóþùèå исправной работе данного канала деления. Элемент 7 запрета при поступлении импульса с выхода делителя 1 частоты запрещает поступление импульсов входного сигнала на вход контрольного делителя

9 частоты. Число запрещенных импульсов соответствует состоянию контрольного делителя 9, фиксируемому

npv исправной работе. Запрет такого числа импульсов эквивалентен установке контрольного делителя 9 частоты в исходное состояние. Следующий цикл деления протекает аналогично. Если на момент прихода импульса с выхода делителя 1 частоты на вход схемы 11

15 фиксируется состояние контрольного делителя 9, отличное от требуемого, то ча выходе выходной схемы 11 появляются сигналы, устанавливающие элеме".т 5 памяти в состояние, соответ20 ствующее неисправной работе данного канала, При =òîì сигнал с выхода элемента 5 памяти устанавливает делитель 1 частоты и контрольный делитель 9 ча""ò"".îòû в исходное состояние и держит их в этом состоянии (делители останавливаются) . Если второй канал исправен„ та сигнал с выхода делителя 2 частоты устанавливает элемент 5 памяти в состояние, соответстьующее исправному состоянию своего канала, сигнал на выходе элемента 5 исчезает и первый канал деления начинает рабаты>ть синфазкО СО ВToptB"I °

При сбсе второго какала процесс коррекп:..и протекает аналогична.

Пример. Пусть коэффициенты де ени". Осковнога и кантрольнога делителей 1 и 9 частоты равны, соответственна, 1000000 и 13. В этом случае состо-ние, фиксируемое в конт4О рольнам делителе 9 частоты, равна 1, Оно вычисляется как остаток ат,целения коэффициента деления оскавнога делителя 1 частоты на коэффициент деления контрольнага делителя 9 частоты, Следовательно, схема 7 эа рета должна осуществлять запрет одного ", nóë ое при подаче сигнала с выхода делителя 1 частоты 7. В этом случ:=е схема эапрета реализуется о -использованием адно-o J K-триггера, На вход >-триггера подается сигнал с выхода аснавнага делителя, на ьход Х вЂ” входной сигнал, С инверсного выхода триггера снимается сигнал запрета, кстарый поступает на йходы .):-:1 Х первого триггера контрольного делителя, Такая схема обеспечивает заир.= одного импульса входного сигнала при появлении.имйульса на входе оснавнога делителя, Введение схе69 мы-загрета позволяет исключить операцию сброса контрольных делителей частоты в каждом .цикле деления, что позволяет повысить быстродействие устройства и исключить схемы сброса контрольных делителей, 752809

/Ь„=3,33

Формула из обре тени я

Ймй

Усп х) Й)) сВ ) г

Подписное

Тираж 995

ЦНИИПИ Заказ 4765/20

Филиал ППП Патент, r ужгород, ул, Проектная, 4

В устройстве по авт, св, Р 499672 выходным импульсам с основного дели,теля производится две операции за один период частоты входного сигнала: опрос контрольного делителя и сброс. Для этого из выходного импульса формируется два разнесенных во времени импульса. Максимально допустимая частота входного сигнала в этом случае равна. где w< — суммарная задержка включения и выключения используемой элементной базы;

" — защитный временной интервал между фронтом импульса входного сигнала и фронтом импульса опроса„ между спадом импульса сброса и фронтом следующего импульса входного сигнала.

В предлагаемом устройстве импульсом с выхода основного делителя частоты запрещается поступление входного сигнала на контрольный делитель и опрос состояния делителя может быть произведен в любой момент до снятия запрета. Если запрещается один импульс, то опрос контрольного делителя может быть произведен в течение двух периодов частоты входного сигнала, и максимально допустимая частота входного си гнала рави а

Выигрыш в быстродействии равен

2 )+ у — =2

Резервированный делитель частоты по авт ° св, 9 499672, от ли ч аю шийся тем, что, с целью повышения быстродействия, в каждый канал деления введен элемент запрета, первый вход которого подключен к входной шине, второй вход — к выходу делителя частоты, а выход — ко входу схемы к Он т po Jt я .

Источники информации, принятые во внимание при экспертизе

1. Лвтсрское свидетельство СССР

Р 499672, кл, Н 03 К 2l,/34, 1974 (прототип) .