Устройство для управления т-фазным тиристорным инвертором

Иллюстрации

Показать всеРеферат

< 1,758470

Союз Советских

Социалистических

Республик

ОПИСЛНИЕ изовеитиния

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 15.08.78 (21) 2653372/24 07 (51)М. Кл.

Н 02 P 13/18 с присоединением заявки М

Гооударствоииый комитет (2;3) Приоритет— по долам изобретений и открытий

Опубликовано 23.08,80. Бюллетень Лв 31

Дата опубликования описания 23.08.80, (53) УЛ К 621.314. .5 72 (088.8) (72) Авторы изобретения

А. Г. Азаров, С. И. Королев, В. В. Полонский и Г. И. Цветков

Научно-исследовательский институт автоматики и электромеханики при Томском институте автоматизированных систем управления и радиоэлектроники (7I ) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ Al -ФАЗНЫМ

ТИРИСТОРНЫМ ИНВЕРТОРОМ

Изобретение относится к электротехнике, а более конкретно к системам управления многофазными тиристорными инверторами с трансформаторным выходом.

Известно устройство для управления тиристорным инвертором, содержащее цепи подмагS ннчивания силового трансформатора, которое обеспечивает однозначность полярности остаточной индукции s трансформаторе вне зависимости от того, какои тиристор проводил послед1О ним (1). Блок запуска обеспечивает включе.ние каждый раз одного и того же тиристора, поэтому в момент:пуска; исключается насыщение силового трансформатора и обеспечивается надежный запуск инвертора.

Однако это устройство предназначено только для однофазных инверторов, так как цепи лодмагничивания выполняются индивидуально для каждого трансформатора, кроме того, увеличиваются масса и габариты инвертора, так как указанное устройство воздействует на силовые цепи и требует сильноточных и энергетических элементов.

Известно устройство для управления тирисгорным инвертором, которое при включении инвертора обеспечивает частоту выходных импульсов выше, чем в номинальном режиме, и тем самым представляет насыщение выходного трансформатора и обеспечивает надежный запуск инвертора (2).

Однако это устройство предназначено только для однофазных инверторов, кроме того, время выхода инвертора на стационарный режим может быть недопустимо большим.

Наиболее близким по технической сущности к предлагаемому является устройство для управления инвертором, содержащее задающий генератор, кольцевой пересчетный блок и выходные каскады (3). Указанное устройство обеспечивает гальваническую развязку цепей управления от силовых и отличается высокой стабильностью угла сдвига фаз.

Однако это устройство не обеспечивает надежного запуска тиристорного инвертора, так как до включения инвертора полярность остаточной индукции в магнитопроводе силового трансформатора может быть как положитель3 758470 ной, так и отрицательной. В момент пуска первым может включаться тот тиристор, который вызовет дальнейшее увеличение индукции.

А так как длительность управляющих импуль/ сов составляет полпериода выходной частоты, то трансформатор инвертора может насытиться и произойдет срыв коммутации, т.е. инвертор выходит из строя.

Целью изобретения является повышение нацежности инвертора в работе в момент пуска путем уменьшения длительности первого полупериода управляющих импульсов, 5

j !+

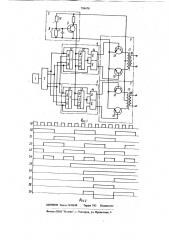

На фиг. 1 представлена схема устройства, на фиг. 2 приведены диаграммы, поясняющие его работу.

Устройство для управления m-фазным тиристорным инвертором содержит задающий ге40 нератор 1, кольцевой пересчетный блок 2, блок запуска 3; логические блоки задержки 4 и 5 и выходные каскады 6, 7. Блок запуска 3 состоит иэ механического выключателя 8, транзистора 9 и делителя на резисторах 10 и 11.

Каждый блок задержки состоит из элемента 2-2И-ИЛИ 12, тактируемого D-триггера 13 и двух двухвходовых блоков совпадения 14.

Выходные каскады 6, 7 представляют собой двухкратные усилителй мощности, каждый из

50 которых собран на транзисторах 15, 16 и трансформаторе 17 с выходной обмоткой 18. Кольцевой пересчетный блок 2 для простоты составлен из двух триггеров (m=2), т.е. изображенное на фиг. 1 устройство предназначено

55 для управления двухфазным инвертором.

Устройство для управления m-фаэным тирис-! торным инвертором работает следующим обра|зом.

Поставленная цель достигается тем, что устройство для управления m-фаэным тиристорным инвертором, содержащее задающий генератор, 15 подключенный ко входу кольцевого пересчетного блока на m триггерах и m выходных каскадов, снабжено блоком запуска и m логическими блоками задержки. каждый из которых .содержит элемент 2-2И-ИЛИ, тактируемый 020 триггер и два двухвходавых блока совпадения, выходы которых подключены соответственно к выходным каскадам, одни иэ входов объединены и соединены с выходом тактируемого

D-триггера, 0- и R-входы которого объединены и подключены к блоку запуска, тактовый вход связан с выходом элемента 2-2И-ИЛИ, одни из входов которого подключены к выходам i-того триггера кольцевого пересчетного блока и к другим входам блоков совпадения, 30 другие входы — к выходаМ j-того триггера кольцевого пересчетного блока, при этом

4.

При подаче напряжения питания на выходе задающего генератора формируются импульсы 19, которые поступают на блок 2. На выходе первого триггера кольцевой пересчетной схемы формируются прямой 20 и инверсный

2I сигналы, на выходе второго триггера— сигналы 22 и 23. Поскольку логические блоки задержки 4 и 5 выполнены по одной и той же схеме, принцип работы их одинаков, то далее останавливаются на работе логического блока зацержки 4. На выходе элемента 2-2И-ИЛИ, 12 формируются сигналы 24, длительность которых равна времени, в течение которого сигналы на выходе триггеров, подключенных к элементу 2-2И-ИЛИ 12, совпадают. В данном случае длительность импульсов 24 равна четверти периода. Эти импульсы поступают на тактовый вход "С" тактируемого 0-триггера !3, но они не могут изменить состояние триггера, так как механический выключатель 8 блока 3 разомкнут, транзистор 9 открыт и с его коллектора на R- и 0-выходы триггера поступает сигнал 25, соответствующий уровню логического

"О", который удерживает триггер в нулевом положении, и на выходе триггера отсутствует разрешающий сигнал 26, Выхоц триггера подключен к одним из входов блока совпадения 14, поэтому выходные сигналы 27, 28 блока совпадения 14 также равны "О", транзисторы 15, 16 выходного каскада 6 закрыты и на обмотке 18 трансформатора 17 нет напряжения. Таким образом, несмотря на то, что задающий генера тор 1 и блок 2 функционируют, устройство в целом находится в режиме ожидания.

При замыкании механического выключателя

8 транзистор 9 закроется и на R- и 0-выходы тактируемого 0-триггера 13 поступит сигнал 25, соответствующий уровню логического "1". Поэтому, как только на входе "С" сигнал 24 изменит свое состояние с "О" на "l", триггер 13 переключится в состояние "1", разрешая тем прохождение единичных сигналов с выхода блока 2 на базы транзисторов 15, 16 выходного каскада 6.. Первоначально на базу транзистора

15 поступит сигнал 27, длительность которого составляет четверть периода выходной частоты.

Затем на базы транзисторов 15, 16 начинают поступать .импульсы 27, 28, длительность которых составляет полпериода выходной частоты, т.е. устройство в целом выходит на стационарный режим. Напряжение на выходной обмотке

18 трансформатора 17, поступающее на управляющие электроды тиристоров, показано на диаграмме 29. Так как включаемый первым тиристор работает всего лишь четверть периода, предотвращается насыщение силового трансфор матора и повышается тем самым надежность инвертора в пусковом режиме.

2. Авторское свидетельство СССР Р 538471 кл. Н 02 P 13/18, 1973.

3. Авторское свидетельство СССР М 481114, кл. Н 02 P 13/18, 1968..

5 75847

При большем числе триггеров в кольцевой пересчетной схеме длительность первого полупериода управляющих импульсов может варьироваться в более широких пределах. Например, в устройстве управления, содержащем кольцевую пересчетную схему иэ шести триггеров, длительность первого полупериода управляющих . импульсов может составлять 90, 60 и 30 эл.градусов. Для этого на другие входы элемента

2-2И-ИЛИ, подключенного одним из входов, например, к выходам первого триггера кольцевой пересчетной схемы, необходимо подавать сигналы соответственно с четвертого, пятого и шестого триггеров кольцевой пересчетной схемы. В общем случае кольцевая пересчетная схема может состоять из m триггеров. 1 огда, для того чтобы получить длительность перво- го полупериода управляющих импульсов меньше или равной четверти периода выходной частоты, другие входы элемента 2-2И-ИЛИ, подключенного одним из входов к входам i-oro триггера кольцевой пересчетной схемы, должны быть подключены к выходам j-ого триггера кольцевой пересчетной схеме, где j A i + — m

Устройство пригодно для управления инвер25 тора любой фазности, в том числе и однофазными. Время выхода инверторами на стационарный режим составляет менее полупериода выходной частоты.

Формула изобретения

36

Устройство для управления m-фазным тиристорным инвертором, содержащее задающий re0 6 нератор, подключенный ко входу кольцевого пересчетного блока íà m триггерах и m выход. ныхкаскадах,отличающееся тем, что, с целью повышения надежности в работе инвертора в момент пуска, оно снабжено блоком запуска и m логическими блоками задерж. ки, каждый из которых содержит элемент

2-2И-ИЛИ, тактируемый О-триггер и два двухвходовых блока совпадения, выходы которых подключены к соответствующему выходному каскаду, одни иэ входов объединены и соединены с выходом тактируемого О-триггера, О- и Я-входы которого объединены и подключены к блоку запуска, тактовый вход связан с выходом элемента 2-2И-ИЛИ, одни иэ входов которого подключены к выходам i-oro триггера кольцевого пересчетного блока и к другим входам блоков совпадения, а другие входы — к выходам J-ого триггера кольцевого пересчетного блока, при этом j h i +—

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 447811, кл. Н 02 P 13/18, 1968.