Частотно-фазовый компаратор

Иллюстрации

Показать всеРеферат

Союз Соеетскик

Социалистических

Республик

О Il И С А Н И Е,„тЬВЛ В

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Пополнительное к авт. свид-ву N 484621 (22} Заявлено 15.05.78 (21) 2616232/18-09 (5 l ) M. Кл. с присоединением заявки №

H 03 О 13/00

Государстееиный камитет (23} П риоритет— па делам изобретений и открытий

Опубликовано 23.08.80. Ь>оллетень № 31

Дата опубликования описания 23.08.80 (53) УД((621 376..55 (088.8) (72) А вторы изобретения

Ю. В, Левочкин и В. И. Левочкина (7l ) Заявитель (54) ЧАСТОТНО-ФАЗОВЪ|Й КОМПАРАТОР

Изобретение относится к радиотехнике и может использоваться в устройствах автоматической подстройки частоты и фазы импульсных сигналов.

По основному авт. св. N 484621 известен частотно-фазовый компаратор, содержащий элементы И-НЕ, фазовый и два блокировочных триггера, причем входы фазового триггера подключены к входам двух элементов И-НЕ, к выходам которых подключены. первые входы блокировочных триггеров, нулевые выходы ко10 торых соединены с их вторыми входами через третий элемент И-Н1 .>а единичные выходы блокировочных триггеров подключены соответственно к первым входам четвертого и пятого

15 элементов И-НЕ, при этом второй вход пятого элемента И-НЕ соединен с выходом четвертого элемента И-НЕ, второй вход которого подключен к нулевому выходу фазового триггера (1).

Однако такой компаратор работает при сравнительно небольшом диапазоне длительностей входных сигналов.

Цель изобретения — расширение диапазона длительностей входных сигналов.

Это достигается тем, что в частотно-фазовом компараторе, содержащем элементы И-НЕ, фазовый и два блокирово >ных триггера, причем входы фазового триггера подключены к входам двух элементов И-НЕ, к вь>ходам которых подключены первые входы блокироно Blbix триггеров, нулевые выходы которых соединены с их вторыми входами через третий элемент

И-НЕ, а единичные выходы блокировочных триггеров подключены соответственно к первым входам четвертого и пятого элементов И-НЕ, при этом второй вход пятого элемента И-НЕ соединен с выходом четвертого элемента И-НЕ, второй вход которого подключен к нулевому выходу фазового триггера, единичный и нулевой выходы фазового триггера подключены соответственно к вторым входам двух элементов

И-НЕ через устройства задержки.

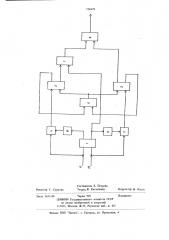

На чертеже приведена структурная электрическая схема предлагаемого компарагора.

Частотно-фазовый компаратор содержит фазовый триггер 1, два блокировочных триггера

2 и 3, элементы И-НЕ 4 — 8 и лва устройства

9 и 10 задержки. На чертеже обозначены так3 7 же входы 11 и 12 компаратора, являющиеся входами фазового триггера 1, Компаратор работает следующим образом.

При превышении частот»1, эталонного сигнала, поступающего на вход 12, над контролируемым сигналом, поступающим на вход 11, обязательно возникает ситуация, при которой в промежутке между двумя соседними импульсами контролируемой частоты на вход 12 компаратора подаются два импульса эталонной частоты.

Первый импульс устанавливает нулевой выход фазового триггера 1 в состояние "1", и одновременно этот импульс проходит на элемент

И-НЕ 5.

Однако совпадения в элементе И-НЕ 5 не происходит, так как включение разрешающего уровня с фазового триггера 1 задерживается в устройстве 9 на величину, равную или более длительности входного сигнала. Таким образом, первый импульс эталонной частоты подготовляет элемент И-НЕ 5 к прохождению второго импульса. Второй импульс с выхода элемента

И-НЕ 5 поступает на первый вход блокировочного триггера 3 и опрокидывает его. При этом единичный, выход блокировочного триггера 3 устанавливается в состояние 0", блокируя работу элемента И-НЕ 8. В результате на выходе компаратора устанавливается состояние "1", что соответствует превышению эталонной частоты над контролируемой. В этом состоянии . омпаратор находится до тех пор, пока в промежутке между поступлениями двух импульсов эталонного сигнала на вход 11 не поступает два импульса контролируемого сигнала.

При этом происходит опрокидывание блокировочного триггера 2 и сигналы с нулевых выходов блокировочных триггеров 2 и 3 через

58478 4 элемент И-HF 6 устанавливают блокировочные триггеры 2 и 3 в исходное состояние, при котором на их единичных выходах появляется уровень "1 . Компаратор переходит от режима сравнения частот к режиму сравнения фаз.

Поскольку при этом на элементы И-HF. 7 и 8 с единичных выходов блокировочных триггеров 2 и 3 подается разрешающий уровень "1", то выход компаратора повторяет состояние

1о нулевого выхода фазового триггера 1, длительность импульса на котором пропорциональна фазовому сдвигу сравниваемых частот.

При превышении в исходном состоянии частоты контролируемого сигнала над эталонным, 15 компаратор работает аналогично, начиная с установки единичного вгяхода фазового триггера 1 в состояние "1".

Предлагаемый компаратор позволяет расширить диапазон длительностей входных сигналов

20 и не требует специальных формирователей входного сигнала.

Формула изобретения

Частотно-фазовый компаратор по авт. св.

N 484621, отличающийся тем, что, с целью расширения диапазона длительностей входных сигналов, единичный и нулевой

30 выходы фазового триггера подключены соответственно к вторым входам двух элементов И.НЕ через устройства задержки.

Источники информации, 35 принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 484621, кл. Н 03 D 13/00, 1974 (прототип).

758478

Составитель Е. Петрова

Техред Ж. Кастелевич

Корректор M. Коста

Редактор С. Суркова

Заказ 5651/48

Подписное

Тираж 995

ПНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4