Стробируемый формирователь с парафазными ттл-выходами

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республнк („)758502

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ Е ТЕ ЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 28.03.78 (21) 2595688/18 — 21 с присоединением заявки— (23) Приоритет—

Опубликовано 23.08в0. Бюллетень №31

Дата опубликования описания 27.08.80 (51) М. Кл. 3

Н 03 К 5/13

Государственный комитет (53) УДК 621.373..52 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. В. Матавкин, А. В. Ниионенко, Т. Н. Кутузова и Г. И. Егоров (71) Заявитель (54) СТРОБИРУЕМЫЙ ФОРМИРОВАТЕЛЬ С ПАРАФАЗНЫМИ

ТТЛ-ВЫХОДАМИ

Изобретение относится к импульсной технике и может использоваться в быстродействующих компараторах напряжений.

Известен стробируемый формирователь с парафазными ТТЛ-выходами, содержащий дифференциальный усилитель на транзисторах с нагрузочными резисторами в коллекторных цепях, ТТЛ-вентили, шины «Строб А . и «Строб Б» (1) .

Целью изобретения является уменьшение потребляемой стробируемым формирователем мощности. 1О

Достигается это тем, что в стробируемый формирователь с парафазными ТТЛ-выходами, содержащий дифференциальный усилитель на транзисторах с нагрузочными резисторами в коллекторных цепях, ТТЛ-вентили, шины «Строб А» и «Строб Б» введены генератор опорных напряжений, первый, второй, третий и четвертый разделительные диоды, первый и второй дополнительные резисторы, первый и второй дополнительные транзисторы, дополнительный диф- о ференциальный каскад на транзисторах и дополнительный источник тока, причем соединенные эмиттеры транзисторов дополнительного дифференциального каскада подключены к дополнительному источнику тока, базы — к соответствующим базам транзисто ров дифференциального усилителя, а коллекторы — к эмиттерам дополнительных транзисторов, к которым также подключены нагрузочные резисторы дифференциального усилителя, к коллекторам транзисторов которого подключены базы инверторов ТТЛвентилей, коллекторы дополнительных транзисторов подключены к шине питания, а базы через первый и второй разделительные диоды — к выходу генератора опорных напряжений и через третий и четвертый разделительные диоды соответственно к шинам

«Строб А» и «Строб Б».

В указанном стробируемом формирователе с парафазными ТТЛ-выходами генератор опорных напряжений выполнен на двухэмиттерном транзисторе, коллектор которого подключен к шине питания, эмиттеры— к коллекторам транзисторов дифференциального усилителя, а база через первый и второй последовательно соединенные диоды смещения подключена к общей шине, и через третий дио* смещения — к выходу генератора опорных напряжений, который через

758502 ограничивактший резистор подключен к шине питания.

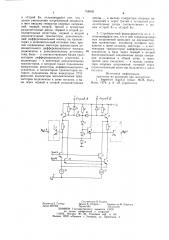

На чертеже приведена принципиальная электрическая схема стробируемого формирователя с парафазными выходами.

Устройство содержит дифференциальный усилитель на транзисторах 1 и 2 с нагрузочными резисторами 3 и 4 в коллекторных цепях, транзисторы 5 и 6 инверторов ТТЛвентилей, шины «Строб А» и «Строб 5» 7 и 8, генератор опорных напряжений, выполненный на двухэмиттерном тра нзисторе 9, ограничивающем резисторе 0 и последовательно включенных прямо смещенных диодах 11, 12 и 13, разделительные диоды 14—

17, дополнительные резисторы 18 и 19, дополнительные транзисторы 20 и 21, допол35 нительныи дифференциальный каскад на транзисторах 22 и 23, генераторы тока 24 и 25.

Формирователь работает следующим образом.

Пусть в исходном состоянии U р — — ЬД хо т. е. выполняется условие баланса тогда, не учитывая напряжение разбаланса (приравняем его к нулю), 1к, =- i — — 1/21гз

Потенциалы без управляемых логическими импульсами транзисторов 20 и 21 с помошью генератора опорных напряжений зафиксированы на уровне 4U@>, т. е. + 2,8В, вследствие чего на эмиттерах транзисторов

20 и 21 устанавливается потенциал U qo, qI ——

= 3U . При условии R > — — R

U, = Ua, = 3Um — ix .К3

Величина R q и ток генератора 24 выбраны такими, чтобы К4 1к = 1„, R j — — 0,7 В. тогда UII, — — U < — — 2Usz = 1,4 В.

Таким образом формируется потенциальный уровень, равный примерно середине помехозашишаюшего корридора ТТЛ, при установлении которого оба инвертора на транзисторах 5 и 6 и остальные элементы ТТЛ вентилей работают в активном режиме, пропуская значительные токи источника питания.

Всякий дифференциальнь;й сигнал (в том числе напряжение смешения), прикладываемый ко входам А и В вызывает изменение коллекторных токов i<, и i„в результате чего коллекторные потенциалы изменяются противофазно, управляя таким образом базовыми токами инверторов на транзисторах

5 и 6. которые в свою очередь управляют ключевыми транзисторами, формирующими логические уровни соответственно нуля и единицы.

Пусть i„, = 1гд., что одновременно означает iq< — — О. Тогда Ug —— - Ug = ЗЬбэ— — и R g, транзистор инвертора отсекается, формируя таким образом на выходе А уровень логической единицы. В то же время при и

i„, = О, 1)„, = 2U<>, причем в базу транзистора 6 инвертора втекает ток 1 = 1/1 (3Uss — 2Ьвэ, = — —, насыщая этот ийУЬЭ вертор, то в свою очередь обеспечивает формирование на выходе В уровня логического нуля. Двухэмиттерный транзистор 9 фи кси рует у ровень Uq< — — U q I,а = 1)вэ, oI раничивая тем самым глубину отсечки транзисторов 5 и 6 и предохраняя транзисторы

1 и 2 от насыщения, что способствует повышению быстродействия.

При подаче на вход «Строб А» низкого логического ТТЛ потенциала U снижается, повторяя этот приложенный уровень.

Пусть Uq = 0,5 — U = 1,2В; Usд =

= 0,5Б, независимо от iq,. Тогда транзистор 5 отсекается, формируя на выходе А логическую единицу. При этом Ug> =

= Бк„) Ъ о, через ризистор 3 протекает ток 1я — — -„ - (Ц,, — U>z ), перезаряжая пауз, разитные емкости эмиттерного узла транзистора 20 прогизоположным по знаку зарядом.

Это приводит к тому, что при снятии низкого логического потенциала с входа

«Строб А» задний фронт стробируюшего импульса па выходе А искажается тем больше, чем оольше Ug, — U,. Как показано выше Ц;,I4A« — 2()вэ, т. е. транзистор 1 отсечен. Для нейтрализации отрицательного вли япия эффекта перезаряда паразитных емкостей управляемых логическими импульсами транзисторов 20 и 21 в рассматриваемое устройство введен управляемый аналоговым сигналом транзисторный дифференциальный токовый каскад, собранный на транзисторах 22 и 23 и генераторе тока 25, причем базы его подключены к базам парафазного транзисторного дифференциального усилителя таким образом, чтобы при 1«, =

=- О - i =- 1г, т. е. противофазно. Тогда открытый транзистор 22 осуществит перехват тока перезаряда паразитных емкостей эмиттерного узла транзистора 20 и поддержит его работу в активном режиме.

При i« — — 1гр ч подаче на вход «Строб А импульса низкого ТТЛ-потенциала транзистор 20 не отсекается, и за счет этого перезаряда его емкостей не происходит.

Положительный эффект использования предлагаемого изобретения заключается в том, что при оптимально выбранном токе генератора 25 суммарный ток, потребляемый стробируемым формирователем с парафазными ТТЛ-выходами составляет примерно половину тока, потребляемого устройством-прототипом при одних и тех же быстродействии и коэффициентах разветвления логических входов и выходов.

Формула изобретения

1. Стробируемый формирователь с парафазными ТТЛ-выходами, содержащий дифференциальный усилитель на транзисторах с нагрузочными резисторами в коллекторных цепях, ТТЛ-вентили, шины «Строб А»

758502 йд Б

Составитель В. Бугров

Редактор Е. Гончар Т хред К. Шчфрич Корректор М. Шароши

Заказ 5697/56 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент» г. Ужгород, ул. Проектная, 4 и «Строб Б», отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены генератор опорных напряжений, первый, второй, третий и четвертый разделительные диоды, первый и второй дополнительные резисторы, первый и второй дополнительные транзисторы, дополнительный дифференциальный каскад на транзисторах и дополнительный источник тока, причем соединенные эмиттеры транзисторов дополнительного дифференциального каскада подключены к дополнительному источнику тока, базы — к соответствующим базам транзисторов дифференциального усилителя, а коллекторы — к эмиттерам дополнительных транзисторов, к которым также подключены нагрузочные резисторы дифференциального усилителя, к коллекторам транзисторов которого подключены базы инверторов ТТЛвентилей, коллекторы дополнительных транзисторов подключены к шине питания, а базы через первый и второй разделительные диоды — к выходу генератора опорных «апряжений и через третий и четзертый разделительные диоды соответственно к шинам «Строб А» и «Строб Б».

2. Стробируемый формирователь по п. 1, отличающийся тем, что в нем генератор опорных напряжений выполнен на двухэмиттерном транзисторе, коллектор которого подключен к шине питания, эмиттеры — к коллекторам транзисторов дифференциального усилителя, а база через первый и второй последовательно соединенные диоды смещения подключена к общей шине, и через третий диод смещения — к выходу генератора опорных напряжений, который через ограничивающий резистор подключен к шине питания.

Источники информации, принятые во внимание при экспертизе

1. Si eties digital linear 31OS Data

Воок, 1974, р. 6 — 23 (прототип).