Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик п>758503 (61) Дополнительное к авт. саид-ву (22) Заявлено 24.04.78 (21) 2607352/18-21 с присоединением заявки Ио (23) Приоритет

Опубликовано 230880.Бюллетень Йо 31

Дата опубликования описания 230880 (Я)М. Нл.з

Н 03 К 5/135

Государственный комитет

СССР по делам изобретений и открытий (53) УДН 624. 142, 66 (088. 8) (72) Авторы изобретения

М,В.Мелень, M.Ã.Ðoìàíþê и Н.И. Бук

Львовский ордена Ленина политехнический институт (73 ) Заявитель (5 4.) УС ТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к вычислительной технике и может быть использовано в преобразователях временного интервала, частоты и фазы в код, ра- 5 ботающих в широком диапазоне частот.

Известны устройства для синхронизации импульсов, используемые в дискретной автоматике и электронной технике, состоящие из двух тактируемых триггеров и одного триггера с установочными входами, одного инвертора и пяти схем совпадения (1) .

Однако в этих устройствах не сохраняется длительность синхронизируемых импульсов. Кроме того, необходимо наличие импульсов вспомогательной тактовой частоты для возвращения схемы в исходное состояние.

Наиболее близким по технической 2О сущности к предлагаемому является устройство, содержащее дифференцирующий блок, дифференцирующие, цепи, триггеры, импульсно-потенциальные схемы совпадения и реверсивный счет- Я5 чик (2} а

Недостатком этого устройства является наличие сбоев синхронизации при совпадении во времени переднега фронта синхронизируемых импульсов импульсами так тов ой частоты, что ограничивает диапазон частот синхронизируемых импульсов .

Цель и з об ре те ни я — расширен ие функциональных возможностей устройства, а именно обеспечения работоспособности устройства при изменении в широких пределах частоты синхронизируемых импульсов.

Поставленная цель достигается тем, что в устройстве для синхронизации импульсов, содержащем дифференцирующий блок, две дифференцирующие цепи, три триггера, два элемента совпадедения и реверсивный счетчик, вычитающий вход которого через первый элемент совпадения соединен с единичным выходом первого триггера, а суммирующий вход через второй элемент совпадения — с единичным выходом второго триггера, а единичные входы триггеров соединены с соответствующими выходами дифференцирующего блока, вход которого соединен с входом синхронизируемых импульсов, причем импульсные входы элементов совпадения соединены между собой, входом импульсов высокостабильной частоты, выход

1зеверсивного счетчика через первую

758503

40

50 дифференцирующую цепь подключен к; нулевым входам первого и третьего триггеров, а единичный вход третьего триггера через вторую дифференцирующую цепь соединен с единичным выходом второго триггера, дополнительно введены два элемента совпадедия, инвертор: триггер, единичный выход которого соединен с первым входом первого дополнительного элемента. совпадения, второй вход которого соединен с входами тактовых импульсов и инвертора, а выход соединен с нулевым входом второго триггера, единичный выход которого соединен с первым входом второго дополнительного элемента совпадения, второй вход которого соединен с выходом инвертора, а выход подключен к единичному входу дополнительного триггера, нулевой. вход которого соединен с нулевым выходом второго триггера.

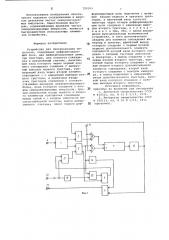

На фиг,1 представлена структуРная схема предлагаемого устройства; на фиг.2 — временные диаграммы, поясняющие его работу.

Устройство для синхронизации импульсов содержит дифференцирующий блок 1 с двумя выходами, основные триггеры 2, 3 4 и дополнительный триггер 5, вход синхронизируемых импульсов 6, Реверсивный счетчик 7, элементы совпадения 8 и 9, вход импульсов высокостабильной частоты 10, дополнительные элементы совпадения

11 и 12 вход тактовых импульсов 13, 3

I дифференцирующие цепи 14 и 15, инвертор 16 и выход устройства 17.

Устройство работает следующим образом.

В исхсдном положении все триггеры устройства находятся в нулевом состоянии. На соответствующих входах элементов совпадения 8, 9, 11 и 12 присутствуют запрещающие сигна-.. лы, поэтому наличие тактовых импуль- . сов на первом входе элемента совпадения 11 и на втором входе элемента совпадения 12 не изменяет состояния ус тройств а.

С приходом первого синхронизируемого импульса (см. фиг.2 а) на вход дифференцирующего блока 1 последний формирует короткие положительные импульсы, соотв етствующие по в ремени переднему (см. фиг.2 в) и заднему (фиг,2 r) фронтам этого импульса.

Импульс (см, фиг.2 в),, поступающий на единичный вход триггера 2, переводит его из нулевого состояния в единичное. С единичного выхода триггера 2 сигнал поступает на вход элемента совпадения 12. При этом последний вырабатывает выходной сигнал (см. фиг ° 2 д) в паузе между тактовыми импульсами (фиг,2 б), так как между входом элемента совпадения 12 и .вхоfO

45 дом тактовых импульсов 13 включен инвертор 16.

Выходной сигнал элемента совпадения 12 переводит триггер 5 из нулевого состояния н единичное (см. фиг.2 е)„ C единичного выхода триггера 5 сигнал поступает на второй вход элемента совпадения 11, который с приходом первого тактового импульса (см, фиг,2 б) на первый его вход вырабатывает выходной импульс (см, фиг.2ж) который поступает на нулевой вход триггера 2, возвращая его нулевое состояние, а положительный импульс с нулевого выхода триггера 2 поступает на нулевой вход триггера

5, возвращая его также в нулевое состояние.

Таким образом, на единичном выходе триггера 2 формируется положительный импульс (см. фиг.2 з) прямоугольной формы, длительности g t<, который разрешает прохождение импульсов высокостабильной частоты (см, фиг. 2 и) через импульсно-потенциальный элемент совпадения 9 на суммирующий вход реверсивного счетчика 7, имеющего в исходном сос тоянии максимальный код (см, фиг. 2 к) И „ 0 кс . За время д t< в реверсивном счетчике 7 запишется код Л о где Т вЂ” период следов ан ия импульсов о высокостабильной частоты.

В момент окончания импульсного сигнала (см. фиг. 2з ) дифференцирующая цепь 14 формирует импульс (см. фиг.2л), устанавливающий триггер 4 в единичное состояние (см, фиг. 2м) .

Импульс (см. фиг. 2г), соответствующий заднему фронту синхронизируемого импульса, переводит триггер 3 в единичное состояние и с его выхода снимается импульс (cM. фиг. 2н ) прямоугольной формы, разрешающий прохождение импульсов высокостабильной частоты через импульсно-потенциальный элемент совпадения 8 на вычитающий вход реверсивного счетчика

7. При эToM импульсы высокocтабильной частоты считывают записанный в счетчик 7 код N Импульсные последовательности на выходе элементов совпадения 9 и 8 представлены на фиг,2о и фиг.2п соответственно. Время, в течение которого в реверсивном счетчике 7 установится исходное значение кода N о „, равно д t . В момент установки максимального кода

Б,„,д дифференцирующая цепь 15 формирует импульс (см. фиг. 2р), устанавливающий триггеры 3 и 4 в нулевое состояние, Схема устройства возвращается в исходное состояние.

Таким образом, синхронизируемый импульс, передний фронт которого совпадает с передним фронтом импульса тактовой частоты, формируется триггером 4„

758503

Использование изобретения обеспечивает надежную синхронизацию в широком диапазоне частот синхронизируемых импульсов. Единственным фактором, ограничивающим диапазон частот синхронизируемых импульсов, является быстродействие используемых элементов устройства, Формула изобретения

Устройство для синхронизации импульсов, содержащее дифференцирующий блок, две дифференцирующие цепи, три триггера, два элемента совпадения и реверсивный счетчик, вычитающий вход которого через первый элемент совпадения соединен с единичным выходом первого триггера, суммирующий вход через второй элемент совпадения — с единичным выходом второго триггера, а единичные входы этих триггеров соединены с соответств ующими выходами дифференцирующего блока, вход которого соединен с входом синхронизируемых импульсов, причем импульсные входы первого и второго элементов совпадения соединены между собой и с входом импульсов высокостабильной частоты, выход реверсивного,счетчика. через первую диф ференцирующую цепь подключен к нулевым входам первого и третьего триггеров, а единичный вход третьего триггера через вторую дифференцирующую цепь соединен с единичным выходом второго триггера, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены два элемента совпадения инвертор и триггер, единичный выход которого соединен с первым входом первого дополнительного элемента совпадения, второй вход которого соединен с входами тактовых импульсов и инвертора, а выход соединен с нулевым входом второго триггера, единичный выход которого соецинен с первым входом второго дополнительного элемента совпадения, второй вход которого соединен с выходом инвертора, а выход подключен к единичному входу дополнительного триггера, нулевой вход которого соединен с нулевым выходом второго триггера, Источники информации, 25 принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Р 424311, кл. Н 03 К 5/13, 1974, 2, Авторское свидетельство СССР

Ф 350151, кл. Н 03 К 5/13. 19/2

30 (прототип).

758503

Миан й1

A(gJ

Составитель В.Муляр

Редактор Т.Иванова Техред Н. Граб

Корректор Н.Григорук

» »»

Филиал ППП Патент, г,ужгород, ул.Проектная, 4

Заказ 5653/50 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5