Устройство синхронизации многоканальных равнодоступных систем связи

Иллюстрации

Показать всеРеферат

Союз Соеетскив

Социалистических

Респубпик

О П И С А Н И Е,758550

ИЗОБРЕТЕН ИЯ

К АВТОИ."КОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. ñâèä-ву

{22) Заявлено 10.05.78 (21) 2612732/18-09 (53 ) M. Кл. с присоединением заявки ¹â€”

H 04 1 7/06

Государственный комитет

{23) Приоритет—

Опубликовано 23.08.80. Бюллетень № 31 но делам изобретений и открытии (53) УДК 621.394.

662(088 8) fl,àòà опубликования описания 23.08.80 (72) Автор изобретения

С. А. Ганкевич (7l) Заявитель

Минский радиотехнический институт (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ МНОГОКАНАЛЬНЫХ

РАВНОДОСТУПНЫХ СИСТЕМ СВЯЗИ

Изобретение относится к радиосвязи и может использоваться в многоканальных децентрализованных синхронно-адресных системах связи с временным делением каналов.

Известно устройство синхронизации много5 канальных равнодоступных систем связи, содержащее последовательно соединенные фильтр, блок фазирования, распределитель, коммутатор, временной дискриминатор и блок тактовой синхронизации, выход которого подключен к второму входу коммутатора, второй выход которого подключен к второму входу блока тактовой синхронизации, при этом вход временного дискриминатора соединен с входом фильтра, второй вход которого объединен с вторым1 входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которого подключен к третьему входу коммутатора (11

Однако такое устройство не обеспечивает достаточно высокой точности синхронизации.

Цель изобретения — повыщение точности синхронизации.

Для этого устройство синхронизации многоканальных равнодоступных систем связи, содержащее последовательно соединенные фильтр, блок фазирования, распределитель, коммутатор, временной дискриминатор и блок тактовой синхронизации, выход которого подключен к второму входу коммутатора, вторсй выход которого подключен к второму входу блока тактовой синхронизации, при этом вход временного дискриминатора соединен с входом фильтра, второй вход которого объединен с вторым входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которого подключен к третьему входу коммутатора, введены блок приема информации и последовательно соединенные блок управления, реверсивный счетчик, блок ключей, сумматор, счетчик и управляющий элемент, выход которого подключен к дополнительному входу распределителя, дополнительный выход которого подключен к блоку управления, другие выходы которого подключены соответственно к вторым входам

758550

10 где ю

N т„ блока ключей.- счетчика и сумматора, второй выход которого подключен к второму входу управляющего элемента, третий вход которого соединен с третьим выходом коммутатора, причем дополнительные выходы блока тактовой синхронизации подключены соответственно к второму входу реверсивного счетчика, и к третьему входу счетчика, а второй вход фильтра через блок приема информации соединен с третьим входом блока ключей.

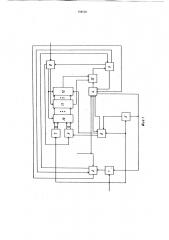

На фиг. 1 дана структурная электрическая схема предложенного устройства; на фиг. 2— схема счетчика.

Устройство содержит фильтр 1, блок 2 фази- JS рования, распределитель 3, коммутатор 4, временной дискриминатор 5, блок 6 тактовой синхронизации, блок 7 приема информации, блок 8 управления, реверсивный счетчик 9, блок 10 ключей, сумматор 11, счетчик 12 и управляющий 20 элемент 13. Счетчик 12 содержит счетчик 14, дешифратор 15, RS-триггер 16, элементы "И/НЕ"

17 — 22.

Устройство работает следующим образом.

Фильтр 1 предназначен для выделения синхро- 25 сигнала, принимаемого в начале каждого занятого временного канала.

С помощью блока 2 фазирования осуществляется поиск временных каналов и начальное фазирование.

Распределитель 3 обеспечивает разметку временных каналов и формирование временных стробов, необходимых для функционирования устройства.

Блок 6 тактовой синхронизации обеспечивает синхронизацию по информационным посылкам с целью их регистрации и синхронизацию распределителя 3.

Коммутатор 4 обеспечивает компенсацию фазовых сдвигов, возникающих вследствие раэлич- 40 ных времен задержки канальных сигналов, и формирование импульсов канальной частоты для определения начала временных каналов через цикл.

Временной дискриминатор 5 обеспечивает 4S формирование дискриминационной характеристики при приеме синхросигнала.

Управляющий элемент 13 обеспечивает коррекцию фазы распределителя 3 при изменении расстояния между станциями. S0

Блок 7 предназначен для выделения из принятых канальных сигналов от других станций информации о состоянии реверсивных счетчиков 9.

Блок 10 обеспечивает запись в сумматор 11 кода реверсивного счетчика 9 и информации о состояниях реверсивных счетчиков 9 других станций. С помощью сумматора 11 осуществляется операция суммирования фазового рас4 согласования всех станций, работающих в сети, накопленного в течение цикла.

Счетчик 12 обеспечивает подачу на вход управляющего элемента 13 импульсов в соответствии с кодом сумматора 11.

Реверсивный счетчик 9 предназначен для усреднения и накопления информации о разности фаз между принимаемыми канальными сигналами и опорным сигналом в течение длительности цикла.

Влияние задержки на частоту следовашщ временных каналЬв приводит к погрешности в восстановлении начала временных каналов через цикл, определяемой величиной приращения задержки, и срыву синхронизма при превышении величины "ь„(2, где т, — длительность элементарной посылки. Каждая из станции сети использует информацию о разности фаз между .опорным и канальным сигналами за время цикла на всех станциях, работающих в сети.

Информацией о величине приращения задержки в сети является

К М

Еhhq" Е (И„-- )тц, 4=1 л=1 свободная частота, i — станции; число станций в сети; длительность цикла.

При нулевой либо скомпенсированной задержке

И, . ьср„=О.

1=1

При наличии приращения задержки эта величина определяется выражением и К Н й, .2 аСР„.=Т Са — K Х ;

Ц-1 „1 где

М

Х 6,7;

1,1+ - " л

1--1 g-1 где К вЂ” коэффициент усиления; т" — величина задержки радиосигнала

Jt между i u j станциями.

Последнее выражение и позволяет составить алгоритм двухсторонней синхронизации.

Каждая из станций сети в занятом временном канале передает информацию о величине

ЬР; = (и i — м)Тц, накопленной в течение предыдущего цикла. Принятая от всех станций информация суммируется на каждой из станций о собственном значении величины р., наI копленным за цикл, и фаза распределителя временных каналов, а следовательно, и канального сигнала при передаче сдвигается в сооти по окончании счетного импульса на входе триггер 16 опрокидывается, закрывая посредством подачи на элемент И" 17 нулевого сигнала на вход счетчика 14, который открывается вновь только по приходу сигнала начальной установки.

Предложенное устройство позволяет за счет устранения влияния задержки на среднюю частоту в сети обеспечить более высокую точность синхронизации по временным каналам.

Устройство синхронизашги многоканальных равнодоступных систем связи, содержащее последовательно соединенные фильтр. блок фазирования, распределитель, коммутатор, временной дискриминатор и блок тактовой синхронизации, выход которого подключен к второму входу коммутатора, второй выход которого подключен к второму входу блока тактовой синхронизации, при этом вход временного дискриминатора соединен с входом фильтра, второй вход которого объединен с вторым входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которого подключен к третьему входу коммутатора, о т л ич а ю щ е е с я тем, что, с целью повышения точности синхронизации, введены блок приема информации и последовательно соединенные блок управления, реверсивный счетчик, блок ключей, сумматор, счетчик и управляющий элемент, выход которого подключен к дополнительному входу распределителя, дополнительный выход которого подключен к блоку управления, другие выхОды которого подключены соответственно к вторым входам блока ключей, счетчика и сумматора второй выход которого

I подключен к второму входу управляющего элемента, третий вход которого соединен с третьим выходом коммутатора, причем дополнительные выходы блока тактовой синхронизации подключены соответственно к второму входу реверсивного счетчика и третьему входу счетчика, а второй вход фильтра через блок приема информации соединен с третьим входом блока ключей.

Источники информации, принятые во внимание при экспертизе

1. Заявка Р 2372221/18-09, кл. П 04 L 7/02, 1976 (прототип).

5 758550 ветствии с величиной 2 Ар в противопоte f ложную по знаку сторону, что позволяет компенсировать влияние задержки на частоту.

На этапе вхождения в связь с помощью блока 2 фазирования производится фазирование распределителя 3 по синхросигналу, принимаемому с минимальной задержкой относительно тактовых точек временных каналов и фазирование делителей по синхросигналам, принимаемым в соответствующих временных каналах. 10

По отклику фильтра 1 делитель тактовой частоты коммутатора 4 устанавливается в нулевое состояние, а делитель каналъной частоты комму. татора 4 — в код, соответствующий базе синхросигнала. Одновременно производится коррек- 1э ция фазы опорного сигнала тактовой частоты.

Для этого в начале временного канала вход делителя коммутатора подключается к управляющему элементу блока 6, а выход — к временному дискриминатору 5. 20

В MoMGHT фазирования распределитель 3 не подстраивается, а по окончании процесса фазирования подключ,1ется к выходу управляющего элемента блока 6 через коммутатор 4 и управляющий элемент 13. 25

Коммутация делителей осуществляется сигналами с блока 8.

С помощью реверсивного счетчика 9 измеряется фазовое рассогласование между опорны,.ми и канальными сигналами за время цикла. ЭО, В занятом для передачи временном канале каждая из станций информирует другие станции о состоянии реверсивного счетчика 9. В результате суммирования значений кода, полученных от всех других станций, и кода собственного реверсивного счетчика 9 на выходе сумматора

11 формируется код, пропорциональный величине прира.цения задержки радиосигнала. В соответствии со значением кода с помощью счетчика 12 и управляющего элемента 13 произво- 40 дится сдвиг фазы распределителя 3, компенсирующий приращение задержки.

Установка счетчика 12 в нулевое состояние производится сигналом с блока 8 управления.

Единишьтм сигналом с дешифратора 15 откры- 45 вается элемент "И" 19, и вне зависимости от предыдущего состояния RS-триггера 16 последний переходит в единичное состояние. При этом на элемент "И" 17 подается разрешение, а вход элемента "И" 18 закрывается нулевым сигна- чО лом с противоположного плеча RS-триггера 16.

При записи в счетчик 14 числа импульсов, соответствующего коду сумматора 11, на элемент

"И" 20 подается разрешение с дешифратора 15, Формула изобретения