Устройство выделения рекурентного сигнала с обнаружением ошибок

Иллюстрации

Показать всеРеферат

Союз Советсннх

Ссщнаюктнчесник

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{n)758552 (61) Дополнительное к авт. сеид-ву (22) Заявлено 030878 (21) 2667804/18-09 (51) М. Кл з с присоединением заявки ¹ (23) Приоритет

Н 04 L 7/10

1 осударствениый комитет

СССР но делам изобретений и открытий

Опубликовано 23.0880. Бюллетень ¹ 31

Дата опубликования описания 23.08.80 (53) УДК 621. 394. .662.2(088.8) (72) Авторы изобретения

В. Е. Петухов, A. К. Грешневиков, В. И. Ключко, С. П. Попов и Н.Н. Сахарова (71) Заявитель

{54) УСТРОЙСТВО ВЫДЕЛЕНИЯ РЕКУРРЕНТНОГО

СИГНАЛА С ОБНАРУЖЕНИЕМ ОШИБОК

Изобретение относится к электросвязи и может использоваться в системах передачи двоичной информации.

Известно устройство выделения рекурентного сигнала с обнару>кением ошибок, содержащее последовательно соединенные переключатель режимов работы, блок проверки на рекуррентность, селектор и элемент И, выход которого подключен к одному иэ входов переключателя ре>киМов работы, управляющий вход которого соединен с выходом реверсивного счетчика и другим входом элемента И, причем другой выход блока проверки на ре- 15 куррентность подключен к другому входу переключателя режимов работы и первому входу блока сравнения, к второму входу которого подключен другой выход переключателя режимов 20 работы (1) .

Однако, известное устройство име-. ет невысокую точность выделения рекуррентного синхросигнала.

Цель изобретения - повышение точ- 25 ности выделения рекуррентного синхросигнала. ,Цля этого в устройство выделения рекуррентного сигнала с обнаружением .ошибок, содержащее последовательно соединенные переключатель режимов работы, блок проверки и рекуррентность, селектор и элемент И, выход которого подключен к одному из входов переключателя режимов работы, управляющий вход которого соединен с выходом реверсивного счетчика и другим входом элемента И, причем выход блока проверки на рекуррентность подключен к другому входу переключателя режимов работы и первому входу блока сравнения, к второму входу которого подключен другой выход переключателя режимов работы, введены последовательно соединенные дополнительный переключатель, анализатор ошибок, счетчик и выходной формирователь, при этом к двум другим входам выходного формирователя подключены соответственно выход дополнительного переключателя и выход элемента И, который соединен с другим входом счетчика и с одним из входов дополнительного переключателя, к другим входам . которого подключены соответственно выход счетчика, выход блока сравнения и один из выходов анализатора ошибок, другой выход которого подключен к соответствующему входу реверсивного счетчика.

758552

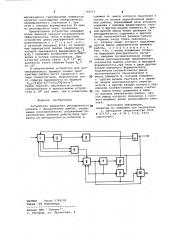

На чертеже представлена структур ная электрическая схема предлагаемого устройства.

Устройство содержит переключатель

1 режимов работы, блок 2 проверки на рекуррентность, селектор 3, элемент И

4, блок 5 сравнения, дополнительный переключатель 6, анализатор 7 ошибок, реверсивный счетчик 8, счетчик 9 и выходной формирователь 10.

Устройство работает следующим образом.

Принимаемая последовательность двоичных символов через переключатель

1 поступает в блок 2 проверки на рекуррентность. В этом блоке, содержащем регистр сдвига на к-разрядов с точ- 15 лами съема на сумматоры по модулю два (в соответствии с многочленом P(x) ), принимаемые символы проверяются на соответствие закону рекуррентного кода. Так, например, для 20

P(x) = x + x+ уравнение проверки имеет вид х; х ® x, - 6, где x,. — принимаемые из канала связи элементы последовательности; Q+ — сложение по модулю два.

Результаты проверки формируются в блоке 5 сравнения и подсчи- 30 тываются реверсивным счетчиком

8. Поскольку одиночный ошибочный элемент, проходя по к-значному регистру сдвига блока 2, образует на выходе блока 5 сравнения к-раз- 35 рядную последовательность из единиц и нулей (причем вес этой последовательности е )r 3), то нецелесообразно, чтобы каждая единица сбрасывала счетчик 8 на к-тактов. Поэтому реверсивный счетчик 8 сбрасывается только первой единицей, появившейся на выходе блока 5. А с помощью анализатора 7 продолжается дальнейший анализ к-разрядного интервала рекуррентной последовательнос- 4э ти. Если анализатор 7 определит, что последовательность, образованная на выходе блока 5, по своей конфигурации соответствует одиночной ошибке, то реверса счетчика 8 боль- 5Q ше не происходит. Это обуславливается отсутствием необходимости исключать из анализа рекуррентной последовательности интервал, превышающий к-разрядов, поскольку ошибочный элемент, обеспечивший реверс счетчика на к-тактов, успеет выйти из регистра блока 2 до того, как счетчик 8 отсчитает сброшенные к-разрядов.

Если анализатор 7 определит наличие пакета ошибки на интервале к-разрядов, то на своем втором выходе выдает сигнал, который одновременно закроет переключатель б, включит в работу счетчик 9 и обеспечит реверс счетчика 8 еще на ) тактов (где Ч =0,1,2,...).

Величина Ч выбирается из условий обеспечения требуемой достоверности выделения синхросигнала. Дополнительный реверс счетчика 8 обусловлен тем, что последний искаженный элемент пакета ошибки не успеет выйти из регистра блока 2 проверки на рекурректность до того, как счетчик отсчитает k тактов, прибавленные ранее. Блокировка выхода блока 5 необходима для исключения нежелательного воздействия последнего искаженного разряда пакета на анализатор 7, поскольку каждый о.:ибочный элемент последовательности влечет размножение ошибок на выходе блока

5. Дальнейший анализ продолжается по сигналу переполнения счетчика 9 (емкость счетчика равна К), который подключает выход блока 5 ко входу анализатора 7 ошибок. Таким образом, анализатор 7 продолжит анализ рекуррентной последовательности после того, как последний искаженный знак пакета ошибки выйдет из регистра блока 2 проверки на рекуррентность.

По окончании зачетного участка рекуррентной последовательности происходит срабатывание счетчика 9.

В этом случае импульс переполнения счетчика 9, воздействуя на переключатель 1, отключает поступление элементов синхросигнала из канала связи и переводит регистр сдвига блока 2 в автономное генерирование рекуррентной последовательности. Селектор 3, подключенный к блоку 2 проверки на рекуррентность, при достижении селектируемой k-значной комбинации, через элемент И 4 выдает фазирующий сигнал. Этот сигнал возвращает устройство в исходное состояние, размыкая цепь обратной связи блока 2 через переключатель 1 режимов работы и сбрасывая счетчик

8 до нуля.

Для уменьшения ложной синхронизации в устройстве производится дополнительная проверка на точность выделения синхросигнала. Это осуществляется путем поэлементного сравнения на блоке 5 генерируемых блоком 2 двоичных знаков с последними k-разрядами рекуррентной последовательности, поступающей из канала связи. Поэтому для определения начала сравнения селектор 3 настраивается не на последнюю k-значную комбинацию рекуррентной последовательности, а на комбинацию, следуемую на k-разрядов раньше (предыдущую). Сигнал с селектора 3 через элемент И включает счетчик 9 (в данном случае он определяет конец выделения синхросигнала), а блок 5 сравнения соединяет со входом устройства. Результат сравнения поступает на вход выходного формирователя 10, который в случае

758552 несовпадения сравниваемых элементов запретит прохождение синхросигнала, сформированного счетчиком 9. При этом с помощью формирователя 10 можно регулировать порог сравнения.

Предлагаемое устройство обладает более высокой технико-экономической эффективностью. Если в известном устройстве длина рекуррентной последовательности и = 2" -1 и k=S, n=31, а зачетный интервал (=10, то появление однократной ошибки (вероятность которой оценивается выражением Р„

ХпРО ) приведен вследствие ее размножения к потере синхросигнала. При качестве канала связи P = 10 вероятность этого события будет Р„,= 15

3 10

В предлагаемом устройстве для рассматриваемого примера только трехкратные ошибки могут привести к потере синхросигнала. Вероятность это- 20 го события оценивается по формуле

Рп„ С„ Ðî(1 7о) -0 > 9О =5 Ю

Таким образом, вероятность потери синхросигнала в предлагаемом устройстве в 10 раз ниже, чем в известном. 25

Формула изобретения

Устройство выделения рекуррентного З » сигнала с обнаружением ошибок, содержащее последовательно соединенные переключатель режимов работы, блок проверкй на рекуррентность,селектор и

ЦНИИПИ Заказ 57á8/20

Тираж 729 Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 элемент И, выход которого подключен к одному из входов переключателя режимов работы, управляющий вход которого соединен с выходом реверсивного счетчика и другим входом элемента И, причем другой выход блока проверки на рекуррентность подключен к другому входу переключателя режимов работы и первому входу блока сравнения, ко второму входу которого подключен другой выход переключателя режимов работы, о т л и ч а ю щ е е с я гем, что, с целью повышения точности выделения рекуррентного сигнала, введены последовательно соединенные дополнительный переключатель, анализатор ошибок, счетчик и выходной формирователь,при этом к двум другим входам выходного формирователя подключены соответственно выход дополнительного переключателя и выход элемента И, который соединен с другим входом счетчика и с одним из входов дополнительного переключателя, к другим входам которого подключены соответственно выход счетчика, выход блока сравнения и один из выходов анализатора ошибок, другой выход которого подключен к соответствующему входу реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 475744, кл. Н 04 L 7/10, 1973 (прототип).