Устройство для контроля исправности кодера-декодера циклического кода

Иллюстрации

Показать всеРеферат

(1и 758553

Союз Советск к к

Социалнстнческмк

Республнк (61) Дополнительное к авт. свил-ву (22) Заявлено 07.07.76 (21) 2382592/18-09 с присоединением заявки J% (23) Приоритет (51}M. Кл .

Н 04 L 11/08

Н 03 G 13/34

Пиударстееииый комитет

CCCP

Ао делам изооретеиий н открытий (53) УДК 621.326..7 (088.8) Опубликовано 23.08.80. Бюллетень ¹ 31

Дата опубликования описания 23.08.80 (72) Авторы изобретения

Б. П. Куприенко, И. 10. Максимов и Д. И. Ройзенвасер (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВНОСТИ

КОДЕРА — ДЕКОДЕРА ЦИКЛИЧЕСКОГО

КОДА

Изобретение относится к технике связи и может использоваться в системах передачи информации, телеметрических системах, автоматических системах управления и др.

Известно устройство для контроля исправS ности кодера — декодера циклического кода, содержащее блок управления, первый и второй выходы которого подключены соответственно к первому и второму входам триггера, первый и второй выходы которого подключены соот.

10 ветственно к первому входу первого элемента

И и первому входу второго элемента И, второй вход которого соединен с выходом источника информационных кодов, а выход второго элемента И через элемент ИЛИ, второй вход

15 которого соединен с выходом первого элемента И, подключен к информационному входу преобразователя циклического кода (1).

Однако точность контроля такого устройства невысока.

Цель изобретения — повышение точности контроля.

Это достигается тем, что в устройство для контроля исправности кодера — декодера цикличестного кода, содержащее блок управления, первый и второй выходы которого подключены соответственно к псрвому и второму входам триггера, первый и второй выходы которого подключены соответственно к первому входу первого элемента И и первому входу второго элемента И, второй вход которого соединен с выходом источника информационных кодов, а выход второго элемента И через элемент ИЛИ, второй вход которого соединен с выходом первого элемента И, подключен к информационному входу преобразователя циклического кода, введены источник контрольных кодов, блок искажения кодов и компаратор, при этом первый выход триггера подключен ко второму входу первого элемента И и входу источника контрольных кодов, выход которого подключен к первому входу первого элемента И и к первому входу блока искажения кодов, выход и второй вход которого соединены соответственно с первым входом компаратора и третьим выходом блока управления, четвералый и пятый выходы которого подключены соответственно к первому и второму управля758553

3 ющим входам преобразователя циклического кода, выход которого подключен ко второму входу компаратора.

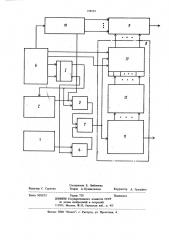

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство для контроля исправности кодера — декодера циклического кода содержит источник 1 информационных кодов, источник 2 контрольных кодов, первый и второй элементы И 3 и 4, триггер 5, блок 6 управления, 10 элемент ИЛИ 7, преобразователь 8 циклического кода, компаратор 9 и блок 10 искажения кодов, при этом преобразователь 8 циклического кода состоит из регистра 11 сдвига с обратными связями, дешифратора 12 кодов оШибок и ре- 15 гистра 13 коррекции кодов, Устройство работает следующим образом, Сигналом из блока 6 триггер 5 устанавливается в единичное состояние, разрешающий сигнал с единичного выхода триггера.5 подается па входы источника 2 и первый элемент И 3, и из источника 2 на вход регистра 11 подается сначала такой к-разрядный контрольньш код, и — kизбыточные разряды которого,,формируемые в регистре 11, должны соответствовать адному из кодов настройки дешифратора 12.

Этот же k-разрядный код сигналом разрешения записи, поступающим из блока 6, записывается в регистр 13. После поступления на вход регистра 13, когда в регистре 11 сформируется код остатка, на управляющий вход разрешения коррекции регистра 13 поступает сигнал из блока 6, открывающий входы коррекщ и всех разрядов регистра 13. В случае исправной работы устройства сигнал с дешифратора 12 35 поступит на вход коррекции одного или нескольких (в зависимости от кратности ошибок) разрядов регистра 13 и изменит символы, записанные в них, на противоположные, т.е. в зти разряды исходного контрольного кода будут вне- 4g сены ошибки.

Контрольный код из источника 2 поступает также в блок 10. По сигналу, поступающему из блока 6 осуществляется искажение исходного контрольного кода, соответствующее искажению контрольного кода в регистре 13 при . исправной работе кодера †декоде, так как при неисправности кодера †декоде в регистре 13 будет другой код, который и позволяет обнарухсить эту неисправность.

Искаженные контрольные к ды с выходов блока 10 и регистра 13 поступают на входы компаратора 9 и сравниваются. На выходе компаратора 9 при равенстве кодов формируется сигнал исправности кодера — декодера.

В случае исправной работы устройства произойдет совпадение всех сравниваемых кодов, в случае возникновения отказа в регистре 11, в дешифраторах 12 или в регистре 13 произойдет несовпадение хотя бы одного из cpasниваемых кодов.

Предлагаемое устройство для контроля кодеров — декодеров циклических кодов с коррек. цией ошибок позволяет значительно повысить точность контроля.

Формула изобретения .Устройство для контроля исправности кодерадекодера циклического кода, содержащее блок управления, первый и второй выходы которого подключены соответственно к первому и второму входам триггера, первый и второй выходы которого подключены соответственно к первому входу первого элемента И и первому входу второго элемента И, второй вход которого соединен с выходом источника информационных кодов, а выход второго элемента И через элемент ИЛИ, второй вход которого соединен с выходом первого элемента И, подключен к информационному входу преобразователя циклического кода, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, введены источник контрольных кодов, блок искажения кодов и компаратор, при этом первый выход триггера подключен ко второму входу первого элемента И и входу источника контрольных кодов, выход которого подключен к первому входу первого элемента И и к первому входу блока искажения кодов, выход и второй вход которого соединены соответственно с первым входом компаратора и третьим выходом блока управления, четвертый и пятый выходы которого подключены соответственно к первому и второму управляющим входам преобразователя циклического кода, выход которого подключен ко второму входу компаратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 534877, кл. H 04 1 3/02, 1974 (прототип).

758553

Составитель Е. Любимова

Техред А. Куликовская

Корректор А. Гриценко

Редактор С. Суркова

Тираж 729

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

1I3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5656/52

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4