Частотно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВТИЗЬСТВУ

Союз Советскмх

Социалыстическнх

Республик

<, 1758559 (61) Дополнительное к авт. свид-ву (22) Заявлено 24,0778 (21) 2б 49049/18-09 с присоединением заявки М (51) и KA 3

Н 04 L 27/22

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 230880. Бюллетень М231

Дата опубликования описания 2 30880 (53) УДК 621.391. .27(088.8) (72) Авторы изобретения

А. А. Гришуков, И. Б. Петяшин, В. В. Гинзбург и Л. М. Рахович (71) Заявитель (54)ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к связи и может использоваться в приемниках многоканальных модемов с ортогональными канальными сигналами и двукратной фазоразностной модуляцией.

Известен частотно-фазовый дискриминатор, содержащий два перемножителя, первые входы которых объединены, а выходы — подключены к входам соответствующих интеграторов, первый блок-определения знаka, вход которого соединен с вхо-. дом первого инвертора, выход ко-. торого подключен к первому входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого подключен первый вход четвертого перемножителя, второй вход которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и второго перемножителей поданы соответствующие опорные сигна313.

Однако известный дискриминатор не обеспечивает высокую точность сравнения частот.

Целью изобретения является повышение точности сравнения частот.

Для этого в частотно-фазовый дискриминатор, содержащий два перемножителя, первые входы которых объединены, а выходы подключены к входам соответствующих интеграторов, первый блок определения знака, вход которого соединен с входом первого инвертора, выход которого подключен к первому входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого подклю15 чен первый вход четвертого перемножителя, второй вход. которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и вто20 рого перемножителей поданы соответствующие опорные сигналы, введены четыре дополнительных перемножителя, второй инвертар, второй и третий ,сумматоры, два блока вычисления модуля, блок сравнения, два ключа и два элемента задержки, входы которых .соединены с выходами соответствующих интеграторов и первыми входами соответствующих дополнительных

30 перемножителей, к вторым входам кото 8559 рых подключены выходы элементов задержки, а выходы соответствующих дополнительных перемножителей соединены с входами второго и третьего сумматоров, выходы которых подключены к входам блоков определения знака и блоков вычисления модуля, выходы которых соединены с входами блока сравнения, выходы которого подключены к первым входам ключей, вторые входы которых соединены соответственно с выходами третьего и четвертого пе- 10 ремножителей, причем выходы ключей соединены с входами первого сумматора, а выход соответствующего допол.нительного перемножителя подключен к входу второго инвертора, выход ко- 15 торого соединен с соответствующим входом третьего сумматора.

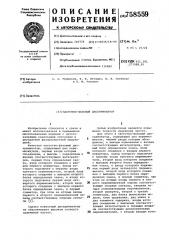

На чертеже приведена структурная электрическая схема предложенного дискриминатора.. 20

Частотно-фазовый дискриминатор содержит четыре перемножителя 1,2,3,4, интеграторы 5,6, первый и второй блоки 7, 8 определения знака, первый и второй инверторы 9, 10, первый, 25 второй и третий сумматоры 11, 12, 13, четыре дополнительных перемножителя

14, 15, 16, 17, два. блока 18, 19 вычисления модуля, два ключа 20, 21, два элемента 22, 23 задержки и блок

24 сравнения.

Дискриминатор работает следующим образом.

Входной сигнал имеет смещение частоты и записывается в виде „®=0 sin((и +аи)) +1+ ч ), где м — номинальная частота сигнаа ла;

6и — смещение частоты сигнала, Ч> — информационная фаза сиг- 40 нала;

Ч вЂ” начальная фаза сигнала, U — амплитуда сигнала. о

Входной сигнал поступает на первый и. второй перемножители 1,, соединенные с соответствующими интеграторами 5, 6. На вторые входы первбго и второго перемножителей 1, 2 подаются соответственно опорные сигналы

U S1ïозс и U Соя щ с . Полученные

0 о о о игнана выходе интеграторов 5, 6 сиг лы являются проекциями входного сигнала и определяются следующим образом: !

55

ФОРмУла изобретения

Частотно-фазовый дискриминатор, содержащий два перемножителя, первые входы которых объединены, а выходы подключены к входам соответст.вующих интеграторов, первый блок определения знака, вход которого соединен с входом первого инвер60

t+T =-(u М. tat

2 7 ВХ о

t Т = — ц фсО&ю1Ж, t е Т вЂ” интервал обработки сигнала. где

Проекции сигнала непоср д и чер рез элементы 22, 23 задержки поси 14-17, вытупают на перемножители числяющие произведени яХХ,УУ, у у,, Х У„, Х, и У представляют собой проекций сигнала на данной посылке, а Х и У вЂ” проекции сигнала на предыдущей посылке. Напряжения с выходов перемножителей 14, 16, соответствующие произведениям Х Х и

У У, непосредственно суммируются на сумматоре 12, а напряжение, соответствующее произведению У„ Х через инвертор 10 суммируется с напряжением, соответствующим произведению Х<У< на сумматоре 13.

Напряжения на выходах сумматоров

12, 13 пропорциональны величинам ди Т ь

g LUX

iin — 11 in(a иэ )

Е2. 4 2 1Я О д > т )

2 где — информационная разность фаз, которая при двукратной фазоразностной зс модуляции принимает значения О, вЂ,Л. и . Напряжение U поступает .на бло

18, через первый ийвертор 9- на пер2 вый вход третьего перемножителя 3 и через первый блок 7 — на первый вход четвертого перемножителя 4. Напряжение Uzg поступает на блок 19, на второй вход четвертого перемножителя 4 и через второй блок 8 на второй вход третьего перемножителя 3. Напряжение 10 1и )И Iс выходов блоков 18, 19 поступают на блок 24, выходными сигналами которого управляются ключи 20 и 21 °

Результаты перемножений через ключи 20 и 21 поступают на первый сумматор 11, выходное напряжение которого зависит только от смещения частоты и равно (3 2 " л)з дп К +У„У ) ес.""(g2 . 4 2)ъ р -(5<+1>>)49>(kp-X V„ I,å и!жк ° з v (c

,„Ó->

Предлагаемый частотно-фазовый дискриминатор позволяет существенно повысить точность сравнения частот за счет суммирования сигналов рассогласования, полученных в отдельных каналах.

758559

Составитель Е. Петрова

Редактор М. Ликович Техред A. Щепанская

КорректорВ. Бутяга

Эаказ 5768/20 Тираж 729

ЦНИИПИ Государственного комитета СССР п делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 тора, выход которого подключен к первому входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого подключен первый вход четвертого перемножителя, второй вход которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и второго перемножителей поданы соответствующие опорные сигналы, о т л и ч а юшийся тем, что, с целью повышения точности сравнения частот, введены четыре дополнительных перемножителя, второй инвертор, второй и третий сумматоры, два блока вычисления модуля, блок сравнения, два ключа и два элемента задержки, входы которых соединены с выходами соответствующих интеграторов и первыми входами соответствующих дополнительных перемножителей, к вторым входам которых подключены выходы элементов задержки, а выходы соответствующих дополнительных перемножителей соединены с входами второго и третьего сумматоров, выходы которых подключены к входам блоков определения знака и блоков вычисления модуля, выходы которых соединены с входами блока сравнения, выходы которого подключены к первым входам ключей, вторые входы которых соединены соответственно с выходами третьего и четвертого перемножителей, причем выходы ключей соединены с входами первого сумматора, а выход соответствующего дополнительного перемножителя подключен к входу второго инвертора, выход которого соединен с соответствующим входом третьего сумматора.

Источники инФормации, принятые во внимание при экспертизе

20 1. Патент ФРГ Р 1512561, кл. Н 04 L 27/22, опублик. 1975 (прототип).