Устройство кадровой синхронизации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >758564 (61) Дополнительное к авт. свид-ву (22) Заявлено 09,02.78 (21) 2576700/18-09 с присоединением заявки №вЂ” (28) П риоритет Э (51 ) М. Кл.

Н 04 и 5/04

Гооударстееиный комитет

СССР

Опубликовано 23.08.80. Бюллетень № 31 по девам изобретений и открытий (53) УДК 621.397. .335.1 (088.8) Дата опубликования описания 23.08.80 (72) Авторы изобретения

Я. Д. Хацкелевич, Т. Ф. Дубова и А. А. Егоров (7!) Заявитель (54) УСТРОЙСТВО КАДРОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике и может быть использовано в системах связи.

Известно устройство кадровой синхронизации, содержащее регистр сдвига, выходы которого соединены с соответствующей первой группой

5 входов коррелятора прямого кода и коррелятора обратного кода, вторые группы входов которых соединены соответственно с выходами блока памяти кода маркера, при этом выход коррелятора прямого кода соединен с первым входом первого элемента ИЛИ, второй вход icoторого соединен с выходом коррелятора обратного кода, а выход первого элемента ИЛИ соединен с первыми входами блока подтверждения маркера и блока обнаружения ложного мар. кера, причем ко второму: входу блока обнаружения ложного маркера подключен выход первого элемента НЕ, вход которого соединен с выходом формирователя кадрового интервала и со вторым входом блока подтверждения маркера 111.

Однако в таком устройстве особенно при низких отношениях сигнал/шум на бит переда2 ваемой информации из-за сбоев происходит потеря информации. К сбоям приводит пропуск маркера или ложное его определение на этапе вхождения в синхронизм, переход в ложное состояние синхронизации на этапе текущего приема информации.

Цель изобретения — повышение помехоустойчивости выделения синхронизирующего маркера, Это достигается тем, что в устройство кадровой синхронизации, содержащее регистр сдвига, выходы которого соединены с соответствующей первой группой входов коррелятора прямого кода и коррелятора обратного кода, вторые группы входов которых соединены соответственно с выходами блока памяти кода маркера, при этом выход коррелятора прямого кода соединен с первым входом первого элемента

ИЛИ, второй вход которого соединен с выходом коррелятора обратного кода, а выход первого элемента ИЛИ соединен с первыми входами блока подтверждения маркера и блока обнаружения ложного маркера, причем ко второму входу блока обнаружения ложного маркера подключен выход первого элемента НЕ, 3 75856 вход которого соединен с выходом формирователя кадрового интервала и со вторым входом блока подтверждения маркера, введены блок обнаружения пропуска маркера, первый, второй и третий блоки формирования весовых коэффициентов, второй, третий и четвертый элемент

НЕ, первый, второй, третий и четвертый элемент И, второй и третий элементы ИЛИ, а также блок принятия решений и сумматор-накопитель, при этом выход первого элемента ИЛИ 10 соединен с первым входом блока обнаружения пропуска маркера через второй элемент НЕ, а второй вход блока обнаружения пропуска маркера соединен со входом первого элемента НЕ, со вторым входом блока подтверждения марке- 15 ра и с входом формирователя кадрового интервала, при этом выход блока обнаружения пропуска маркера соединен с первым входом первого элемента И, ко второму входу которого подключен выход первого блока формиро- >0 вания весового коэффициента, выход блока обнаружения ложного маркера соединен с первым входом второго элемента ИЛИ и первым входом второго элемента И, второй вход которого соединен с выходом второго блока формирова- 25 ния весового коэффициента, а выход блока подтверждения маркера соединен со вторым входом второго элемента ИЛИ и с первым входом третьего элемента И, второй вход которого соединен с выходом третьего блока формирования весового коэффициента, причем выходы первого, второго и третьего элементов И соединены соответственно с первым, вторым и третьим входами третьего элемента ИЛИ, выход которого соединен со входом блока принятия решений через сумматор-накопитель, при этом первый выход блока принятия решений соединен с третьим входом первого элемента И через третий элемент НЕ, а второй выход блока принятия решений соединен со входами уста- 40 новки порогов срабатывания коррелятора прямого кода и коррелятора обратного кода, а также со входом четвертого элемента НЕ и со вторым входом четвертого элемента И, при этом выход четвертого элемента HE соединен с треть.45 им входом третьего элемента И, второй вход четвертого элемента И соединен с выходом второго элемента ИЛИ, причем выход четвертого элемента И соединен со входом формирователя кадрового интервала.

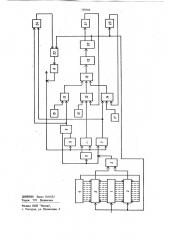

На чертеже приведена структурная схема устройства кадровой синхронизации.

Устройство содержит регистр 1 сдвига с фиксированными отводами, коррелятор 2 прямого кода, коррелятор 3 обратного кода, блок 4 памяти кода маркера, элемент ИЛИ 5, блок б обнаружения ложного маркера, блок 7 подтвер; ждения маркера, формирователь 8 кадрового интервала, элемент HE 9, блок 10 обнаружения пропуска маркера, элемент IIÅ 11, элементы И 12, 13 и 14, блоки 15, 16 и 17 формирования весовых коэффициентов, элемент ИЛИ

18, сумматор-накопитель 19, блок 20 принятия решений, элементы IE 21, 22, элемент И 23, элемент ИЛИ 24.

Устройство кадровой синхронизации работает следующим образом.

Входной сигал поступает на вход регистра 1 сдвига с фиксированными отводами, которые подсоединены ко входам корреляторов 2 и 3 прямого и обратного кода. При превышении сигналом порога в корреляторе и в зависимости от знака корреляции на выходе одного из корреляторов (второго или третьего) появится код маркера, который через элемент ИЛИ 5 поступает на входы блока 6 обнаружения ложного маркера и блока 7 подтверждения маркера непосредственно, а на блок 10 обнаружения пропуска маркера через элемент HE 11.

С выхода формирователя 8 кадрового интервала импульс синхронизирующего маркера поступает на вторые входы блоков 7 и 10 непосредственно и на блок б через элемент НЕ 9. При выделении сигнала блоком 6 он поступает на элемент И 12, второй вход которого соединен с блоком 15 формирования весового коэффициента. При выделении сигнала блоком 10 он поступает на элемент И 13, второй вход которого соединен с блоком 16 формирования весовых коэффициентов. При выделении сигнала блоком 7 подтверждения маркера он поступает на элемент И 14, второй вход которого соединен с блоком 17 формирования весовых коэффищ ентов.

Сигналы с выходов элементов И 12, 13, 14 через элемент ИЛИ 18 поступают на сумматорнакопитель 19, где происходит алгебраическое суммирование поступающих сипсалов с уже имеющейся там суммой. Если в сумматоре-накопителе 19 сумма меньше или равна О, то в корреляторах 2 или 3 устанавливается минимальный порог n> = n — k,, где n — число символов маркера, а k, — число исправляемых ошибок. Одновременно поступает запрет через элемент. НЕ 21 на элемент И 13, пропускающий импульс с блока 10 обнару>кения пропуска маркера, и открывается элемент И 23, разрешающий фазировку формирователя 8 кадрового интервала в состояние синфазное с импульсами, выделяемыми либо блоком б, либо блоком 7 и проходящих через элемент ИЛИ 24 на второй вход элемента И 23. Если в сумматоре-накопителе 19 сумма больше или равна 1, порог и, увеличивается, одновременно поступает запрет через элемент НЕ 22 на элемент И 14, Выход формирователя 8 кадрового интервала является выходом устройства.

Таким образом, в предлагаемом устройстве кадровой синхронизации за счет введения управляемого порога принятия решения в корреляторах и придания разных весов таким событиям как пропуск маркера, правильное его определение и ложное его определение, а также придания отдельным событиям при граничных состояниях сумматора-накопителя нулевых весов (неучет весов) повышается эффективность системы кадровой синхронизации, определяемая как величина обратная вероятности потери информации, на один — два порядка.

l5

Устройство кадровой синхронизации, содержащее регистр сдвига, выходы которого соединены с соответствующей первой группой входов коррелятора прямого кода и коррелятора обратного кода, вторые„группы входов которых

20 соединены соответственно с выходами блока памяти кода маркера, при этом выход коррелятора прямого кода соединен с первым входом первого элемента ЙЛИ, второй вход которого соединен с выходом коррелятора обратного кода, а выход первого элемента ИЛИ соединен с первыми входами блока подтверждения маркера и блока обнаружения ложного маркера, np>fчем ко второму входу блока обнаружения ложного маркера подключен выход первого элемен- З

30 та НЕ, вход которого соединен с выходом формирователя кадрового интервала и со вторым входом блока подтвержцения маркера, о тI л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости выделения синхронизирующего маркера, введены блок обнаружения пропуска маркера, первый, второй и третий блоки формирования весовых коэффициентов, второй, третий и четвертый элементы НЕ, первый, второй, третий и четвертый элементы И, второй и третий элементы ИЛИ, а также блок

40 .принятия решений и сумматор-накопитель, при этом выход первого элемента ИЛИ соединен

Формула изобретения

758564

6 с первым входом блока обнаружения пропуска маркера через второй элемент НЕ, а второй вход блока обнаружения пропуска соединен со входом первого элемента НЕ, со вторым входом блока подтверждения маркера и с входом формирователя кадрового интервала, при этом выход блока обнаружения пропуска маркера соединен с первым входом первого элемента И, ко второму входу которого подключен выход

l0 первого блока формирования весового коэффициента, выход блока обнаружения ложного маркера соединен с первым входом второго элемента ИЛИ и первым входом второго элемента И, второй вход которого соединен с выходом второго блока формирования весового коэффи-. циента, а выход блока подтверждения маркеоа соединен со вторым входом второго элемента

ИЛИ и с первым входом третьего элемента И, второй вход которого соединен с выходом третьего блока формирования весового коэффициента, причем выходы первого, второго и третьего элементов И соединены соответственно с первым, вторым и третьим входами третьего элемента

ИЛИ, выход которого соединен со входом блока принятия решений через сумматор-накопитель, при этом первый выход блока принятия решений соединен с третьим входом первого элемента И.через третий элемент НЕ, а второй выход блока принятия решений соединен со входами установки порогов срабатывания коррелятора прямого кода и коррелятора обратного кода, а также со входом четвертого элемента НЕ и со вторым входом четвертого элемента И, при этом выход четвертого элемента НЕ соединен с третьим входом третьего элемента И, второй вход четвертого элемента И соединен с выходом второго элемента ИЛИ, причем выход четвертого элемента И соединен со входом формирователя кадрового интервала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 554639, кл. Н 04 К 5/06, 1977 (прототип).