Устройство для сложения чисел в избыточной системе счисления

Иллюстрации

Показать всеРеферат

Союз Советския

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<„,763896 (61) Дополнительное к авт. сеид-ву (22) Заявлено 260678 (21) 2633734/18-24 (51)М. Кл.

G 06 F 7/50 с присоединением заявки N9 (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 1509.80, бюллетень Йо 34

Дата опубликования описания 25. 09. 80" (53) УДК 681=325.5(088.8) (72) Авторы изобретения

В.A.Телековец и В.В. Кашевский (71) Заявитель

Таганрогский радиотехнический институт им. В.Д.Калмыкова (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ В ИЗБЫТОЧНОИ

СИСТЕМЕ СЧИСЛЕНИЯ

Изобретение относится к цифровой вычислительной технике и может быть испоЛьзовано в вычислительных машинах, работающих в избыточной системе счисления.

Известно устройство для сложения нескольких двоичных чисел f1), содержащее несколько рядов одноразрядных двоичных сумматоров в каждом из блоков суммирования. В данном устройстве производится сложение только в двоичной системе счисления, т.е-. это устройство не позволяет выполнить суммирование нескольких чисел в избыточной системе счисления.

Известно устройство для сложения в избыточной системе счисления (,21, содержащее два комбинационных сум- матора, логические схемы,выработки положительного и отрицательного переносов и группу элементов ИЛИ.

Недостатком данного устройства является то, что оно производит сложение только двух чисел. Для сложения нескольких чисел требуется значительное увеличение оборудования, Кроме того, это устройство позволяет суммировать только в системе счисления с нечетным основанием.

Наиболее близким к предложенному является устройство для сложения

N чисел в избыточной системе счисления Я, содержащее в каждом иэ л разрядов два двоичных сумматора и сумматор в избыточной системе счи1О сления, в котором производится сложение нескольких чисел. Сумматор в двоичной избыточной системе счисления содержит четыре одноразрядных двоичных сумматора и два элемента запрета.

Это устройство производит сложение чисел только в двоичной избыточной системе счисления.

Цель изобретения - расширение

2О функциональных воэможностей,,т.е. обеспечение суммирования чисел в избыточной системе счисления с произвольным основанием.

Для достижения этой цели в каж25 дый.иэ и разрядов устройства, содержащий первый и второй двоичные сумматоры, первые группы входов которых соединены с N ° k шинами соответственно отрицательных и поло3р жительных значений соответствующе763896

50

60 го разряда слагаемых (1о g rake

1о9 р+1, где p — основание системы счисления), введен блок анализа.

Выходы k младших разрядов двоичных сумматоров подключены к 2k входам блока анализа, а выходы остальных разрядов первого и второго двоичных сумматоров i-ro разряда устройства подключены к вторым группам входов соответственно первого и второго двоичных сумматоров следующего (i+1)-ro разряда устройства. Выходы блока анализа соединены с отрицательными и положительными шинами результата.

При суммировании чисел в избыточной системе счисления с основанием

Р=2 блок анализа содержит k-разрядК ный двоичный сумматор, две группы элементов И и элемент НЕ.

Выход, переноса k-разрядного двоичного сумматора подключен к входу переноса первого разряда этого сумматора, к первым входам элементов И первой группы и через элемент НЕ к первым входам элементов И второй группы. Выходы элементов И первой и второй группы подключены к выходам блока анализа, а вторые входы— к выходу соответствующего разряда

k-разрядного двоичного сумматора, входы которого соединены с входами блока анализа.

При суммировании чисел в избыточной системе счисления с основанием

2 cpg.2.", блок анализа дополнительно. содержит первый и второй узлы коррекции, входы которых соединены с соответствующими входами блока анализа. Выходы переноса первого и второго узлов коррекции блока анализа i-го разряда устройства соединены с входсм переноса первого разряда соответственно первого и второго двоичных сумматоров следующего (i+1)-ro разряда устройства, а . выходы суммы первого и второго узлов коррекции соединены с соответствующими входами k-разрядного сумматора блока анализа.

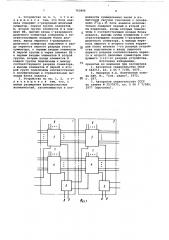

Структурная схема устройства для сложения N чисел в избыточной системе счисления приведена на фиг. 1; функциональная схема блока анализана фиг. 2.

Устройство содержит и разрядов, из которых на чертеже изображены

i-й разряд 1 и (i+1)-й разряд 2, состоящие каждый из первого двоичного сумматора 3, второго двоичного сумматора 4 и блока анализа 5.

Первая группа входов двоичного сумматора 3 соединена с М М шинами

6 отрицательных значений соответствующего разряда входных аргументов, а первая группа входов второго двоичного сумматора 4 соединена с и k шинами 7 положительных значений со5 t0

-ответствующего разряда входных аргументов.

Выходы (с младших разрядов двоичных сумматоров 3 и 4 соединены с 2 входами блока анализа 5, а выходы остальных разрядов первого и второго двоичных сумматоров 3 и 4 1-го разряда

1 устройства подключены к вторым группам входов соответственно первого и второго двоичных сумматоров 3 и 4 следующего (i+1)-ro разряда 2 устройства. Выходы блока анализа 5 соединены с выходными положительными 8 и отрицательными 9 шинами устройства.

Блок анализа 5 каждого разряда устройства содержит k-разрядный двоичный сумматор 10, k элементов

И 11, k элементов И 12 и элемент

HE 13. При суммировании чисел в избыточной системе счисления с основанием 2 срс2 блок анализа 5 дополнительно содержит первый узел коррекции 14 и второй узел коррекции 15.

Входы блока анализа 5 при этом подключены к входам соответствующего узла коррекций, выходы которых подключены к входам соответствующего разряда k-разрядного двоичного сумматора 10, а выход переноса сумматора 10 подключен к входу переноса первого разряда этого сумматора, к первым входам элементов И 11 и через элемент HE 13 — к первым входам элементов И 12.

Вторые входы элементов И 11 и 12 подключены к выходу соответствующего разряда сумматора 10, а выходы к выходам блока анализа 5.

Выходы переноса узлов коррекции

14 и 15 блока анализа.5 i-ro разряда 1 устройства подключены к входу переноса первого разряда соответственно первого и второго двоичных сумматоров 3 и 4 следующего (i+1)-ro разряда 2 устройства. При суммировании чисел в избыточной системЕ счисления с основанием р=2" входы блока анализа 5 непосредственно соединены с соответствующими входами разрядного сумматора 10.

Устройство работает следующим образом.

При поступлении входных аргументов по и k шинам 6 и 7 в двоичных сумматорах 3 и 4 образуется двоичный код суммы соответственно отрицательных и положительных цифр соответствующего разряда и входных аргументов, который суммируется с двоичным кодом состояния, поступающего со старших разрядов двоичных сумматоров 3 и 4 предыдущего (i-1)-ro разряда устройства, и на выходах двоичных сумматоров 3 и 4 образуются соответственно отрицательная и положительная m-разрядные двоичные суммы S, и S; .

763896

Иладаие k разрядов отрицательной S; и положительной S,- сумм с выходов k младших разрядов двоичных сумматоров 3 и 4 поступают в блок анализа 5, в котором двоичные разрядные положительное а, и отрицательное а, числа преобразуются в

k-разрядное число Z в избыточной системе счисления. При суммировании чисел в избыточной системе счисления с основанием => числа а ;

k а не могут быть больше (р-1), поэтому преобразование сводится к суммированию числа а. с числом а в обL ратном коде и анализу полученной суммы. 1

При суммировании чисел в избыточной системе счисления с основанием

1с-с 1< с а ра 2 числа а, и ас, может быть боль. ше (р- I ), поэтому блок анализа 5

i-го разряда 1 устройства должен вырабатывать сумму чисел ас и а и ь Е перенос в старший (!1-1)-й разряд

2 устройства. Узел коррекции 14, на выходах которого подается число а;, вырабатывает отрицательный перенос

Ь; и отрицательную сумму с;;

Ь =Оис. а, при a„ ð-1

b;=1 и с„— = a +p при а,ър-1

Узел коррекции 15, на входы которого подается число а;, вырабатывает положительный перейос Ь„и положительную сумму с :

30

Разряд устройства с

Zi

t а

S„ а (в;

01 00

00 00 010 000 10 00 10 00 2

01 00

00 00

00 11

10 00

00 00

10 00 010 010 10 10 00 00 0

00 01 001 100 01 00 01 00 1

00 00 100 001 00 01 00 01 1

00 00 001 000 01 00 01 00 1

00 10

01 00

10 00

00 00

3

2 3 0 1

2 1 2 1

0120

1 1 1 0 2

Таким образом, данное устройство позволяет производить сложение К чисел в избыточной системе счисления с основанием Р q p<2k, при этом каждый разряд числа в избыточной„ системе счисления передается по 2 шинам.

Формула изобретения

1. Устройство для сложения К чисел в избыточной системе счисления, содержащее в каждом из и раэря- бО дов первый и второй двоичные сумматоры, первые группы входов которых соединены соответственно с отрицательными и положительными шинами соответствующего разряда входных б5

Проверим результат сложения

Ь; =О и с =а; при а,;р-1

b, =1 и с,=а ; -p при ас .р-1

Сумматор 10 имеет k разрядов, на входы которых поступают двоичные числа с, (или а ; ) и с, (или а; ) .

На выходах сумматора 10 образуется сумма Z„, которая поступает на входы соответствующих элементов И

11 и 12, на другие входы которых поступает сигнал с выхода переноса сумматора 10. На входы элементов

И 11 поступает прямой сигнал переноса, а на входы элементов И 12 инверсный сигнал через элемент НЕ 13.

Соответственно на выходах элементов И 11 формируются положительные значения результата сложения Е;, которые поступают на положительные выходные шины 6 устройства в виде

-разрядного двоичного числа, а на выходах элементов И 12 формируются отрицательные значения результата сложения Z„., которые поступают на отрицательные выходные шины 9 устройства в обратном коде. Чтобы получить прямой код отрицательных значений результата, необходимо добавить k элементов НЕ (не показаны).

Пример сложения трех чисел

А-2301, В-21-"1 и С=0120, представленных цифрами 3, 2, 1, О, 1, 2, и 3 приведены в таблице (при k=2 и р=4) . ойерандов, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей, заключающегося в возможности суммирования чисел в избыточной системе счисления с основанием р=2, каждый из и раэ k рядов устройства содержит блок анализа, 2k входов которого соединены с выходами k младших разрядов двоичных сумматоров (l og p(k (l og>p+1., где р — основание системы счисления), выходы остальных (N- k) разрядов первого и второго двоичных сумматоров i-го разряда устройства подключены к вторым группам входов соответственно первого и второго двоичных сумматоров следующего (l+

+1)-го разряда устройства, à k положительных и к отрицательных выходов блока анализа подключены к отрицательным и положительным шинам результата устройства соответственно.

763896

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок анализа содержит k-разрядный двоичный сумматор, первую группу элементов

И, вторую группу элементов И и элемент НЕ, причем входы k-разрядного двоичного сумматора соединены с соответствующими входами блока анализа, выход переноса k-разрядного двоичного сумматора подключен к входу переноса первого разряда этого сумматора, к первым входам элементов

И первой группы и через элемент НЕк первым входам элементов И второй группы, вторые входы элементов И каждой группы подключены к выходу соответствующего разряда сумматора, а выходы элементов И первой и второй групп подключены соответственно к положительным и отрицательным выходам блока анализа.

3. Устройство по пп. 1, 2, о тл и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей, заключающегося в возможности суммирования чисел в избыточной системе счисления с,основаф,-1 нием 2 ср с 2, блок анализа дополни» тельно содержит первый и второй узлы коррекции, входы которых подключены к соответствующим входам блока анализа, выходы суммы соединены с соответствующими входами k-разрядного двоичного сумматора, а выходы переноса первого и второго узлов коррекции блока анализа i-го разряда устройства подключены к входу переноса первого разряда соответственно первого и второго двоичных сумматоров следующего (i+1)-го разряда устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство. СССР

9 484513, кл. G F 7/38, 1975.

2. Папернов A.A. Логические основы ЦВТ. М., "Сов. радио", 1972, 20 с. 187.

3. Авторское свидетельство СССР по заявке 9 2537875, кл. G 06 F 7/385, 1977 (прототип).

763896

Составитель Н.Слюсарев

Техред Ж. Кастелевич

Редактор Т.Орловская

Заказ 6284 42

Корректор E.Ïàïï

Подписное атент, г. Уягород, ул. Проектная, Тираж 751

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1130

035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП П