Устройство для умножения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ („)763897

I

4 г (61) Дополнительное к авт. свид-ву р )м. к.

G 06 F 7/52 (22) Заявлено 250178. (21) 2573690/18-24 с с присоединением заявки ¹Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (53) УДК 681. .325(088.8) Опубликовано 150980. Бюллетень Ко 34

Дата опубликования описания 25.09. 80 " (72) Авторы изобретения

Б.Г.Лысиков и A.A.Øoñòàê

Минский радиотехнический институт (71 ) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Изобретение относится к области вычислительной техники и может быть использовано при разработке быстродействующих устройств для умножения чисел в любой позиционной системе счисления, удобных для изготовления в составе больших интегральных схем .(БИС).

Известно устройство для умножения чисел (11, содержащее регистры миожимого и множителя, сумматор частичных произведений, цепи сдвига на оДин разряд в регистре множителя и в сумматоре частичных произведений, блок управления, выходы которого соединены с управляющими входами сумматора частичных произведений, регистров множи- мого и множителя.

Недостатком известного устройства является его низкое быстродействие, так как в каждом такте работы устройства обрабатывается только одна двоичная цифра (разряд) множителя.

Наиболее близким к изобретению аналогом является устройство для умножения, содержащее регистры мно жимого и множителя, накапливающий сумматор, п одноразрядных узлов умножения (и — разрядность множимого), п-разрядный комбинационный сумматор и блок управления, причем входы одноразрядных узлов умножения соединены с выходами соответствующих разрядов регистра множимого и с выходом первого разряда регистра множителя, а выходы соединены со входами комбинационного сумматора, выходы которого подключены ко входам накапливающего сумматора, а выходы блока управления подключены к управляющим входам регистров множимого и множителя и накапливающего сумматора. 1.23.

Это устройство может производитт

29 перемножение двух чисел в любой системе счисления с основанием N>2.

ОсобЫй интерес представляет умножение чисел в двоичнокодированной системе с основанием N-=2"Д где

25 каждый разряд операнда представляетая совокупностью k двоичных разрядов.

Недостатком этого устройства является недостаточное быстродей30 ствие, определяемое, в частности, 763897 быстродействием и-разрядного комбинационного сумматора.

Целью изобретения является повышение быстродействия.

Для достижения поставленной цели устройство для умножения, содержащее регистры множимого и множителя, накапливающий сумматор, и одноразрядных узлов умножения (n-разрядность множимого), и одноразрядных сумматоров и блок управления, выходы которого соединены с управляющими входами регистров и накапливающего сумматора, первый вход каждого одноразрядного узла умножения соединен с выходом соответствующего разряда регистра множимого, а второй вход — c выходом первого разряда регистра множителя, первый выход i-ro одноразрядного узла умножения (i=1,..., n) соединен с первым входом соответствующего одноразрядного сумматора, второй вход которого подключен ко второму выходу (i+1)-ro одноразрядного узла умножения, второй выход первого одноразрядного узла умножения соединен со входом младшего разряда накапливающего сумматора, входы остальных разрядов которого подключены к выходам одноразрядных сумматоров, содержит и узлов запоминания переноса, вход каждого иэ которых подключен к выходу переноса соответствующего одноразрядного сумматора, а выход — co входом переноса этого же одноразрядного сумматора, управляющие входы узлов запоминания переноса соединены с одним из выходов блока управления.

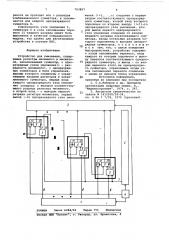

На чертеже приведена структурная схема быстродействующего устройства для умножения чисел.

Числа представленыв в двоичнокодированной системе счисления с основанием N=-2", т.е. каждый разряд множимого и множителя закодирован с помощью k двоичных разрядов.

Устройство содержит m-разрядные двоичные регистры 1, 2 соответственно множимого и множителя (где m=n:k), (m+k) — разрядный накапливающий сумматор 3, цепи однотактного сдвига на k разрядов в регистре 2 и в суммато »е 3 (на чертеже не показаны), блок 4 управления, выходы которого соединены с управляющими входами накапливающего сумматора 3 произвеДений, регистров 1, 2 соответствен-но множимого и множителя, п узлов одноразрядного умножения 5 (k-разрядного двоичного умножения), и одноразрядных сумматоров 6 (в данном случае — k-разрядных двоичных сум маторов), причем первый вход i-ro узла умножения 5 (i=i,...,ï) соединен с шиной 7 значения k младших двоичных разрядов регистра множителя

2, второй вход соединен с шиной 8 зна1О чения соответствующих k двоичных разрядов регистра множимого 1, à его выход 9 значения старших двоичных разрядов произведения соединен с первым входом соответствующего сумматора б, второй вход которого

15 соединен с выходом 10 значения младших двоичных разрядов произведения (i+1)-го узла умножения 5, а вход переноса соединен с выходом

i-го узла запоминания переноса 11, вход которого соединен с выходом

12 значения переноса сумматора б, а управляющий вход соединен с выходом блока управления 4, выход

13 значения суммы сумматора б со25,единен с соответствующим входом накапливающего сумматора 3, младший вход которого соединен с выходом 10 значения k младших двоичных разрядов произведения первого уз3() ла умножения 5.

В данном устройстве регистр множимого 1 может быть реализован на

i S-триггерах, регистр множителя

2 — на О-триггерах, накапливающий

З5 сумматор 3 — на 0- либо EK-триггерах с блоком ускоренного образования разрядных переносов, блок управления 4 — в виде управляющего автомата. Узел умножения 5 выполнен в виде логического шифратора k-разрядных кодов сомножителей в 2 k-разрядный код их произведения, синтез которого может быть проведен хорошо известными методами с использованием таблицы истинности. Ниже при45 ведены фрагменты таблицы истинности для узла k-разрядного умножения

5, причем для определенности принято, что ) =4. В таблице разряды множимого, поступающие по шине 8, 50 обозначены как m4» m » m>i mq разряды множителя, поступающие по шине 7, как п4, n>, n, п„,, а разряды 2 k-разрядного произведения на выходах 9, 10, узла k-разрядного

55 умножения 5 через Рв . p Рь р

Р » Р Р » Р1

7б 3897 и Ps Р Р Ps Р Р Р P "а mg и

П4 Пз П

О О О 0

0 0 О 0

О 0 О О

0 О О

О О О

0 О 1

1 1 1 1 О О О

1 1 1 1 О О 1

1 1 1 1 О 0 1

1 1 1 1 1 1 0

1 1 1 1 1 1 1

1 1 1 1 1 1 1

Однако следует отметить, что в определенных случаях может оказаться целесообразным реализация узла умножения 5 в виде пирамиды взаимосвязанных одноразрядных сумматоров, а также объединение узла умножения 5 и сумматора б в общую матрицу взаимосвязанных полных сумматоров (например с целью сокращения оборудования и обеспечения регулярности структуры операционного модуля). В данном устройстве в качестве узла запоминания переноса 11 может быть использован одноразрядный элемент. Например, им может быть двухтактный синхронный RS-триггер.

Устройство для умножения чисел работает следующим образом.

В исходном состоянии в регистре множимого 1 хранится m-разрядный двоичный код множимого, в регистре множителя 2 — m-разрядный код множителя (или, что ТОКеп-разрядные двоичнокодированные коды в системе счисления с основанием ,N=2" ), сумматор 3 обнулен (здесь предполагается m=8 и k=4, а сомножители представлены в виде положительных правильных дробей). Пусть множимое М=0,0001.1111; множитель

И=0,1111.1111; произведение Р=И К=

=0,0001.1110.1110.0001-0,0001..1110.

В устройстве данный результат будет получен следующим образом.

Пусть к началу первого такта работы устройства в узлах умножения

5 сформированы соответственно сле-. дующие произведения Ар=0001@1111-=0000.1111; В,=1111 1111=1110.0001, а в сумматорах б получены соответственно результаты С =0000; + =1110+

t1111=1101 (возникшая при этом единица переноса будет записана в узле запоминания переноса 11 младшего разряда).

1-й такт: осуществляется прием

1информации в сумматор 3, ее .сложение с содержимым сумматора 3, после че- .

0 0 О О О О О 0 О

1 0 0 О О 0 О 0 О

0 О О О О О О О О

В °

1 О О О О 1 1 1 1

0 О О О 1 1 1 1 О

1 О О 1 О 1 1 О 1

1 1 1 О О О О 1 1

О 1 1 0 1 О О 1 О

1 1 1 1 О О О О 1

ro осуществляется одньтактный сдвиг

QQ в сумматоре 3 информации на четыре разряда в сторону его младших разрядов. В итоге содержимое сумматора равно р =,OOOO. OOOO.OOOO+,OOOO. 11O1.

25,0001=t0000 ° 1101 ° 0001 = t0000 ° Оооое .1101.

Одновременно с этим в регистре множителя 2 был осуществлен однотактный сдвиг информации на четыре разgp ряда в сторону его младших .разрядов и были сформированы результаты

А =0001 1111--0000.11113 В =1111"

x1111=1110 0001 С =0000; 0 =1110+

+1111+0001=1110 (возникшая при этом единица переноса записывается в узле запоминания переноса 11 младшего разряда).

2-й такт: в данном такте и всех последующих осуществляется последовательность, действий, аналогичная

4О первому такту. В итоге выполнения второго такта получают следующие результаты . Р =P +,OOOO. 111O.OOO1=,OOOO. OOOO.

1101+,0000.1110.0001=,0000,1110.

45 1110 -,оооо. оооо.1110 A -0001x

B,=1111 OOOO=

=оооо.оооо с =оооо o =oooo+oooo+

+0001=0001.

3-й такт (такт окончательного уче 50 та переносов): в итоге получаем

=,OOOO -OOOO 111O+,OOOO.ООО1 .0000=,0000.0001.1110..

На этом процесс умножения заканчивается, окончательный результат сформирован в m младших разрядах сумматора 3 частичных произведений.

Как уже указывалось, подобное умножение в принципе может быть осуществлено для любой системы

60 счисления с основанием й72, в том числе, например, для:Ь-ичнокодированных операндов в системе счисления с основанием М=Ь".

Время операции при этом сокраща65 ется, за счет того, что сигнал пе763897

Формула изобретения

25

Заказ 6284/42 Тираж 751 Подписное

ВНИИПИ

Филиал ШШ "Патент", r. Ужгород, ул. Проектная, 4 реноса не проходит все и разрядов комбинационного сумматора, а запоми- нается для каждого одноразрядного сумматора 6.

Совокупность узла умножения 5, сумматора 6 и узла запоминания переноса 11 каждого разряда может быть выполнена в качестве операционного модуля, что удобно для изготовления устройства в составе БИС, Устройство для умножения, содержащее регистры множимого и множителя, накапливающий сумматор, и одноразрядных узлов умножения(п - разрядность множимого), и одноразряд-. ных сумматоров и блок управления, выходы которого соединены с управляющими входами регистров и накапливающего сумматора, первый вход каждого одноразрядного узла умножения соединен с выходом соответствующего разряда регистра множимого, а второй вход — с выходом первого разряда регистра множителя, первый выход i ãî одноразрядного узла умно.жения (i=1,,п) соединен с первым входом соответствующего одноразрядного сумматора, второй вход которого подключен ко второму выходу (i+1)-го одноразрядного узла умножения, второй выход первого одноразрядного узла умножения соединен со входом младшего разряда накапливающего сумматора, входы остальных разрядов которого подключены к выходам одноразрядных сумматоров, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, устройство содержит и узлов запоминайия переноса, вход каждого иэ которых подключен к выходу переноса соответствующего одноразрядного сумматора, а выход — со входом переноса этого же одноразрядного сумматора, управляющие входы узлов запоминания переноса соединены с одним из выходов блока управления.

Источники информации, принятые во внимание при экспертизе

1. С.А.Майоров и др. Принципы органиэации цифровых машин, Л., "Машиностроение", 1974, с. 297.

2. Авторское Свидетельство по заявке Р 1412260/18-24, кл. G 06 F 7/39, 1970 (прототип).