Динамический элемент памяти

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцнапнстнческни

Республик

ОП ОСАНКЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

,763966 (6I ) Дополнительное к ввт. свнд-ву (22) Заявлено 02.01. 78(21) 2566728/18-24 (51)M. Кл.

Я 11 С 11/34

G 11 С 11 40 с присоединением заявки ¹

Гооударстееииый комитет

СССР (23) Приоритет по делам изобретений и открытий

Опубликовано 15,09.80, Бюллетень ¹ З4

Дата опубликования описания 18.09 80 (53) УДК - 681.327.. 6 7 (088.8) (72) Автор изобретения

B. В. Пастон (7I) Заявитель (54) ПИНАМИЧЕСКИЙ ЭЛЕМЕНТ ПАМЯТИ 1

Изобретение относится к вычислительной технике и может быть испопь» зовано в запоминающих устройствах автоматики.

Известен динамический элемент памяти, выполненный в виде р-тт-р-q прибора, т -эмиттер которого подсоединен к разрядной шине, à р -эмиттер к числовой $1).

Недостатком такой ячейки при работе в составе матрицы накопителя является то, что цикл изменения информации включает операцию стирания целого слова накопитепя и операцию записи в выбранные ячейки этого же слова, что приводит к уменьшению быстродействия, усложнению схем управления, увеличению потребляемой мощности в составе запоминающего ус тройства.

Известен также полупроводниковый запоминающий элемент на одном транзисторе с неподклточенной базой. Транзистор работает, как двухэлектродный прибор, коллектор которого соединен с генератором импульсов напряжения, а эмиттер-со схемой обнаружения тока 21.

Недостатком этого запоминающего элемента является то, что для записи информашти между коллектором и эмитттером транзистора требуется значителт ная разность потенциалов (около 6-7 то

В), так как элемент памяти работает в режиме пробоя одного из переходов, что существенно снижает срок его службы. Запись и считывание требуют многоуровневых управпятоптих сигналов, что усложняет организацию выборочного поэпементного управления.

Наиболее близким техническим решением к данному изобретенито является динамический элемент памяти с двумя электрическими выводами, со. держшций биполярный и полевой транзисторы, причем эмиттер бипопярного и исток полевого транзисторов подключены к первому и второму выводу

7639

15

25

40

50

3 соответственно, база биполярного подключена к стоку, а коллектор биполяр ного к затвору полевого транзистора (3).

Недостатком этого элемента памяти является то, что при перезаписи информации в ячейках памяти в составе матрицы накопителя требуется предварительный опрос ячеек всего слова для поддержания на разрядных шинах определенного режима, неразрушающего информацию в ячейках, в кото» рых информация при цикле перезаписи должна быть сохранена. Зто приводит к снижению быстродействия запоминающего устройства и увеличению рассеиваемой мощности.

Целью изобретения является уменьшение потребляемой мощности динамического элемента памяти.

Поставленная цель достигается тем, что в динамическом элементе памяти, содержащем биполярный транзистор, коллектор и база которого подключены соответственно к затвору и истоку полевого транзистора, а эмиттер — к одной иэ двух шин управления, сток полевого транзистора подкпючен к эмиттеру биполярного транзистора, база которого подключе»на к другой шине управления.

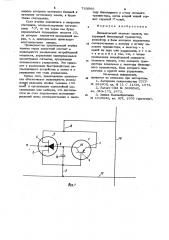

На фиг. 1 представлена схема элемента памяти; на фиг. 2-4 — возможные варианты конструктивного выполнения этой схемы.

Динамический элемент памяти содержит биполярный транзистор 1 и полевой транзистор 2, связаннь1е между собой так, что исток 3 полевого транзистора и база 4 биполярного транзистора подключены к выводу 5, а сток 6 полевого транзистора и эмиттер 7 биполярного транзистора подсоединены к выводу 8. Затвор 9 полевого транзистора подключен к коллектору 10 биполярного транзистора, исток 3 и сток 6 соединены кана.лом 11. Выводы 5 и 8 подключены соответственно к шинам 12 и 13 управления.

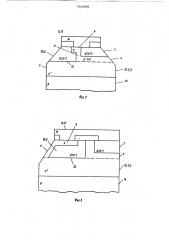

При интегральном выполнении описываемая ячейка представляет собой следующую структуру: на рподложке 14 расположен п -скрытый слой 12, являющийся одновременно шиной 12 и истоком 3 полевого транзистора. На слое 12 выполнены h (й)-слой 4, являющийся базой биполяр66 ф ного транзистора, а (nj-êàíàë 11 полевого транзистора, p(p) -затвор 9 полевого транзистора, являющийся коллектором биполярного транзистора, P(p ) -эмиттер 7 биполярного транзистора, соединенный общим электрическим контактом в виде проводящей металлической шины 13 с и -стоком

6 полевого транзистора.

Работа ячейки основана на возможности хранения двоичной информации в зависимости от того, в проводящем (логическая "1 ) или непроводящем (логический "0 ) состоянии она находится. Запись логического "0" осуществляется следующим образом: на вывод

5 подается импульс положительной полярности, на выводе 8 в это время устанавливается потенциал, близкий к нулевому потенциалу. В результате между выводами ячейки устанавливается разность потенциалов, достаточная для заряда барьерной емкости 15, образованной полупроводниковыми области. ми затвора и истока полевого транзистора. В результате введения запирающего заряда на барьерную емкость 15 р- .-перехода объемный заряд в канале полевого транзистора увеличивается, что приводит к переводу ячейки в не»проводящее состояние.

Запись логической 1 или перевод ячейки в проводящее состояние происходит так: на вывод 8 подается импульс положительной полярности, на выводе

5 устанавливается потенциал, смещаю щий р-д -переход эмиттера биполярного транзистора в прямом направлении. В результате инжекции эмиттерным переходом носителей зарядл в область коллектора биполярного транзистора, являющегося затвором полевого транзистора„ p H 3 p 3 0pe рассасывается, объемный заряд в канале сокращается, и ячейка переходит в проводящее состояние.

При считывании на вывод 5 подает ся импульс попожительной полярности, а вывод. 8 подключается через шину

13 к нагруэочному сопротивлению

7„=101 „0, где g - сопротивление канаQP ла в проводящем состоянии. Если ячейка находилась в состоянии логической ю °

1, т. е. была открыта, то между выводами 5 и 8 устанавливается напряжение М (ЧП/1О, гДе V< — амплитУда напряжении импульса на выводе 8. Ток, проходящий в этот момент через канал ячейки и сопротивление Pg на втором

5 выводе которого потенциал близкий к нулевому потенциалу земли, и будет током считывания.

Если ячейка находилась в закрытом состоянии, соответствующем логичес кому 0, то ток через нее будет определяться подзарядом емкости 15, на котором находится запирающий заряд, т. е. <одновременно происходит восстановление заряда.

Преимущество предложенной ячейки памяти перед известной состоит в воэможности уменьшения потребляемой мощности, управлении одноуровневыми амплитудами сигналов, организации поэлементного управления.. Это приводит к увеличению быстродействия запоминающего устройства в целом и к упрощению его схем управления.

Кроме того, предложенное выполнение обеспечивает возможность уменьшения размеров ячейки (меньше 100 мкмжд и организацию однослойной металлиэации шин выборки, что достигается за счет подключения металлизированной шины непосредственно к эмитФормула изобретения динамический элемент памяти, содержащий биполярный транзистор, коллектор и база которого подключены соответственно к затвору и истоку полевого транзистора, а эмиттер - к одной из llsyx шин управления, о т л и ч а ю шийся тем, что, с целью уменьшения потребляемой мощности элемента памяти, сток полевого транзистора подключен к эмиттеру биполяр-ного транзистора, база которого подключена к другой шине управления.

Источники информации, принятые во внимание при экспертизе.

1. Авторское свидетельство СССР № 391609, кл. Cj 11 С 11/34, 1972.

2. Патент США ¹ 3699540, кл. 340-173, 1973.

3. Зывка Великобритании

¹ 1429846, кл. Н3Т, 1976 (прототип).

1S

25

763966 6 теру биполярного и стоку полевого транзистора, когда второй шиной служит скрытый h+wлой.

763966

Составитель Ю. Ушаков

Редактор Н. Каменская Техред Н. Бабурка Корректор ph, Шароши

Заказ 62 92/45 Тираж 662 Подписное

ИНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4