Полупроводниковое постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз CQB97cKHx

Социалнстическик

Республик

<1,763968 (61) Дополнительное к авт. сеид-ву (22) Заявлено 200278 (2t) 2581254/18-24 (51)М. Кл 3 с присоединением заявки №

С 11 С 17/00

Государственный комитет

СССР во делам изобретений н открытий (23) Приоритет

Опубликовано 1509.80. Бюллетень ¹ 34 (53) УДК б 81. 327.28 (088. 8) Дата опубликования описания 15pq80 (72) Авторы изобретения

И.Я.Козырь и О,A,Ïåòðîñÿí (71) Заявитель

Московский институт электронной техники (54) ПОЛУПРОВОДНИКОВОЕ ПОСТОЯННОЕ

ЗАПОМИНИОЩЕЕ УСТРОЙСТВО

Изобретение относится к вычисли тельной технике и автоматике и может быть использовано в устройствах обработки цифровой информации в ка5 честве табличных данных, программ, подпрограмм, преобразователей кодов и др.

Иэ вес тно полу про води и ко все з а поминающее устройство, содержащее запоминающие транзисторы с инжектором р-типа с базовыми диодами Шоттки (l), Наиболее близким техническим решением к изобретению является полупроводниковое постоянное запоминающее устройство, содержащее адресные формирователи, инвертор разрешения выборки, элементы дешифратора, транзисторы матрицы и усилители счйтывания (2 .

Недостатками этих полупроводниковых постоянных запоминающих устройств является низкая степень интеграции, что ограничивает информационную емкость устройства.

Цель изобретения — повышение сте" пени интеграции полупроводникового постоянного з апоминающего устройства. 30

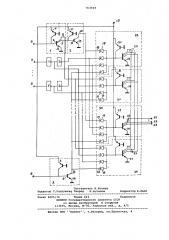

Поставленная цель достигается тем, что полупроводниковое постоянное запоминающее устройство содержит запоминающие транзисторы с инжектором р-типа с баэовыми диодами Шоттки, коллекторы которых соединены с соответствующими выходами устройства, эмиттеры — с шиной нулевого потенциала, а катоды диодов Шоттки с соответствующими вторыми коллекторами первых адресных и коллекторами вторых адресных транзисторов с инжектором р-типа, а также с коллектором управляющего транзистора с инжектором р-типа, причем инжекторы транзисторов подключены к шине питания, На чертеже представлена электрическая схема полупроводникового постоянного запоминающего устройства.

Полупроводниковое постоянное запоминающее устройство содержит адресные первые 1 и вторые 2 транзисторы с инжектором р-типа, а также— управляющий транзистор 3 с инжектором 4 р-типа, база 5 которого и ба-. зы б адресных первых транзисторов

1 с инжектором 7 р-типа соединены с соответствующими входами 8 уст763968

1О

20 формула изобретения

35

45

55

65 ройства, а первые коллекторы 9 адресных первых транзисторов 1 с инжек тором 7 р-типа — с базами 10 соответствующих адресных вторых транзисторов 2 с инжектором 11 р-типа, эмиттеры 12 адресных первых транзисторов 1 .с инжектором 7 р-типа, эмиттеры 13 адресных вторых транзисторов 2 с инжектором 11 р-типа и эмиттер 14 управляющего транзистора 3 с инжектором 4 р-типа соединены с шиной нулевого потенциала (на чертеже она не нумерована), а инжекторы

4, 7 и 11 — к шине 15 источника питания, при этом вторые коллекторы 9 адресных транзисторов 1 с инжектором 7 р-.типа, коллекторы 16 адресных транзисторов 2 с инжектором 11 р-типа и коллектор 17 управляющего транзистора 3 с инжектором 4 р-типа соединены с соответствующими катодами

18 базовых диодов 19 Шоттки запоминающих транзисторов 20 с инжектором

21 р-типа, коллекторы 22 которых соединены с соответствующими выходами

23 устройства, а эмиттеры 24 — с шиной нулевого потенциала, причем инжекторы 21 подключены к шине 15 источника питания.

Полупроводниковое постоянное запоминающее устройство работает сле дующим образом.

На входы 8 устройства (базы 6 адресных первых транзисторов 1 с инжектором 7 р-типа и базу 5 управляющего транзистора 3 с инжектором 4 р-типа) подается код адреса (комбинация сигналов низкого и высокого уровня напряжения на базы б адресных первых транзисторов 1 с инжектором

7 р-типа и низкий уровень напряжения на базу 5 управляющего транзистора 3 с инжектором 4 р-типа). При этом на катодах 18 базовых диодов 19 Шоттки выбранного запоминающего транзистора 20 с инжектором 21 р-типа устанавливаются высокие уровни напряжения. В результате из выбранного з апоминающего транзистора 20 с инжектором 21 р-типа считывается соответствующее слово и на его коллекторах 22 (выходах 23 устройства, так как одноименные коллекторы 22 запоминающих транзисторов 20 с инжектором 21 р-типа объединены и выполняют функцию монтажной ИЛИ) появляются высокие (0,6О, 7В) уровни напряжения, если коллекторы 22 разомкнуты (не подключены к выходам 23 устройства),. и низкие (<О, 1В) уровни напряжения, если коллекторы 22 не разомкнуты (подключены к выходам 23 устройства), что сооТветствует считанному слову.

Таким образом, предлагаемое полупроводниковое постоянное запоминающее устройство по сравнению с известным отличается повышенной степенью интеграции, которое обеспечивается введением запоминающих транзисторбв

20 с инжектором 21 р-типа с базовыми диодами 19 Шоттки (занимающий площадь от 1500 мкм до 5000 мкм и имеющий быстродействие от 5 нс до 15 нс) и тем, что инжекторы 21 р-типа обеспечивают подвод питания не только к запоминающим транзисторам 20, но и к соответствующим адресным первым 1 и вторым 2 транзисторам с инжектором р-Tèïà через соответствующие базовые диоды 19 Шоттки, Это позволяет реализовать постоянное запоминающее устройство 16 Кбит на кристалле размером 4х4 мм, Полупроводниковое постояннбе запоминающее устройство сохраняет работоспособность в широком диапазоне изменения напряжения питания (1В6. (Еп(15В) соответственно рабочего тока инжектора (10 мАС In(lмА), а так-б же температуры окружающей среды (-60o С cT4+125o С), Полупроводниковое постоянное запоминающее устройство, содержащее управляющий и первые и вторые адресные транзисторы с инжектором р-типа, причем базы управляющего и первых адресных транзисторов с инжектором р-типа соединены с соответствующими входами устройства, а первые коллекторы первых адресных транзисторов с инжектором р-типа — с базами соответствующих вторых адресных транзисторов с инжектором р-типа, эмиттеры адресных и управляющего транзисторов с ийжектором р-типа соединены с ши,ной нулевого потенциала, о т л и ч а ю щ е е с ятем, что, с целью повышения степени интеграции устройства, оно содержит запоминающие транзисторы с инжектором р-типа с базоными диодами Шоттки, коллекторы которых соединены с соответствующими выходами устройства, эмиттеры — с шиной нулевого потенциала, а катоды диодов Шоттки — с соответсвующими вторыми коллекторами первых адресных и коллекторами вторых адресных транзисторов с инжектором р-типа, а также с коллектором управляющего транзистора с инжектором р-типа, при. чем инжекторы транзисторов подключены к шине питания, Источники информации, принятые во внимание при экспертизе

1. Фурсин Г. И, Фун кцион альные интегральные схемы и инжекционным питанием и активной связью на биполярных приборах.- Микроэлектроника, т.б, вып.2, с..108-126, 1977, 2. Щетинин Ю,И,, Крамаренко О.Л

Неклюдов В,А. . Монолитное ПЗУ 155РЕ1 емкостью 25ббит со схемами управления-.

Сб. Микроэлектроника и полупроводниковые приборы, вып. 1. Сов. радио, 1976, с. 50-58 (прототип) .

763968

Сос т а выт ел ь И. Козырь

Редактор С.Патрушева Техред И.Асталош

Корректор Е.Папп

Заказ 6605/16 Тираж 66 2 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035., Москва, К-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная, 4