Генератор напряжения смещения подложки в мдп-интегральных схемах

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ изоь етиния

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социапнстмческмк

Респубпмк

1

< (61) Дополнительное к авт. свид-ву— (51) М.К .з (22) Заявлено 24.05.78 (21) 2621297/18-21 с присоединением заявки №вЂ”

Н 03 В 5/36

Государственный комитет

СССР (23) Приоритет—

Опубликовано 15.09.80. Бюллетень № 34 (53) УДК 621.373 (088.8) ио деиам изобретений и открытий

Дата опубликования описания 23.09.80

С. С. Булгаков, А. И. Стоянов, С. А. Еремин, В. A. Сухоруков и В. С. Хорошунов (72) Авторы изобретения (71) Заявитель (54) ГЕНЕРАТОР НАПРЯЖЕНИЯ СМЕЩЕНИЯ ПОДЛОЖКИ

В МДП-ИНТЕГРАЛЬНЫХ СХЕМАХ

Изобретение относится к области вычислительной техники и предназначено для построения МДП-устройств в интегральном исполнеттии.

Известен генератор напряжения смещения подложки, состоящий из детектора порогового напряжения, кольцевого генератора и блока формирования напряжения смещения подложки (1).

Недостатками известного устройства является низкая чувствительность детекторов порогового напряжения, что обусловливает значительное отклонение пороговых напряжений транзисторов МДП-ИС от номинальных значений, а также высокая статическая мощность потребления детектора.

Ближайшим по технической сущности к данному изобретению является генератор напряжения смещения подложки в МДПустройствах, состоящий из детектора порогового напряжения, кольцевого генератора, формирователя и блока формирования напряжения смещения подложки; делитель напряжения детектора порогового напряжения выполнен на двух МДП-транзисторах, затворы которых и сток первого из них подключены к шине питания; исток второго из транзисторов делителя подсоединен с шине нулевого потенциала, исток первого транзистора и сток второго транзистора соединены с выходом делителя напряжения; инвертор детектора порогового напряжения выполнен на переключающем и нагрузочном

МДП-транзисторах; выход делителя напряжения соединен с затвором переключающего транзистора; исток переключающего тран1п зистора подключен к шине нулевого потенциала, сток нагрузочного транзистора подключен к шине питания, сток переключающего и исток нагрузочного транзисторов связаны с первым входом формирователя напряжения, к второму входу которого подсоединен выход кольцевого генератора, выход формирователя напряжения соединен со входом блока формирования напряжения смещения подложки, выход которого непосредственно связан с подложкой интегральной схемы (2).

Недостатками прототипа являются зна-, чительное отклонение порогового напряжения транзисторов интегральной схемы вследствие низкой чувствительности детектора

?64097

5$

zo ральной шины

4$

so

55 и большая статическая мощность потребления детектора.

Действительно, выходной элемент детектора состоит из инвертора, чувствительность которого определяется крутизнои передаточной характеристики и при выборе крутизны транзисторов, достаточно приемлемой с топологической точки зрения, не обеспечивается высокая чувствительность выходного ивертора. Кроме того, делитель напряжения и выходной инвертор построены по статическому принципу, что вызывает зна- чительное потребление мощности.

Целью изобретения является повышение чувствительности и уменьшение статической мощности потребления устройства.

Цель достигается тем, что в генератор напряжения смещения подложки в МДП-интегральных схемах, который содержит детектор порогового напряжения, образованный. делителем напряжения и инвертором, выполненным на переключающем и нагрузочном МДП-транзисторах, причем выход делителя напряжения соединен с затвором переключающего транзистора, исток которого подключен к шине нулевого потенциала, сток нагрузочного транзистора — к шине питания, сток переключающего и исток нагрузочного транзисторов объединены, ко второму входу формирователя напряжения подсоединен выход кольцевого генератора, а выход формирователя напряжения- соеди нен со входом блока формирования напряжения смещения подложки, между выходом детектора порогового напряжения и первым входом формирователя напряжения включен дифференциальный усилитель, второй вход которого подсоединен к выходу делителя напряжения детектора порогового напряжения.

Делитель напряжения в первом варианте изобретения выполнен на двух МДП-транзисторах, затворы которых и сток первого из них подключены к затвору и стоку нагрузочного транзистора, исток второго транзистора делителя подсоединен к шине нуле» вого потенциала, а исток первого и сток. второго транзисторов соединены с выходом делителя. напряжения.

Во втором варианте выполнения устройства делитель напряжения выполнен на двух конденсаторах, объединенные выводы которых подключены к выходу делителя напряжения; вторые выводы первого конденсатора подсоединены к затвору нагрузочного транзистора инвертора и к выходу кольцевого генератора, а второго конденсатора — к шине нулевого потенциала.

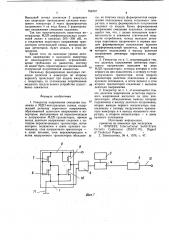

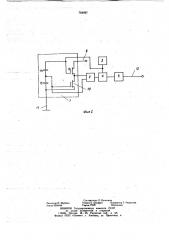

На фиг. 1 представлен генератор напряжения, в котором делитель напряжения детектора порогового напряжения выполнен на двух МДП-транзисторах; на фнг. 2— то же, делитель напряжения выполнен на двух конденсаторах.

Генератор напряжения состоит из детектора порогового напряжения l, диффе. ренциального усилителя 2, кольцевого генератора 3, формирователя напряжения 4 и блока 5 формирования напряжения смещения подложки.

В первом варианте выполнения устройства делитель напряжения образован

МДП-транзисторами 6 и 7, затворы которых, а также сток транзистора 7 подключены к шине питания 8, к которой также подсоедииены затвор и сток нагрузочного МДП-транзистора 9 выходного инвертора. Исток транзистора 9 объединен со стоком переключающего МДП-транзистора 10 и подсоединен к первому выходу детектора порогового напряжения 1, который соединен с первым входом дифференциального усилителя 2.

Истоки транзисторов 6 и 10 подсоединены к шине нулевого потенциала 1l. Сток транзистора 6 объединен с истоком транзистора 7, с затвором транзистора 10 и со вторым входом дифференциального усилителя 2.

Выход дифференциального усилителя 2 подключен к первому входу формирователя напряжения 4, ко второму входу которого подсоединен выход кольцевого генератора 3.

Выход формирователя напряжения 4 соединен со входом блока 5, выход 12 которого непосредственно связан с подложкой интегВ устройстве по второму варианту делитель напряжения образован конденсаторами 13 и 14, средние выводы которых соединены с затвором транзистора 10 и со вторым входом дифференциального усилителя 2:

Второй вывод конденсатора 12 соединен

-с истоком транзистора 10 и с шиной нулевого потенциала 11. Второй вы вод конденсато. ра 13 подключен к затвору транзистора 9 и к выходу кольцевого генератора 3.

В остальном конструкция генератора по этому варианту та же, что и по первому варианту.

Предлагаемый генератор напряжения работает следующим образом.

Делитель напряжения формирует на затворе переключающего транзистора 10 выходного инвертора некоторый опорный уровень напряжения, который в общем случае не связан с номинальным пороговым напряжением. При этом соотношение крутизны транзисторов 9 н 10 выходного инвертора выбирается таким, что на выходе инвертора (стока транзистора 10) формируется уровень напряжения, близкий к напряжению на затворе транзистора !О. Если значение порогового напряжения выше или ниже номинального, то на входах дифференциального усилителя 2 формируется разность напряжений, фиксируемая усилителем, При этом на выходе усилителя устанавЛивается уровень напряжения в соответствии со знаком приращения напряжения на выходе детектора 1 (выходное напряжение делителя напряжения не зависит от значения порогового напряжения транзисторов 6 и 7).

764097

Выходной сигнал усилителя .2 разрешает или запрещает прохождение сигналов кольцевого генератора 3 через формирователь напряжения 4 на вход блока 5 формирования напряжения смещения подложки, Так как чувствительность известных интегральных МДП-дифференциальных усилителей лежит в пределах 200 — 300-мВ, то и отклонение порогового напряжения транзисторов интегральной схемы, контролируе- мых детектором, будет лежать в этих же пределах.

i0

Кроме того, на выходные уровни делителя напряжения и выходного инвертора не накладывается никаких ограничений,. кроме требования их равенства, поэтому, он может быть спроектирован с минимальной статической потребляемой мощностью.

Поскольку формирование выходных сигналов делителя и инвертора по второму варианту происходит при подаче импульса с генератора, то статическая потребляемая мощность предлагаемого устройства сущест- >е венно снижается.

Формула изобретения

l. Генератор напряжения смещения под. ложки в МДП-интегральных схемах, содержащий детектор порогового напряжения; образованный делителем напряжения и ннвертором, выполненным на переключающем и нагрузочном МДП-транзисторах, причем выход делителя напряжения соединен с затвором переключающего транзистора, исток которого подключен к шине нулевого потенциала, сток нагрузочного транзистора— к шине питания, сток переключающего н исток нагрузочного транзисторов объедине- и ны, ко второму входу формирователя напряжения подсоединен выход кольцевого генератора, а выход формирователя напряжения соединен со входом блока формирования напряжения смещения подложки, отличающийся тем, что, с целью повышения чувствительности и снижения статической мощности потребления, между выходом детектора порогового напряжения и первым входом формирователя . напряжения включен дифференциальный усилитель, второй вход которого подсоединен к выходу делителя напряжения детектора порогового напряжения.

2. Генератор по п. 1, отличающийся тем, что делитель напряжения детектора поро-. гового напряжения выполнен на двух

МДП-транзисторах, затворы которых и сток первого из них подключены к затвору и стоку нагрузочного транзистора, исток второго транзистора делителя подсоединен к шине нулевого потенциала, а исток первого и сток второго транзисторов соединены с выходом делителя напряжения.

3. Генератор по п. I, отличающийся тем, что делитель напряжения детектора порогового напряжения выполнен на двух конденсаторах, объединенные выводы которых подключены к выходу делителя напряжения, вторые выводы первого конденсатора подсоединены к затвору нагрузочного транзистора инвертора и к выходу кольцевого генератора, а второго конденсатора — к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

I. 1976/IEEE International Solid-State

Cirl ui ts Conference (ISSCC-76), Digest

of Technical Papers.

2. Электроника, № 4, 1976, с. 47, 764097

Составитель Л. Колосков .

Редактор И. Шубина Техред К. Шуфрнч Корректор Г. Решетник

Заказ 6300/48 Тнраж 991 Подпнсное

ВНИИПИ Государственного комитета СССР по дела м нзобретенай н открытнй

I )3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патентз, г. Ужгород, ул. Проектная, 4