Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАН

ИЗОБРЕТЕНИЯ.-.:ЛТ ПН0- ÄlgÄ. . . „,.

И-4

Союз Советских

Социалистическими

Респу6лмк

3}Ih M 1

< 4"т12

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дош>лиительное к авт. свил-ву (22) Заявлено 24.07.78 (2I ) 2647691/18-21 (51) М, Кл.

Н 03 К 5/153 с присоелинением заявки J%—

Государстввнный комнтет (2;3) Приоритет (53) УДК 641.373 (088.8) па делам нэобретеннй н открытнй

ОпУбликовано 15.09.80. Вюл.плетень ¹ 34

Дата опубликования описания 15.09.80 (72) Автор изобретения

М. В. Мелень

Львовский ордена Ленина политехнический институт (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к импульсной технике и может быть использовано в цифровых вычислительных машинах, цифровых измерительных приборах и в цифровых преобразователях.

Известны устройства синхронизации, содержащее триггеры, элементы совпадения и инверторы (1).

Недостаток известных устройств — низкая точность измерения.

Из известных устройств наиболее близким по технической сущности к предложенному является устройство тактовой синхронизации, содержащее запоминающий и управляющий триггеры, два элемента И-НЕ, инвертор и логический формирователь импульсов (2).

Недостатками известного устройства тактовой синхронизации являются низкое быстродействие и низкая точность синхронизации.

Бель изобретения — повышение быстродействия и точности синхронизации устройства.

Поставленная цель достигается тем, что в устройство синхронизации, содержащее последовательно соединенные запоминающий и управляющий триггеры и первый элемент И-НЕ, последовательно соединенные инвертор. и второй элемент И-НЕ, второй вход которого подключен к инверсному выходу запоминающего триггера, а выход второго элемента И-НЕ соединен с нулевым входом управляющего триггера, а также логический формирователь импульсов, тактовый вход которого соединен со вторым входом первого элемента И-HF и с шиной тактовых импульсов, введены два дополнительных триггера, два дополнительных элемента И-HE

10 и элемент И, первый вход которого соединен с инверсным выходом управляющего триггера, второй вход элемента И соединен с выходом первого дополнительного элемента И-НЕ и с

15 первым входом второго дополнительного элемента И-НЕ, первый вход первого дополнительного элемента И-HE подключен к тактовому входу логического формирователя, а второй и третий входы первого дополнительного элемента И-HE соединены с прямыми выходами первого и второго дополнительных триггеров, при этом нулевые входы дополнительных триггеров соединены с выходом логического формирователя импульсов, инверсные Bf>l764112 хoды первого и второго дополнительных триггеров соединены с информационными входами — " второго и первого дополнительных триггеров соответственно, синхровходы первого и второrî дополнительных триттеров подключены к шине управляющих импульсов и к шине тактовых импульсов соответственно, выход элемента И соединен с нулевым входом запоминающего триггера. второй вход второго дополнительного элемента И-НЕ соединен с выходом первого элемента И-НЕ, а вход инвертора. подключен к шине тактовых импульсов.

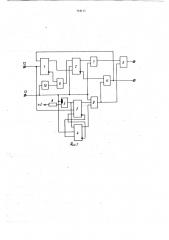

На фиг. 1 приведена структурная схема устройства тактовой синхронизации; на фиг. 2— эпюры напряжений, иллюстрирующие формирование выходных импульсов. . Устройство тактовой синхронизации содержит запоминающий триггер 1, управляющий триггер 2, дополнительные триггеры 3 и 4, логический формирователь 5 импульсов, элементы И-НЕ

6 — 9, инвертор 10, элемент И 11, шину 12 управляющих импульсов и шину 13 тактовых импульсов, тактовый вход запоминающего триггера подсоединен к шине управляющих импульсов, а синхровход управляющего триггера подсоединен к шине тактовых импульсов.

Устройство тактовой синхронизации работает следующим образом.

В исходном положении все триггеры устройства находятся в нулевом состоянии. На шине

12 уйравйякй1тих импульсов присутствует низкий потенциал. Элементы И-НЕ 7 и 8 закрыты (на их выходах поддерживается высокий потенциал), а элемент И-НЕ открыт (на его выходе поддерживается низкий потенциал). На выходе логического элемента И 11 присутствует высокий потенциал. Присутствие тактовых импульсов на шине 13 (фиг. 2, а) изменяет лишь состояние триггера 4, При появлении управляющего сигнала (поло- 4 жительный импульс — фиг. 2, б) перепадом от низкого потенциала к высокому триггер 1 переходит в единичное состояние (фиг. 2, в). .Триггер 3 не изменяет своего состояния, так как на синхровход триггера 4 раньше поступил 45 тактовый импульс и триггер 4 перешел в единичное состояние (фиг. 2, r). Потенциал; соответствующий логическому "0", с инверсного выхода триггера 4 поступает на информационный вход триггера 3, и приход управляющего

50 импульса на информационный вход последнего подтверждает его нулевое состояние. Появление тактового импульса вызывает переключение инвертора 10. С установкой триггера 1 в единичное Состояние на инверсном выходе последнего станавливается низкий потенциал, что прйвбдит к появлению на выходе элемента

И-НЕ 6 высокого потенциала (фиг. 2, д).

Триггер 2 не удерживается принудительно в

4 нулевом состоянии низким потенциалом. Высо кий потенциал с прямого выхода трипера подается на информационный вход триггера 2.

Г прихЬдом следующего ближайшего тактового импульса »a синхровход триггера 2 последний переходит в единичное состояние (фиг.

2, е). На прямом выходе триггера 2 появляется высокий потенциал, открывающий элемент

И-HE 7 по первому входу. На выходе последнего появляется отрицательный импульс (фиг.

2, ж), так как на втором входе элемента

И-НЕ 7 присутствует положительный тактовый импульс. Низкий потенциал с выхода элемента И вЂ” НЕ 7 поступает на вход элемента

И вЂ” НЕ 9 и на выходе последнего появляется положительный импульс (фиг. 2, з), по длительности и моменту совпадающий с тактовым импульсом. С установкой триггера 2 в единичное состояние низкий потенциал с его инверсного выхода поступает на вход элемента И 1I

/ и на в ых оде последнего фор мируетс я отрицательный импульс, по длительности и моменту совпадающий с тактовым импульсом (фиг. 2, и), который поступает на инверсный выход устройства и на нулевой вход триггера 1, устанавливая его в нулевое состояние. Потенциал на его. нулевом выходе становится высоким. По окончании тактового импульса потенциал на выходе инвертора 10 также становится высоким, чу, в свою очередь, приводит к появлению низкого потенциала на выходе элемента И-НЕ 6, которым триггер 2 устанавливается в нулевое состояние.

Таким образом, устройство тактовой синхронизации возвращается в исходное положение.

В моменты времени, когда управляющий и тактовый импульсы не совпадают во времени по переднему фронту (на фиг. 2-моменты времени t,, t,) устройство тактовой синхронизации работает аналогичным образом.

Рассмотрим работу устройства; при совпадении по переднему фронту управляющих и тактовых импульсов (на фиг. 2 — момент времени t ), В этом случае при одновременном поступлении на синхровходы триггеров 3 и 4 управляющих и тактовых импульсов последние переходят в единичные состояния, так как на их информационных входах до этого момента присутствовал потенциал, соответствующий логической "1" (фиг. 2, г, к). Триггер I управляющим импульсом также переводится в единичное состояние. Теперь на всех входах элемента И-НЕ 8 имеются высокие потенциалы, что вызывает его переключение, т.е. на выходе элемента И-НЕ 8 устанавливается низкий потенциал (фиг. 2, л.). Отрицательный импульс с выхода элемента И-НЕ 8 поступает на входы элемента И 11 и элемента И-IIE 9. На выходе элемента И l l формируется также отрицатель164112

5 ный импульс, который поступает на нулевой вход риггера 1, возвращая его тем самым в нулевое состояние, а с поступлением отрицательного импульса на вход элемента И-НЕ 9 на выходе последнего формируется положительный импульс, синхронный с импульсом тактовой частоты, длительностью, равной длительности импульса тактовой частоты. По заднему фронту этого же тактового импульса на выходе формирователя формируется короткий отрицательный импульс (фиг. 2, м), которым триггеры 3 и 4 устанавливаются в нулевое состояние. Таким образом, устройство тактовой син- . хронизации возвращается в исходное положение.

Соединение прямого выхода запоминающего триггера с информационным входом управляющего триггера, синхровход которого подключен к шине тактовых импульсов, и соединение инверсного выхода управляющего триггера с одним из входов элемента И, выход которото со20 единен с нулевым входом запоминающего триггера, позволило повысить быстродейстиве устройства. Так, в прототипе импульс на выходе появляется через время Ьт + Т после поступления управляющего импульса, где Т вЂ” период следования тактовых импульсов; — время от момента поступления управляюгцего импульса до момента поступления ближайшего тактового импульса (см. фиг. 4, а). Таким образом, в известном устройстве тактовой синхронизации задержка составляет 1

=11 + Т.

В предлагаемом устройстве быстродействие ьЬ+ т 35 повысилось в раза. В этом случае ьС т т+т . с=

5tn ; = 2, т.е.. быстродействие повысилось в 2 раза.

Введение двух дополнительных триггеров, логического элемента И и двух логических эле- 411 ментов И-НЕ позволило повысить точность синхронизации, так как при совпадении во времени передних фронтов управляющих и тактовых импульсов на выходе устройства сразу же формируется выходной импульс, синхронный с им- 45 пульсом тактовой частоты.

Формула изобретения

Устройство тактовой синхронизации, содер- жашее последовательно соединенные запомина6 ющий и управляюший триггеры и первый эле. мент И-НЕ, последовательно соединенные инвер тор и второй элемент И-НЕ, второй вход которого подключен к инверсному выходу запоминающего триггера, а выход второго элемента

И-НЕ соединен с нулевым входом управляющего триггера, а также логический формирователь импульсов, тактовый вход которого соединен с вторым входом первого элемента И-НЕ и с шиной тактовых импульсов, о т л и ч аю ш е е с я тем, что, с целью повышения быстродеиствия и точности синхронизации, в него введены два дополнительных триггера, два дополнительных элемента И-НЕ и элемент И, первый вход которого соединен с инверсным выходом управляюшего триггера, второй вход элемента И соединен с выходом первого дополнительного элемента И-НЕ и с первым входом второго дополнительного элемента И-НЕ, первый вход первого дополнительного элемента H-НЕ подключен к тактовому входу логического формирователя, а второй и третий входы первого дополнительного элемента И-НЕ соединены с прямыми выходами первого и второго дополнительных триггеров, при этом нулевые входы дополнительных триггеров соединены с выходом логического формирователя импульсов, инверсные выходы первого и второго дополнительных триггеров соединены с информационными входами второго и первого дополнительных триггеров соответственно, синхровходы первого и .второго дополнительных триггеров подключены к шине управляющих импульсов и к шине тактовых импульсов соответственно, выход элемента И соединен с нулевым входом запоминающего триггера, второй вход второго дополнительного элемента И-HE соединен с выходом первого элемента И-НЕ, а вход инвертора подключен к шине тактовых импульсов, тактовый вход запоминающего триггера подсоединен к шине управляющих импульсов, а синхровход управляющего триггера подсоединен к шине тактовых импульсов.

Источники информации, принятые во внимание при эксперзизе

1, Авторское свидетельство ГССР N" 478429, кл. Н 03, К 5/13, 1975

2. Авторское свидетельство СССР N" 453791, кл. Н, 03 К 5/153, 1974 (прототип).

764112

Составитель Л. Воронина

Техред Н. Барадулина . Корректор В, Бутяга

Редактор T. Орловская

Заказ б301/49

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5