Аналого-цифровой интегрирующий преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

< ц 764 1 29

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 21Я878 (21) 2656289/18-21 (s»e. к. с присоединением заявки №

Н 03 К 13/20

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 1509.80. Бюллетень ¹ 34

Дата опубликования описания 1509.80 (53) УДК 681.325 (088.8) (72) Авторы изобретения

В.И. Мартынюк и A.B. Холодюков (71) Заявитель (5 4 ) АНАЛОГО-ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к измерительной и вычислительной технике, а именно к преобразователям аналоговой величины в цифровую, и может быть использовано при разработке и изго-, 5 товлении цифровых измерительных приборов и устройств связи датчиков аналоговых сигналов с ЭВМ.

Известны интегрирующие аналогоцифровые преобразователи с предвари- )0 тельным преобразованием аналогового сигнала в (пропорциональную) частоту следования импульсов с последующим измерением частоты, служащие для преобразования среднего эа время измере")5 ния значения аналогового сигнала в цифровую форму (1) .

Известен аналого-цифровой интегрирующий преобразователь, содержащий преобразователь аналоговой вели- 20 чины в частоту следования импульсов, выходы которого подключены к установочным входам триггера знака входного сигнала и элемента ИЛИ, выходом соединенного со счетным входом ре- 25 версивного счетчика, триггер знака интеграла и генератор тактовых импульсов (2) .

С помощью указанных преобразователей нельзя произвести дискрети- 1

2 эацию интеграла непрерывного входного аналогового сигнала большой длительности на интегралы эа более короткие отрезки времени. Это объясняется тем, что цикл измерения состоит соответственно из времени измерения и времени индикации. При этом за время ин-. дикации интегрирование входного сигнала не производится и, следователь- ° но, информация о сигнале теряется, что недопустимо при обработке информации с датчиков, где необходимо получить значение интеграла измеряемой величины в больших интервалах времени.

Целью изобретения является исключение потерь йнформации при получении интеграла аналоговых сигналов большой длительности.

Для достижения поставленной цели . в аналого-цифровой интегрирующий преобразователь, содержащий преобразователь аналоговой величины в частоту следования импульсов, выходы которого подключены к установочным входам триггера знака входного сигнала и элемента ИЛИ, выходом соединенного со счетным входом реверсивного счетчика, триггер знака интеграла и генератор тактовых чмпульсов, 764129

ЗО щим образом.

35 нен с выходом третьего элемента И, вто введены дополнительные элементы ИЛИ, элементы И, блок элементов И, вспомогательный триггер, триггер управления счетчиком, регистр памяти, формирователи импульсов. Причем выход основного элемента ИЛИ соединен со счетным входом вспомогательного триггера, информационный вход которого подключен к шине логического 0, а установочный - к выходу первого дополнительного элемента ИЛИ и устайовочному входу триггера управления счетчиком, счетный вход последнего соединен с выходом первого элемента И, неинвертирующий выход — с входом сложения реверсивного счетчика и первыьп входами второго и третьего элементов И, инвертирующий выход— с входом вычитания реверсивного счетчика и одним из входов блока элементов И, другие входы которого цодключены к выходам реверсивного счетчика и информационным входам регистра па мяти, дополнительный информационный вход регистра памяти соединен с выходом триггера знака интеграла, а вход записи — с первым выходом первого формирователя импульсов, вход последнего подключен к выходу генератора тактовых импульсов, а второй выход — к установочному входу реверсивного счетчика и первому входу первого дополнительного элемента ИЛИ, " второй вход которого соединен с выходом блока элементов И и первым входом второго дополнительного элемента ИЛИ, вторым входом подключенного к выходу второго элемента И, а ,выходом — к первому установочному вхдду триггера знака интеграла, вто- рой установочный вход которого соедирые входы второгб и третьего элементов И соединены соответственно с ныходами положительной и отрицательной .полярности преобразователя аналоговой величины в частоту следования импульсосв вход второго формирователя импульсов подключен к выходу триггера знака входного сигнала, выход — к первому входу первоГо элемента И, второй вход которого соединен с выходом вспомогательного триггера.

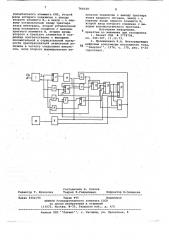

На чертеже показана схема предла аемого аналого-цифрового преобразон". геля i с

Аналого-цифровой преобразователь содержит преобразователь 1 аналоговой величины в частоту следования импульсов, выходы которого подключены к входам триггера 2 знака входйо;. госигнала и элемента ИЛИ 3 элемен ты ИЛИ 4 и 5, первый вход первого из которых соединен с одним из выходов формирователя 6. импульсов, элементы

И 7, 8, 9, вспомогательный триггер 10 счетным входом подсоединеннЫЙ к выходу элемента ИЛИ 3, информационным входом — к шине логического нуля, уста.1 новочным входом — к выходу элемента

ИЛИ 4, а инвертирующим выходом — к одному из входов элемента И 7. Кроме того, преобразователь содержит триггер знака интеграла ll установочны чи входами соединенный с выходами элемента ИЛИ 5 и элемента И 9, триг» гер 12 управления реверсивным счетчиком 13, счетным входом подключенный к выходу элемента И 7, а устано10 ночным — к выходу элемента ИЛИ 4, причем реверсивный счетчик счетнйм входом соединен с выходом элемента

ИЛИ 3, а управляющими входами — с выходами триггера 12, блок 14 элементов И, входами соединенный с выходами реверсивного счетчика и триг-. гера 12, а выходом — с вторым входом элемента ИЛИ 4 и первым входом элемента ИЛИ 5, второй вход которого подключен к выходу элемента И 8.

Преобразователь включает также регистр памяти 15, информационными входами соединенный с выходами реверсивного счетчика 13 и триггера знака интеграла 11, генератор 16 тактовых

25 импульсов, выход которого подключен к входу формирователя 6 импульсов, одним выходом соединенного с установочным входом реверсйвного счетчика, а другим — с входом записи регистра памяти 15, формирователь 17 импульсов, вход кбторого подключен к выходу, триггера 2, а выход — к другому входу элемЕнта И 7.

Преобразователь работает следую-

Входной аналоговый сигнал посту пает на вход преобразователя 1 и преобразуется последнии в частоту следования импульсов, пропорциональную величина аналогового сигнала. завйсимосстйс от полярносги входного сигйала импульсы вырабатываются на соответствующем выходе преобразователя напряжения н частоту. Импульсы

45 с выхода преобразователя напряжения в частоту через элемент ИЛИ 3 поступают на вход реверсивного счетчика

13 и вспомогательного триггера 10.

Цикл преобразования начинается с ус50 тановки реверсивного счетчика, триггера 12 управления счетчиком и scnoмогательного триггера импульсом сброса, вырабатынаемым формирователем 6 импульсов . При этом реверсивный счетчик устанавливается в ноль, триггер управления счетчиком — н положение, разрешающее сложение в реверсивном счетчике, а вспомогательный триггер— в состояйие логического 0 на иннертирующем выходе. По окончании им60 пульса сброса начинается сложение импульсов в реверсивном счетчике.

Одновременно импульсы с преобра. зователя 1 через элементы И 8 и 9 устанавливают триггер знака интег- рала 11 в соответствие с полярностью

764129

/ входного сигнала, Если за время преобразования происходит смена знака входного сигнала, состояние триггера знака сигнала меняется на противопо ложное. Формирователь 17 импульсов на каждую смену состояния триггера знака сигнала вырабатывает импульс, который поступает на счетный вход триггера 12 управления счетчиком и пЕРебрасывает пОслеДний. При первой смене знака сигнала триггер управления счетчиком переключается в состояние, переводящее реверсивный счетчик 13 на вычитание, и импульсы с преобразователя 1, поступающие на реверсивный счетчик, начинают уменьшать содержимое последнего. На время, 15 когда реверсивный счетчик находится в положении вычитания импульсов, сиг налом с триггера управления счетчи- ., ком, поступающим на входы элементов

И 8 и 9, запрещается прохождение импульсов с преобразователя 1 на триггер знака интеграла 11 и последний сохраняет знак до следующего включе= ния режима сложения реверсивного счетчика.

Формула изобретения

Аналого-цифровой интегрирующий

20 преобразователь, содержащий преобразователь аиалоговой величины в частоту следования импульсов, выходы которого подключены к установочным входам триггера знака входного )5 сигнала, и элемент ИЛИ, выход которого соединен со счетнцм входом реверсивного счетчика, трйггер знака интеграла и генератор тактовых импульсов, о т л и ч а ю @ и и с я тем, Зо что,с целью исключения потерь информации при получении интеграла аналоговых сигналов большой длительности, в него введены дополнительные элементы ИЛИ, элементй И, блок элементов И, вспомогательный триггер, триггер управления счетчиком, регистр памяти, формирователи импульсов, причем выход основного элемента ИЛИ соединен со счетным входом вспомогательного триггера, информационный вход которого

4О подключен к шине логического: 0 -, а установочный — к выходу первого дополнительного элемента ИЛИ и уста новочному входу триггера управления счетчиком, счетный вход последнего

4g соединен с выходом первого элемента

И, неинвертирующий выход — с входом сложения реверсивного счетчика H первыми входами второго и третьего элементов И, инвертирующий выход— с входом вычитания реверсивного счетчика и одним из входов блока элемен тов И, другие входы которого подключены к выходам реверсивного счетчика .и информационным входам регистра памяти, дополнительный информационный вход которого соединен с выходом триггера знака интеграла, а вход записи— с первым выходом первого формирователя импульсов, вход последнего подключен к выходу генератора тактовых им60 пульсов, а второй выход — к установочному входу реверсивного счетчика и первому входу первого дополнительного элемента ИЛИ, второй вход которого соединен с выходом блока элементов И и первым входом второго до-.

Одновременно сигнал с триггера

12 управления счетчиком поступает на блок 14 элементов И и разрешает анализ состояния реверсивного счетчика

13. Еспи в режиме вычитания содержимое реверсивного счетчика становит- ся равным нулю, на выходе блока элементов И появляется сигнал, который через элемент HJIH 4 устанавливает триггер управления счетчиком в режим сложения в реверсивном счетчике ° Одновременно этим же сигналом вспомогательный триггер 10 устанавливается в состояние логического 0, на инвертирующем выходе.

Вспомогательный триггер служит для запрещения прохождения импульса с формирователя 17 импульсов на триггер 12 управления счетчиком после установки его в режим сложения до поступления первого импульса с преобразователя 1 в реверсивный счетчик 13. После прохождения импульса-"" с преобразователя 1 в реверсивный счетчик во, вспомогательном триггере

10 записывается логический 0, соответственно разрешается прохождение импульсов с формирователя 17 импульсов на триггер 12 управления счетчиком. Таким образом, с помощью вспомогательного триггера исключается переключение реверсивного счетчика в режим вычитания в ситуации, когда вслед за импульсами с формиро вателя 17 импульсов и блока элементов И, устанавливающимн триггер управления счетчиком в режим сложения, может появиться сигнал смены знака сигнала с триггера 2 знака входного сигнала, а импульсы в реверсивный счетчик 13 еще не поступали и его содержание раэно нулю.

Цикл преобразования заканчивается записью содержимбго реверсивного счетчика и триггера знака интеграла в регистре памяти 15 с помощью импульса переноса, вырабатываемого формирователем б импульсов. .Время преобразования определяется периодом следования импульсов, вырабатываемых генератором 1б тактовых импульсов.

На каждый импульс с генератора тактовых импульсов формирователь б импульсов вырабатывает импульс переноса и импульс сброса.

764129

Составитель Н. Козлов

Техред Е. Гаврьтлешко

Корректор В.Синицкая

Редактор Т. Юрчикова

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6302/50

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 полнительного элемента ИЛИ, второй вход которого подключен к выходу второго .элемента И,- а выход —, к первому установочному входу триггера знака интеграла, второй установочный вход последнего соединен с выходом третьего элемента И, вторые входы второго и третьего элементов И соединены соответственно с выходами положительной и отрицательной полярности преобразователя аналоговой величины в частоту следования импульсов, вход второго формирователя импульсов подключен к выходу триггера знака входного сигнала, выход — к первому входу первого элемента И, второй вход которого соединен с выходом вспомогательного триггера.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3778794, кл. 340-347, 11 12.73, 2. Прянишников И.A. Интегрируюшие цифровые вольтметры постоянного тока, Энергия, 1976, с. 170, рис. 4-24 (прототип).