Многоканальный коммутатор с переменным циклом опроса

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ с присоединением заявки ¹ (23) Приоритет

Н 03 К 17/04

Государственный комитет

СССР по делам изобретений и открытий, Опубликовано 15 0980, Бюллетень № 34

Дата опубликования описания 1509.80 (5Q) УД)(621. 382. 3 (088. 8) (72) Авторы изобретения

В.П.Левицкий и О.О.Каганов

Львовский ордена Ленина политехнический институт (71) Заявитель (54) МНОГОКАНАЛЬН()Й KOPJWTATOP С ПЕРЕФПННЫМ

ЦИКЛОМ ОПРОСА

2 второго элементов И, при этом еди- ничный и нулевой выходы управляющего триггера подключены к первым входам соответственно первого и второго элементов И, выход первого элемента И соединен с синхронным информационным входом основного триггера, выход второго элемента И вЂ” с одним из входов элемента ИЛИ, второй вход которого соединен с единичным выходом основного триггера, а выход - со . вторыми входами первого и второго элементов И следующего разряда, причем выход элемента ИЛИ последнего разряда подключен ко вторым входам первого и второго элементов И первого разряда через общий элемент ИЛИ (2).

Недостаток этого устройства— низкая надежность работы.

С целью повышения надежности работы в многоканальный коммутатор с .переменным циклом опроса, содержащий п-разрядный регистр, каждый разряд которого состоит из основного и управляющего триггеров, элемента ИЛИ, первого и второго элементов И, при этом единичный и нулевой выходы управляющего триггера подключены к riepвым входам соответственно первого и

Многоканальный коммутатор с переменным циклом опроса относится к измерительной и вычислительной технике и может использоваться, в частности, в устройствах с опросом про- з извольного числа каналов (объектов)., преимущественно в тех случаях, когда необходим последовательный опрос с переменным в процессе работы колиЧеством каналов.

Известен многоканальный коммутатор с переменным циклом опроса каналов, формирующий на выходах в заданной последовательности сигналы, содержащий триггеры, дешифраторы и логические элементы (1) .

Недостатком этого устройства является существенное усложнение схемы в зависимости от количества каналов коммутатора за счет увеличе- 20 ния ни ла входов дешифраторов и особенно числа установочных входов триггеров, т.е. низкая надежность работы.

Известен также многоканальный 2з коммутатор с переменным циклом опроса, содержащий и-разрядный регистр, каждый разряд которого состоит из основного и управляющего триггеров, элемента ИЛИ, первого и

30 (61) Дополнительное к авт. свид-ву (22) Заявлено 030778 (21) 2636660/18-21 (5 ) М. Кл.

764131 рядов поступает уровень 0 . До окончания длительности начального сигнала все триггеры 3 и триггер 10 удерживается в состоянии 0, ком25 мутатор находится s исходном состоянии. По окончании сигнала со всех триггеров 3 и триггера 10 снимается сигнал установки, и по фронту перво.го же тактового-кмпульса триггер 10

ЗО и триггер Э первого разряда устанавливаются в состояние 1, а в триггеры Э.всех остальных разрядов заносится 0, что соответствует состоянию опроса первого канала. Уровень логического 0 с нулевого

35 выхода триггера 10 разрешает теперь прохождение через элемент ИЛИ 9 выходного сигнала элемента ИЛИ 8 пос.леднего разряда, т.е. 0 . Этот уровень через элемент ИЛИ 9 и эле-

4О мент ИЛИ 5 поступает на вход 7 триггера 3 первого разряда. Уровень второго, элементов И, выход первого элемента И подсоединен к синхронному информационному. входу основного триггера, выход второго элемента И к одному из входов элемента ИЛИ, второй вход которого подсоединен к единичному выходу основного триггера, а выход — ко вторым входам первого и второго элементов И следующего разряда, причем выход элемента ИЛИ йоследнего разряда подключен ко вторым входам первого и второго элементов И первого разряда через общий элемент ИЛИ, введен триггер начальной установки, нулевой выход которого соединен со вторым входом общего элемента HAH, синхронный информаци- 15 онный вход — с шиной логической 1, асинхронные входы установки основных триггеров всех разрядов.и триггера начальной установки соединены с шиной сигнала установки. 20

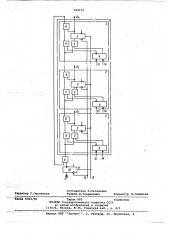

На чертеже представлена структурная схема многоканального коммута-. тора с переменным циклом опроса..

Многоканальный коммутатор с переменным циклом опроса содержит ив

-разрядный регистр 1, каждый разряд

2 которого состоит из основного триггера 3, управляющего триггера 4, элементов Й 5, б, первые выход кото-рых соединены соответственно с еди=

-ничным и нулевым выходами триггера 4, выход элемента И 5 соединен с синх" роннйм информационным входом 7 триггера 3, а выход элемента И б — с входом элемента ИЛИ 8, второй вход которого подключен к единичному выходу триггера 3. Выход элемента 8 соединен со вторыми входами эле ментов И 5 и б следующего разряда, причем выход элемента 8 последнего

n-ro разряда соединен со вторыми входами элементов И 5 и б первого разряда через элемент ИЛИ 9, второй вход котброго подключен к нулевому выходу триггера 10 начальной установки. Триггер 10 однотипен с триггера- 45 ми 3 каждого разряда, на его синхронный информационный вход постоянно передается логическая 1, а асинхронный вход 11 устан6вки в 0 соединен с аналогичными вХодами триг- яп геров 3 всех разрядов и шиной 12 сигнала установки. Ко входам 13 и 14

:.Управляющих триггеров 4 подключены выходы схемы управления этими триггеРами, не представленной ва :iepieit<5 ;

Поскольку в данном устройстве в качестве основных триггеров-и"тригге- ра начальной установки использ лются триггеры потенциально-импульсного типа, то.осуществляется однотактная система синхронизации тактовыми им- 60 пульсами, поступающими по шине 15.

Выходами разрядов коммутатора явля"ютСя единичные выходы триггеров 3.

Устройство работает следующим образом.

Пусть нуждаются s опросе все и каналов коммутатора, т.е. все триг,геры 4 в состоянии 1

После включения устройства и прихода сигнала установки (от схемы управления, от кнопки или любого другого устройства) все основные триггеры 3 разрядов устанавливаются в 0, что соответствует запрету опроса всех разрядов коммутатора. Триггер 10 начальной установки также устанавливаетсяя в 0 . Уровен ь логической i с нулевого выхода триггера 10 через элемент ИЛИ 9 и элемент И 5 первого разряда, на второй вход которого с триггера 4 поступает разрешающий уровень 1, подается на вход 7 триггера Э первого разряда.

Элементы И б всех разрядов заперты уровнем логического 0 с нулевых выходов триггеров 4, поэтому на входы 7 триггеров 3 всех остальных раз 1 с выхода триггера Э первого разряда через элемент ИЛИ 8 первого разряда и элемент И 5 второго разряда йоступает на вхЬд 7 триггера 3 второго разряда. На входах 7 всех остальных триггеров 3 сохраняется уровень 0 ; По приходу второго тактового импульса в 1 устанавливается только триггер 3 второго разряда, что соответствует состоянию опроса второго канала. Осуществляется подготовка к установке в 1 триггера третьего разряда и т.д.

Пусть запрещен опрос одного или нескольких каналов, например второго и третьего. Триггеры 4 этих раэрядов устанавливаются в состояние 0 °

По прихбду сигнала, как и в предыдушем случае, триггеры 3 и триггер

10 устанавливаются в исходное состояние, подготавливая установление по первому тактовому импульсу триггера 3 первого разряда в 1 . Выходные уровни триггеров 4 второго и третьего разрядов запрещают прохож 7б4131 дение сигналов с выхода элемента

ИЛИ 8 первого разряда на входы 7 триггеров 3 этих разрядов, поддерживая на них постоянный уровень логического 0, и разрешают прохождение сигналов через элементы И 6 и

ИЛИ 8 запрещенных разрядов и элемент

:И 5 четвертого разряда на вход 7 триггера 3 четвертого разряда. После прихода второго тактового импульса логическая 1 переносится с выхода триггера 3 первого разряда в триггер 3 четвертого разряда, во все остальные триггеры 3 заносится .логический 0, т.е. коммутатор из состояния опроса первого канала переходит сразу в состояние опроса четвертого канала, пропуская состояния опроса второго и третьего каналов.

Формула изобретения

Многоканальный коьмутатор с переменным циклом опроса, содержащий и-разрядный регистр, каждый разряд которого состоит из основного и управляющего триггеров, элемента ИЛИ, первого и второго элементов И, при этом единичный и нулевой выходы управляющего триггера подключены к

:первым входам соответственно первого и второго элементов И, выход первого элемента И соединен с синхронным информационным входом основного триггера, выход второго элемента И— с одним из входов элемента ИЛИ, второй вход которого соединен с единичным выходом основного триггера, а выход — со вторыми входами первого и второго элементов И следующего разряда, причем выход элемента ИЛИ последнего разряда подключен ко вторым входам первого и второго элементов И первого разряда через общий элемент ИЛИ, отличающийся тем,что,с целью повышения надежности работы коммутатора, в него введен триггер начальной установки, нулевой выход которого соединен со вторым входом общего . элемента ИЛИ, а синхронный информационный вход — с шиной логической

Щ 1, асинхронные входы установки основных триггеров всех разрядов и триггера начальной установки соедийены с шиной сигнала установки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 512578, МКИ Н 03 К 17/02, 30.03.77.

2. Авторское свидетельство СССР

Р 375789, МКИ Н 03 К 17/00, 23.03.73

ЗО

764131

Составитель Л.Скобелева

Техред Е.Гаврылешко Корректор В.Синицкая

РЕдактор Г.Орловская

Иакаэ 6302/50

Тираж 995 Подпи си ое

ВЧЛИПИ Государственного комитета СССР лэ делам изобретений и открытий

113035, ИоскВа, E-35, Раушская наб., д. 4/5

Ю ФВ 4В Ю Ю Ю Ю ВЬ

Филиал ППП Патент, г. ужгород, ул. Проектная, 4