Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. сеид-ву (22) Заявлено 180978 (21) 2665587/18-24 (5>)>

G 05 В 23/02 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР ко делам изобретений и открытий (53) УДК 691.326 (088.8) Опубликовано 23.0980.Бюллетень ¹ 35

Дата опубликования описания 230980 (72) Автор изобретения

Б. Я. Вайнштейн (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ

Изобретение касается изменений и контроля и может быть использовано для визуального контроля параметров логических блоков.

Известны устройства для контроля логических блоков, содержащие контрольный щит, выпрямитель, диодный мост, индикаторы, усилитель, селекторы и синхронизаторы (1) . и 12) .

Недостатком этих устройств является малая информативность и узкая область применения.

Наиболее близким по технической сущности к предлагаемому является устройство 13), принятое за прото- 15 тип и содержащее первый и второй компараторы, входы которых соединены соответственно с первым и вторым входами устройства, первый и второй триггеры, выход первого триггера под-20 ключен к первым входам первого ключа и блока сравнения, выход второго триггера — к первому входу второго ключа и второму входу блока сравнения, выходы первого и второго ключей подсоединены через соответствующие регистры сдвига к первому и второму входам коммутатора, подключенным соответственно ко вторым входам перво,го и второго ключей, третий вход ком-30 мутатора подключен к выходу третьего триггера, первый вход которого соединен с .первым выходом распределителя импульсов, второй вход — с первым входом четвертого триггера и вторым выходом распределителя импульсов, подключенного первым входом к выходу первого делителя частоты, вторым входом — к первому входу первого делителя частоты и к выходу блока сравнения, третьим входом — к третьему входу устройства, второй вход первого делителя частоты соединен с первыми входами первого и второго триггеров, вторыми входами регистров сдвига и выходом формирователя импульсов, подключенного первым входом через третий ключ к выходу, второго делителя частоты, вход которого соединен с выходом генератора импульсов, выход четвертого триггера подключен ко второму входу третьего ключа и третьим входам. первого и второго ключей, второй вход соединен с четвертым входом устройства и .с третьим входом блока сравнения, четвертый вход которого подключен к пятому входу устройства, второй вход формирователя импульсов и второй вход второго делителя частоты под765784 ключены соответственно к шестому и седьмому входам устройства.

Недостатком этого устройства являются ограниченные функциональные возможности.

Целью изобретения является расширение функциональных возможностей

5 устройства.

Это достигается тем, что в него введены счетчик, сумматор, генератор ступенчатого напряжения, а так- Я же первый и второй логические блоки, первые входы которых подсоединены к выходам первого и второго компараторов соответственно, вторые входы — к восьмому входу устройства, а выходы — ко вторым входам первого и второго триггеров соответственно, вход счетчика соединен со вторым выходом распределителя импульсов,а вы-, ход — с четвертым входом коммутатора и через генератор ступенчатого напряжения — с первым входом сумматора, подключенного вторым входом к выходу коммутатора.

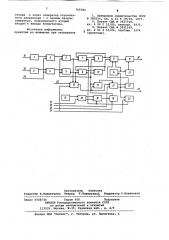

На чертеже приведена структурная схема устройства, на которой обозначе- 25 но первый и второй компараторы " и 2, первый и второй логические блоки 3 и

4, первый и второй" триггеры 5 и б, первый и второй ключи 7 и 8, первый и второй регистры сдвига 9 и 10, ком- ® мутатор 11, сумматор 12, генератор ступенчатого напряжения 13, счетчик

14, блок сравнения 15, генератор им« пульсов 16, первый делитель частоты

17, третий ключ 18, формирователь импульсов 19, второй делитель частоты

20, распределитель импульсов 21, третий и четвертый триггеры 22 и 23, входы 24-29, выход 30, входы 31, 32 и выход 33 устройства.

Устройство работает следующим образом.

Устройство находится постоянно в одном из двух режимов, в режиме записи, либо в режиме считывания информации. В обоих режимах с выхода гене- 45 ратора 16 на вход делителя 20 поступают импульсы опорной частоты. Делитель 20 имеет два выхода, на первом из которых формируются импульсы постоянной частоты, необходимые для Щ считывания информации, а на второмимпульсы с частотой, определяемой коэффициентом деления, установленным сигналами со входа 27 устройства, необходимые для записи информации. 55

Работа устройства в режиме записи.

На вход 24 подается сигнал запуска, устанавливающий в исходное состояние триггер 23, а через блок 15— делитель 20 и распределитель 21.

Информация со входов 31 и 32 поступает на входы входных компараторов 1 и 2 квантующих сигналы относительно трех уровней напряжения, установленных для выбранной серии логических элементов входного напряжения,; 65 переключения, максимального напряжения логического "0" и минимального напряжения логической "1".

В зависимости от значения сигнала, поступающего со входа 28 на входы блоков 3 и 4,. возможны два. режима квантования.

В первом режиме сигнал, квантован- ный относительно входного напряжения переключения, непосредственно поступает на вход "3 " триггера 5 или б.

Во втором режиме сигнал на входах

"3 " — триггеров 5 и б определяется по формуле: ц - Se Sz> Sq где S 1, если входной сигнал превышает максимальный уровень логического "0", S1 1, если входной сигнал превышает минимальный уровень логической "1" S2 сигнал на выходе триггера.

В обоих режимах квантования сигнал на входе "К" триггеров 5 и б получается инвертированием сигнала, поступающего на вход "3 ". Второй режим квантования необходим.для различения трехуровневых сигналов или оборванных проводов беэ увеличения емкости регистров сдвига.

Запись информации в триггеры 5 или б осуществляется тактовым импульсом, поступающим с выхода формирователя 19 °

В зависимости от управляющего сигнала, поступающего на вход формирователя 19 со входа 26, тактовые импульсы могут иметь следующий вид: длигельность синхроимпульса значительно меньше его периода.

При этом триггер 5 или 6 принимает состояние, определяемое значением S в момент прихода импульса, что соответствует синхронной записи информации. Разность периода следования и длительности синхроимпульсов значительно меньше периода

"акважность а 1/. При этом триггер 5 или 6 сохраняет свое состояние, если период синхроимпульса значение 5 не менялось и изменяет на противоположное, если S менялось на время, достаточное для срабатывания триггера 5 или б. Это дает возможность фиксации импульсов, длительность которых значительно меньше периода квантования.

С выхода триггеров 5 и б информация поступает на вход регистров 9 и

10 íà n-m разрядов и записывается в них, но не считывается. Переход из режима записи в режим считывания осуществляется блоком 15. . В зависимости от сигнала на входе

24 возможен переход в режим считывания по окончании сигнала запуска на вход 24, либо в момент совпадения входных сигналов с кодом, поступающим на вход 25 устррйства, 765784

В первом слугае импульс со входа

24 проходит беэ изменений на выход блока 15 °

Во втором случае передний Фронт сигнала со входа 24 вызывает формирование логического "0" на выходе блока 15.

Переключение в состояние логической "1" происходит в момент, когда с выходом триггеров 5 и 6 на входы блока 15 поступит в параллельном моде информация, совпадающая с кодом, йриходящим с входа 25. В обоих случаях переход выходного сигнала блока

15 из состояния логического "0" в

"1" вызовет запуск делителя 20 íà и и распределителя 21 íà m разрядов.

Через число тактов, равное произведению и на разность е и задержки, определяемой сигналом со входа 29 на втором выходе распределителя 21 формируется импульс, переключающий триггеры 22 и 23 в состояние логической "1". При этом сигнал,.поступающий с выхода триггера 23 переключает ключи 7, 8 и 18 в состояние соответствующее режиму считывания.

Работа устройства в режиме считывания.

Регистры 9 и 10 через ключи 7 и

8 замкнуты в кольцо и информация циркулирует в них не обновляясь.

Коммутатор 11 подключает поочередно регистры сдвига 9, 10 и триггер

22 на вход сумматора 12, на другой вход которого поступает сигнал с выхода генератора 13. коммутатором 11 и генератором 13 управляет счетчик 14 по модулю 3 (в общем случае по модулю К+1, где

К вЂ” число каналов). Переключение счетчика 14, коммутатора 11 и формирование новой ступеньки генератором 13 осуществляется одновременно сигналом с первого выхода распределителя 21 один раэ за.несколько тактов работы регистров 9 и 10. Триггер 22 устанавливается в "0" сигналом с выхода первого разряда распределителя 21 и в "1" сигналом с его другого выхода. На выходе сумматора 12 формируется ступенчатый сигнал, каждый уровень которого передает информацию, записанную в одном из регистров 9, 10, либо двухуровневый сигнал, формируемый триггером 22.

Для наблюдения информации, записанной в регистрах 9, 10,необходимо подключить выходы 30 и 33 на внешний осциллограф.

Использование признаков, перечисленных в отличительной части Формулы позволяет различить сигналы с запрещенными уровнями; наблюдать .импульсы с длительностью менее периода квантования и случайные сигналы; выводить информацию, записанную в регистрах сдвига анализатора, на экран осциллографа, то есть значи

1ельно расширить Функциональные воз можности устройства по сравнению с известными решениями. ч3ормула изобретения

Устройство для контроля логических блоков, содержащее первый и второй компараторы, входы которых соединены соответственно с первым и вто10

26

S5

65 рым входами устройства; первый и второй триггеры, выход первого триггера подключен к первым входам первого ключа и блока сравнения, выход второго триггера — к первому входу второго ключа и второму входу блока сравнения, выходы первого и второго ключей подсоединены через соответствующие регистры сдвига к первому и второму входам коммутатора, подключенным соответственно ко вторым входам первого и второго ключей, третий вход коммутатора подклюЧен к выходу третьего триггера, первый вход которого соединен с первым выходом распределителя импульсов, второй вход — с первым входом четвертого триггера и вторым выходом распре» делителя импульсов, подключенного первым входом к выходу первого делителя частоты, вторым входом †. к первому входу первого делителя частоты и к выходу блока сравнения, третьим входом — к третьему входу устройства, второй вход первого делителя частоты соединен с первыми входами первого и второго триггеров, вторыми входами регистров сдвига и выходом формирователя импульсов, подключенного первым входом через третий ключ к выходу второго делителя частоты, вход которого соединен с выходом генератора: импульсов, .выход четвертого триггера подключен ко второму входу третьего теля импульсов и второй вход второго делителя частоты подключены соответ ственно к шестому и седьмому входам . устройства, о т л и ч а ю щ е е с я . тем, что, с целью расширения функциональных возможностей устройства, в него введены счетчик, сумматор, генератор ступенчатого напряжения, а также первый и второй логические блоки, первые входы которых подсоединены к. выходам первого и второго компараторов соответственно, вторые входы — .к восьмому входу устройства, а выходы — ко вторым входам первого и второго триггеров соответственно, вход счетчика соединен со вторым выходом распределителя импульсов, а выход — с четвертым входом коммуключа и третьим входом первого и второго ключей, второй вход соединен с четвертым входом устройства и с третьим входом блока сравнения, четвертый вход которого подключен к пятому входу устройства, второй вход формирова-

765784

Составитель Алексеев

Редактор И.Бахметьева Техред H.Âàðàäóëèíà Корректор О.Ковинская

Заказ 6508/44 Тираж 956 Подписное

ВНИИПИ Росударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 татора и через генератор ступенчатого. напряжения †с первым входом сумматора, подключенного вторым входом к выходу коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 580514, кл. С 01 R 19/14, 1977.

2. Патент США 9 3927310, кл. G 06 F, 11/00, опублик. 1975.

3. Патент CQIA 9 3831149, кл. G 01 R 15/00, опублик. 1974 (прототип).