Устройство для вычисления функции вида

Иллюстрации

Показать всеРеферат

I кяте1, . нс.-тя ин.",.;куя

) ъ, з т т д

СоюЗ Советских

Социалистических

Республик

ОП ИСАНИ E

ИЗОБРЕТЕНИЯ

<1ц 765 803

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 25. 08. 78 (2! ) 2676293/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 230980, Бюллетень 1 19

Дата опубликования описания 260980 (51)М. Кл.3

G 06 F 7/38

Государственный комитет

СССР по делам изобретений и открытий (5З) АК 681,325 (088.8) (72) Автор изобретения

A-Ю.Борисова

Рязанский радиотехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ВИДА () (g х,) Изобретение относится к цифровой вычислительной технике и может быть использовано в приборах и устройствах статистической обработки информации., в частности, при вычислении дисперсии в темпе накопления данных, модуля суммы многомерных векторов и т.д.

Известны устройства, выполняющие операцию возведения в квадрат суммй чисел,;содержащие реверсивные счетчики, триггеры, счетчики-делители, счетчик выборки, схемы совпадения, генератор тактовых импульсов $1) .

Йаиболее близким по технической сущности к предлагаемому является 15 устройство для вычисления функции ь вйда g gn)(g X ), содержащее

1 1 регистр числа; выход которогд"(тодключен ко входу блока коммутаторов, блок управления, сумматор p) .

Кроме того, устройство содержит. эле менты ИЛИ.

Недостатком в этих устройствах является то, что при вычислении квадрата суммы чисел (k X )2 выс полняется предварительное йакоплейие

Pl полной суммы чисел т х . Число

L=1 рабочих тактов при возведении в квадрат составляет

М и, = Х, + Хг+, ° . + Х „-,«т Х = Й Х

2 " и ° .„ где Х вЂ” среднее значение последовательности входных чисел хт,х ...x

Принципиально указанные устройства позволяют вычислять квадрат суммы чисел в темпе поступления данных, т е. фо)эмирбйать функцию вида ф(п)а

*(.1 х; ), где a=1,2,3,...N. В этсзм случае требуемое число рабочих тактов для получения конечного результата при n ""--й возрастает и находится следующим образом

Xi 4 "г(q) ХЬ(" 2)+ "+Хм=

N+1 N2

=,7. Х (N-i-q)a)(3Ц a.)(2 2 !

Быстродействие устройств в таком случае определяется требуемым количеством рабочих тактов, равным (N /2)x и существенно (по квадратичному закону) зависит от числа исходных цанных, т.е. пропорционально N2/2 .

765803 5 !

О

40

Действительно: (Х «„)+

Хп

Целью изобретения является повышение быстродействия устройства.

Это достигается тем, что в устройство для вычисления функции вида

y!п)=(, x; ), содержащее регистр числа, выход которого подключен ко входу блока коммутаторов, блок управления, сумматор, введены регистры суммы, результата промежуточный регистр, а блок управления содержит генератор импульсов, делитель частоты, счетчик, дешифратор, триггер, дискриминатор нуля, счетчик-регистр, элемент задержки, пять элементов И, причем выходы всех регистров через блок коммутаторов подключены ко входам сумматора, выход которого соединен с ин,формационными входами регистров результата, сумьы и промежуточного регистра, выход генератора импульсов подключен к первому входу первого элемента И и входу делителя частоты, выход которого соединен со входами элемента задержки и счетчика, выход которого подключен к управляющему входу блока коммутаторов и входу дешифратора, первый, второй, третий и четвертый выходы которого соединены с первыми входами соответственно второго, третьего, четвертого и пятого элементов И, вторые входы второго, третьего и пятого из которых подключены к выходу элемента задержки, а второй вход четвертого элемента И соединен с выходом первого элемента

И и входом вычитания счетчика-регистра, информационный вход которого подключен к выходу регистра числа, вход записи которого соединен с выходом второго элемента И и входом счетчикарегистра, выход которого подключен ко входу дискриминатора нуля, выход которого соединен с нулевым входом триггера, выход которого соединен со вторым входом первого элемента И, а единичный вход триггера подключен к третьему выходу дешифратора, выходы третьего, четвертого и пятого элементов И соединены соответственно со вХодами записи промежуточного регистра, регистров суммы и результата, информационный вход регистра числа является входом устройства.

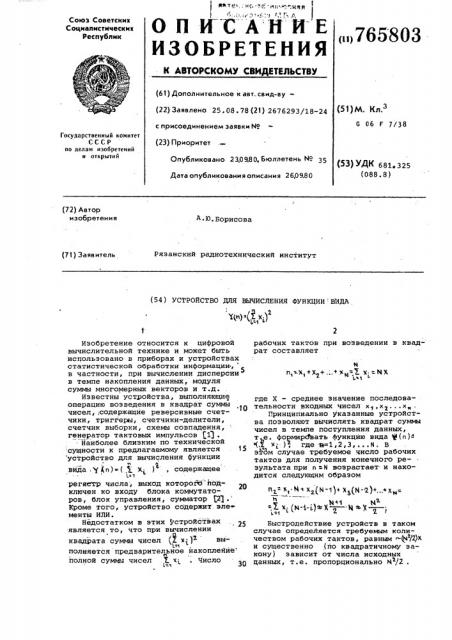

Сущность изобретения заключается в в том, что вычисление квадрата суммы значений х„ производится в интервале времени между приходом двух соседних,значения х„, и х„ и выполняе ся в соответствии с рекурентной формулой (Х «Ä) =ф «;)+х„(2 «„ «„) (1) На чертеже представлена структур. ная схема предлагаемого устройства.

Схема содержит регистр 1 числа, блок

2 управления, генератор 3 импульсов, делитель частоты 4, счетчик 5, дешифратор 6, триггер 7, дискриминатор нуля 8, счетчик-регистр 9, элемент задержки 10, элементы И 11 — 15, блок

16 коммутаторов, сумматор 17, промежуточчый регистр 18, регистр суммы

19, регистры результата 20.

Устройство работает следующим образом.

В исходном состоянии перед поступлением значения x„ в регистре суммы 19 записана сумма .ф, х,, в регистре 20 записан квадрат суммы (L«)

По сигналу с блока управления 2 очередное значение х заносится в регистр числа 1, после чего блок управления выдает команду на коммутатор 16 для подключения на входы сумматора 17 выходов регистра числа 1 и регистра суммы 19. Содержимое регистра суммы подается со сдвигом на один разряд влево, благодаря чему осуществляется умножение суммы ,Ъ. Х„ на два без дополнительного ь-1 .тактирования. Сумматор выполнен на потенциальных полусумматорах, поэтому непосредственно после подключения к нему укаэанных значений чиаел на

его выходах устанавливается код чис-. ла 2 д х; к„ который по сигналу с блока управления 2 записывается в промежуточный регистр 18.

После этого к сумматору 17 блоком управления 2 через коммутатор 16 подключаются выходы промежуточного регистра 18 и регистра квадрата суммы

20. Блок управления 2 выдает х сигналов на вход записи регистра квадрата суммы (результата) 20 для занесения в последний результат суммирования, после чего в регистре 20 образуется число, равное квадрату суммы

=ф «„.) +«„(2 х; х„)=(«;) Число тактов суммирования, равное х» блок управления определяет благодаря наличию связи его входа с выходом регистра числа x„ . Значение результата запоминается в регистре ,20, после чего блок управления дает команду на вычисление суммы

«\ и-1

,Хх х=7.xx„. „

Р1 " . .=1 путем подключения к сумматору 17. выходов, регистра суммы 19 и регистра

765803 числа 1. Содержимое сумматора заносится в регистр суммы 19 по команде с блока управления. На этом обработка значения х заканчивается.

Блок управления 2 формирует команды, определяющие порядок работы устройства. Работа блока управления происходит циклически. Один цикл состоит из 4-х тактов. В исходном состоянии счетчик 5 находится в положении "00".

Сигналом с соответствующего выхода дешифратора б открыт элемент И 12, на второй вход которого поступает сигнал с делителя частоты 4,- которым в регистр числа 1 и в счетчик-регистр

9 записывается очередное значение х

С приходом первого тактового импульса 15 с делителя частоты 4 счетчик 5 ставится в состояние "01", которое дешифрируется дешифратором 6. Код "01" со счетчика подводится к коммутатору 16 для подключения к .сумматору 17 выхо- gO дов регистра числа 1 и регистра суммы

19, а сигнал с дешифратора подается на один из входов элемента И 13, на второй вход которого поступает задержанный элементом задержки 10 тактовый импульс для занесения результатов суммирования в промежуточный регистр

18. Время задержки определяется общим временем срабатывания коммутатора и сумматора. Второй тактовый импульс ставит счетчик 5 в состояние "10", ко-З торым подключает к сумматору через коммутатор 16 промежуточный регистр

18 и регистр результата 20, а сигнал с дешифратора открывает элемент

И 14, через который на вход записи регистра результата 20 поступают импульсы тактового генератора. Коэффициент деления делителя частоты 4 определяется максимальным значением (числом разрядов) входных данных х.. 40

Число импульсов, проходящих через элемент И 14 формируется следующим образом. В момент переключения счетчика 5 в состояние "10" триггер 7 переводится в едийичное состояние, ко- 45 торым открывается элемент И 11. Импульсы тактового генератора 3 начинают поступать на элемент И 14 и одновременно на вход счетчика 9, который работает в вычитающем режиме.

С приходом x„ импульсов счетчик 9 обнуляется, срабатывает диСкриминатор нуля 8, возвращая триггер 7 в исходное состояние. Элемент И 11 закрывается. Таким образом, в течение этого такта на вход записи регистра результата 20 проходит х импульсов.

С приходом третьего тактового импульса счетчик переводится в состояние "11", кодом которого подключаются к сумматору 17 регистр числа 1 и ре- 60 гистр суммы 19, а через элемент И 15 проходит импульс записи в регистр суммы 19 результатов суммирования.

Четвертый тактовый импульс ставит счетчик в исходное состояние "00" 65 при котором принимается новое значение входной информации x+yf .Обработка входного сигнала х происходит аналогичным образом.

Быстродействие устройства определяется числом тактов суммирования, равного сумме значений исходных чиИ сел, т.е.. ч„=ИМ, и пропорционально б э! непосредственно :.ислу исходных данных N.

Таким образом, предлагаемое устройство позволяет вычислять квадрат суммы чисел в темпе поступления информации и обеспечивает выигрыш в быстродействии по сравнению с известными устройствами в М/2 раз, что при достаточно большом числе входных сигналов является весьма существенным.

Формула изобретения

Устройство для вычисления функции вида Y (n ) = (,r х „), содержащее регистр числа, выход которого подключен ко входу блока коммутаторов, блок управления, сумматор, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены регистрь суммы, результата, промежуточный регистр, а блок управления содержит генератор импульсов, делитель частоты, счетчик, дешифратор,.триггер, дискриминатор нуля, счетчик-регистр, элеМент задержки, пять элементов И, причем выходы всех регистров через блок коммутаторов подключены ко входам сумматора, выход которого соединен с информационными входами регистров результата, суммы и промежуточного регистра, выход генератора импульсов подключен к первому входу первого элемента И и входу делителя частоты, выход которого соединен со входами элемента задержки и счетчика, выход которого подключен к управляющему входу блока коммутаторов и входу де-шифратора, первый, второй, третий и четвертый выходы которого соединены с первыми входами соответственно второго, третьего, четвертого и пятЬго элементов И, вторые входы. второго, третьего и пятого из которых подключены к выходу элемента задержки, а второй вход четвертого элемента И соединен с выходом первого элемента И и входом вычитания счетчика-регистра, информационный вход которого подключен к выходу регистра числа, вход записи которого соединен с выходом второго элемента И и входом счетчика-регистра, выхбд которого подключен ко входу дискриминатора нуля, выход которого соединен с нулевым входом триггера, выход которого соединен со вторым входом первого элемента И, а единичный вход триггера подключен к третьему выходу дешифратора, выходы тре765803

Составитель H.Шелобанова

РедакторИ.Бахметьева Техред Ж.Кастелевич Корректор С.Шекмар

Заказ 6510/45 Тираж 7 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП"Патент, г.ужгород,ул.Проектная, тьего, четвертого и пятого элемен тов И соединены соответственно со входами записи промежуточного регист. ра, регистров суммы и результата, информационный вход регистра числа является входом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

Р 419899, кл. С 06 F 15/36, 1974.

2.Авторское свидетельство СССР

° 5 В 343273, кл. G 06 G 7/52, 1970.