Устройство для записи цифровой информации

Иллюстрации

Показать всеРеферат

< >765870

Союз Советскмх

Соцмвлмстмческма

Республмк

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф г (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.09.78 (21) 266048!/18-10 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.а

G 11 В 5/09

Гееударстееннмй камитет

Опубликовано 23.09.80. Бюллетень,% 35

Дата опубликования описания 28.09.80 (53) 534.852 (088.8) до делам лзебретеннй н ютармтнй

Л. А. Белова, С. А. Белоусов, В. И. Галкин, Д. С. Дубинин, Г. А. Комоцкнй, В. В. Цыганков и Г. Ф. Шамнн (72) Авторы изобретения

f ( (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАПИСИ

ЦИФРОВОЙ ИНФОРМАЦИИ

Изобретение относится к приборостроению, а именно к устройствам для записи цифровой информации на движущийся магнитный носитель.

Известно многоканальное устройство записи-воспроизведения цифровой информации, записанной методом узкополосной фазовой манипуляции (УФМ) (1). Его преобразующая перед записью часть состоит из последовательно соединенных сумматора по модулю 2, Э-К триггера, усилителя записи и головки записи. В результате суммиро- 1о вания входного сигнала и синхроимпульсов (СИ) получается кодовая последовательность, которая, поступая на вход Э-К триггера, на его выходе преобразуется в трехчастотный код Миллера.

Недостатками этого устройства являются низкая эксплуатационная надежность и невысокая достоверность.

Наиболее близким по технической сущности к предлагаемому является устройство для магнитной записи и воспроизведения, содержащее информационные каналы с фазовым манипулятором в каждом из них (2J

Недостатком этого устройства является неустойчивость к временным смещениям меж2 ду каналами при повышении, плотности записи.

Цель изобретения — повышение достоверности информации и увеличение устойчивости к временным смещениям между каналами.

Цель достигается тем, что в устройство введены дополнительный информационный канал, опорный канал, блок проверки на четность, блок преобразования синхроимпульсов, счетчики адресов занесения и считывания, блок формирования маркерного слова, в каждый информационный канал введены блок памяти, логический элемент И и сумматор, опорный канал выполнен в виде делителя частоты и логического элемента И, при этом первый вход логического элемента И опорного канала подсоединен к входам делителя частоты, блока преобразования синхроимпульсов и счетчика адресов занесения, выход которого подключен к первым входам блоков памяти каждого информационного канала, а вторые входы блоков памяти через счетчик адресов считывания соединены с выходом блока преобразования синхроимпульсов, с входом блока формирования маркерного слова и с первыми входами фазовых манипуляторов каждого информационного канала, 3 сбросовые BxoBHI блока преобразования синхроимпульсов и блока формирования маркерного слова соединены с Выходом делителя частоты опорного канала, при этом первый выход блока формирования маркерного слова соединен с входами сумматоров каждого информационного канала, а второй выход — с первымн входами логических элементов И информационных каналов и вторым входом логического элемента И опорного канала, третьи входы блоков памяти информационных каналов подключены к соответствующим входам блока проверки на четность, вы îä,которого соединен с третьим входом блока памяти дополнительного информационнОго канала, 3 ВыхОды блОкОВ памЯти через сумматор каждого информационного канала подключены ко вторым входам фа" îâûõ манипуляторов, выходы которых соединены со вторыми Входами логических элементов И информационных каналов.

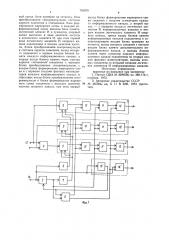

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2— временные диаграммы его работы.

Устройство содержит информационные каналы 1, дополпительееыйе информационный канал 2, опорный канал:3, блок 4 проверки на четность, блок 5 преобразования синхроимпульсов, счетчики адресов занесения, и считывания 7 и блок 8 формирования маркерного слова.

Каждый информационный канал состоит из последовательно включенных блока памяти 9, сумматора 10, фазового манипулятора 11, логического элемента И 12. Причем вход его соединен с входными шинами

l3, а также с соответствующими входами блока 4 проверки на четкость, выход которого подключен к входу дополнительного инфор HBHHOHHOI O KBHBJIB 2. аналогH IHOI O HHформационному каналу 1.

Входная шина 14 импульсов синхронизации соединена с входами делителя частоты

15 и логическим элементом И 16 опорного канала З„входами счетчика 6 адресов занесеееия и через блок 5 преобразования синхроимпульсов — входом счетчика 7 адресов считывания, со вторыми входами фазовых манипуляторов 1! информационных каналов l и 2, а также с первым входом блока

8 формирования маркерного слова. Выходы счетчиков адресов занесения 6 и считывания

7 подключены соответственно к вторым и третьим входам блоков памяти 9. Второй вход блока 5 соединен со Вторым входом блока 8 формирования маркерного слова, а также с выходом делитель частоты 15.

Вторые входы сумматоров 10 и логических элементов И 12 и 16 подключены к соответствующим выходам блока 8.

Входные импульсы синхронизации (см. фиг. 2,б) поступают на счетчик адресов занесения, который формирует коды адресов для занесения информации (см. фиг. 2, а) в блоки памяти. Эти же импульсы синхронизации поступают в блок преобразования синхронизации, где происходит умножение входнои частоты в †- раз (где и — целое

И.+ число) и «вырезка» определенного количества импульсов (см. фиг, 2, в) . Например, при и =-. i5 коэффициент умножения частоты блока преобразования синхронизации равен —. Поэтому на каждые 150 входных СИ по16 лучается 150 импульсов синхрочизации умноженной частоты плюс 10 импульсов умноженной частоты, которые «вырезаются». Полученные импульсы (см. фиг. 2, в) через счетчик адресОВ считыВания, где формируются коды адресов считывания, поступают

В блоки памяти информационных каналов для считывания информацHH из памяти.

Тае(им обоазом, В блоках памяти происходит сжатие информации во времени. Образовавшийся временной промежуток заполняется десятиразрядным маркерным словом (см. фиг. 2, I), сформированным блоком формирования маркерного слова из импульсов синхронизации умноженной частоты, на схеме сумматора. На выходе схемы сумматора получается последовательность, изображенная H" фиг. 2, д. Например, десятиразрядное маркерное слово может иметь структуру

1О!0000101. Тогда фазовый манипулятор преобразует ее во Временные интервалы 2Т-I, 5Т-IT-IT-l, 5Т-2Т, которые могут встречаться в принципе и в измерительной информации. Поэтому, чтобы превратить эту комбинацию в запрещенную с интервалами 2Т-I, 5Т-2Т-1, 5Т-2Т, блок формирования маркерного слова вырабатывает импульс запрета, который «Выбивает» на логическом элементе И импульс между двумя интервалами IT и делает из них 2Т. Этот же импульс запрета поступает на логический элемент И опорного канала и «выбивает» один из импульсов синхронизации. Это делается для «окраски» последовательности импульсов синхронизации с целью восстановления его при воспроизведении для обнуления счетчиков адресов считывания.

Делитель частоты служит для фазировки блоков преобразования синхронизации и пре образования маркерного слова. В данном случае коэффициент деления равен 150, поэтому фазировка происходит через 150 импульсов синхронизации.

Формула изобретения

Устройство для записи цифровой информации, содержащее информационные каналы с фазовым манипулятором в каждом из них, отличаюи!ееся тем, что, с целью повышения достоверности информации и увеличения устойчивости к временным смещениям между каналами, в устройство введены дополнительный информационный канал, опор765870 ный канал, блок проверки на четность, блок преобразования синхроимпульсов, счетчики адресов занесения и считывания, блок формирования маркерного слова, в каждый информационный канал введены блок памяти, логический элемент И и сумматор, опорный канал выполнен в виде делителя частоты и логического элемента И, при этом первый вход логического элемента И опорного канала подсоединен к входам делителя частоты, блока преобразования синхроимпульсов и счетчика адресоь занесения, выход которого подключен к первым входам блоков памяти каждого информационного канала, а вторые входы блоков памяти через счетчик адресов считывания" соединены с выходом блока преобразования синхроимпульсов, с входом блока формирования маркерного слова и с первыми входами фазовых манипуляторов каждого информационного канала, л сбросовые входы блока преобразовании сикхроимпульсов и блока формирования маркерного слова соединены с выходом делителя >в частоты опорного канала, при этом первый выход блока формирования маркерного слова соединен с входами сумматоров каждого информационного канала, а второй выход — с первыми входами логических элементов И информационных каналов и вторым входом логического элемента И опорного канала, третьи входы блоков памяти информационных каналов подключены к соответствующим входам блока проверки на четность, выход которого соединен с третьим входом блока памяти дополнительного информационного канала, а выходы блоков памяти через сумматор каждого информационного канала подключены ко вторым входам фазовых манипуляторов, выходы которых соединены со вторыми входами логических элементов И информационных каналов.

Источники информации, принятые во внимание при экспертизе !. Патент США № 3699556, кл. 340- 74. 1, опублик. !972.

2. Авторское свидетельство СССР

¹ 455364». кл,- G !! Б 5/02, !973 (прототип) .

765870 фиг.2

Составитель И. Миронова

Редактор Т. Иванова Техред К. Шуфрич Корректор О. Билак

Заказ 65 f 8/48 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I (3035, Москва, Ж вЂ” 35, Раушская иаб., д. 4/5 .

Филиал ППП «Патеит», г. Ужгород, ул. Проектная, 4