Формирователь записи-считывания для запоминающих устройств

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (765873

ИЗОБРЕТЕНИЯ

Союз Советск ми

Соцмалмстмческ ма

Реслублмк

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 13.11.78 (21) 2683259/18-24 с присоединением заявки №вЂ” (23) Приоритет— (5I) М. Кл.э

G 11 С 7/00

Гос дерстеениый комитет

Опубликовано 23.09.80. Бюллетень № 35

Дата опубликования описания 28.09.80 (53) УДК 681.327, .6 (088.8) до делам иэаоретеник к открытие (72) Авторы изобретения

В. И. Невядомский и .С. Н. Исаева (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ

ДЛЯ ЗАПОМИНАЮЩИХ УСТРОГ.СТВ

Изобрегение относится к области электронной и вычислительной техники и, в частности, предназначено для использования в интегральных полупостоянных запоминающих устройствах.

Известны формирователи записи-считывания, используемые в ППЗУ в качестве буферных схем между выходами дешифратора и шинами строк накопителя.

Известен формирователь записи-считывания, содержащий транзистор считывания, затвор которого соединен со словарной шиной, исток подключен к шине считывания, а сток соединен с выходом формирователя (1). Для формирования сигналов в режиме записи и избирательного стирания в него введен первый транзистор, Мтвор которого соединен со словарной шиной и второй транзистор, затвор которого соединен с истоком первого транзистора, а исток соединен с выходом формирователя записи-считывания.

Недостаток устройства состоит в ограниченных функциональных возможностях.

Наиболее близким техническим решени- ем к предлагаемому изобретению является формирователь записи-считывания, содержащий транзистор считывания, сток которого через МДП-резистор соединен с шиной высокого потенциала, затвор соединен со словарной шиной, управляющий транзистор, сток которого соединен с выходом устройства, исток подключен к шине смещеНия, прно и инверсную шины управления 12).

Для обеспечения режимов записи и избирательного стирания в него введены два ключевых транзистора, первый иэ которых свято зывает вход с выходом формирователя, а второй подключен к выходу (стоку) транзистора считыв4 . я.

Этот фо рователь обеспечивает три режима ра пы: избирательное стирание, запись и считывание. Недостатком устройства является отсутствие режи ма обще ro сти рания. Кроме этого, устройство имеет низкое быстродействие в режиме считывания эа с., т малой проводимости первого ключевотранзистора.

Цель изобретения — повысить функциональные возможности формирователя.

Это достигается тем, что в формирователь записи-считывания, содержащий транзистор считывания, исток которого подклю765873 чен к шине считывания, затвор — к словарной шине, сток — к выходу устройства и через первый МДП-резистор — к шине записи, управляющий транзистор, исток которого подключен к шине смещения, сток — к стоку транзистора считывания, шины управления, введены коммутирующий транзистор, исток которого подключен к первой шине управления, затвор — к словарной шине, а сток — к затвору управляющего транзистора, второй МДП-резистор, одним концом подключенный ко второй шине управления, а вторым — к стоку коммутирующего транзистора.

Кроме того, второй МДП-резистор выполнен со встроенным каналом, а коммутирующий транзистор — с индуцированным каналом, причем затвор и сток МДП-резистора соединены со второй шиной управления.

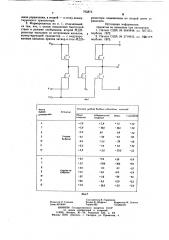

На фиг. 1 представлена электрическая принципиальная схема формирователя; на фиг. 2 — таблица величин уровней входных и выходных сигналов.

Формирователь за1иси-считывания содержит МДП-резистор 1, коммутирующий транзистор 2, управляющий транзистор 3, шину

4 смещения, транзистор 5 считывания, МДПрезистор б, шину 7 записи, шину 8 считывания, словарную шину 9, вторую шину 10 управления, первую шину 11 управления и выход 12 устройства.

Предлагаемый формирователь обеспечивает работу накопителя полупостоянного запоминающего устройства в следующих четырех режимах: общее стирание, избирательное стирание, запись, считывание.

Рассмотрим работу формирователя отдельно для каждого режима.

Режим общего стирания. На шину 10 управления подается напряжение амплитудой — 9 В, на шину 11 управления, шину

7 записи, шину 4 смещения, шину 8 считывания подается напряжение амплитудой

+ 5 В (см. таблицу).

Если на словарную шину 9 из дешифратора поступает напряжение «лог, О» (строка не выбрана), то транзисторы 2 и 5 закрываются и через МДП-резистор 1, выполнен..ый со встроенным каналом, напряжение — 9 В полностью передается на затвор управляющего транзистора 3, в результате чего емкость шины строки накопителя разряжается через этот транзистор.

Если на словарную шину 9 из дешифратора поступает напряжение «лог. 1» (строка выбрана), то транзисторы 2 и 5 открываются, причем проводимость коммутирующего транзистора 2 превышает в б — 8 аз проводимость МДП-резистора 1, и на затворе управляющего транзистора 3 устанавлива ется напряжение «лог. О», запирающее уп равляющий транзистор 3.

В этом случае емкость шины строки накопителя разряжается до напряжения +5 В через открытый транзистор 5 считывания.

Таким образом, независимо от того, какой сигнал поступает из дешифратора на словарную шину 9 каждого формирователя, в режиме общего стирания на выходе 12 формируется напряжение +5 В, поступающее на шины строк накопителя, и при одновременной подаче на изолированную подложку накопителя, напряжения стирания амплитудой — 30 В в ячейках всех строк накопителя происходит общее стирание информации.

Режим избирательного стирания. На шину 10 управления, шину 4 смещения подается напряжение амплитудой + 5 В, на шину 11 управления подается напряжение амплитудой — 9 В, на шину 7 записи подается отрицательное напряжение амплитудой — 30 В, а шина 8 считывания подключена к высокоомному сопротивлению (см. табл.) Hpè работе формирователя на выбранную строку из дешифратора на словарную шину 9 поступает напряжение «лог. 1» в и транзисторы 2 и 5 отпираются.

Несмотря на то, что МДП-резистор 1 со встроенным каналом также оказывается в состоянии проводимости, но проводимость его встроенного канала резко ограничивается за счет перехода из триодного режима работы в режим стабилизации тока при подключении к шннс 10 управления низкого напряжения амплитудой +5 В, отношение проводимостей транзистора 2 и МДПрезистора возрастает.

Вследствие этого через открытый транзистор 2 на затвор управляющего транзистора 3 поступает напряжение, достаточное для его отпирания. Соотношение проводимостей . управляющего транзистора 3 и МДП-резистора 6 выбрано таким, что на шине выбранИ ной строки накопителя устанавливается напряжение + 5 В. Если одновременно на изолированную подложку подать напряжение стирания амплитудой — 30 В, то в ячейках выбранной строки происходит стирание ин41 формации. При работе формирователя на невыбранную строку иа словарную шину 9 из дешифратора поступает напряжение

«лог. О».

В этом случае коммутирующий транзис тор 2 и транзистор 5 считывания закрыты, 44 а через МДП-резистор 1 емкость затвора управляющего транзистора 3 разряжается до напряжения запирания. В результате емкость шины невыбранной строки накопителя заряжается до напряжения 25 — 30 В. При одновременной подаче на изолированную подложку накопителя отрицательного напряжения амплитудой -30 В стирание информации в невыбранных строках не происходит, Режим записи. На шину 10 управления поступает напряжение амплитудой -9 В, на шину 11 управления и шину 4 смещения поступает напряжение амплитудой +5 В, на шину 7 записи поступает высоковольтное отрицательное напряжение амплитудой

765873

4$ ае

Фориула изобретения

-30 В, шина 8 считывания подключена к высокоомному сопротивлению (см. табл.) .

При работе формирователя на выбранную строку на словарную шину 9 из дешифратора йриходит напряжение «лог. 1», коммутирующий транзистор 2 открывается, и так как проводимость МДП-резистора 1 меньше проводи мости коммутирующего тра нзистора 2, напряжение на затворе управляющего транзистора 3 устанавливается меньше напряжения отпирания. Выход формирователя через открытый транзистор считывания 5 подключается к высокоомному сопротивлению и емкость шины выбранной строки накопителя заряжается до напряжения -(25 — 30) В, достаточного для записи информации, если одновременно на изолированную подложку накопителя подано напряжение смещения +5 В.

При работе формирователя на невыбранную строку из дешифратора поступает напряжение «лог. О», транзисторы 2 и 5 запираются.

На затвор управляющего транзистора 3 через открытый МДП-резистор 1 поступает напряжение «лог. 1», достаточное для его отпирания, и на выходе формирователя 12 устанавливается напряжение +5 В, как результат деления высоковольтного напряжения -30 В между МДП-резистором 6 и транзистором 3. Таким образом формирователь обеспечивает запрет записи информации в невыбранную строку накопителя.

Режим считывания. На вторую шину 10 управления поступает напряжение амплитудой -9 В, на шину 1 управления, шину 4 смещения, шину 7 записи поступает напряжение амплитудой +5 В, а на шину считывания приходит напряжение считывания, (см. табл.), которое выбирается из условия:

Ц„ьl-loll i iu " l uñ4ìòÆoð1 1 17вер1ю где(,11 -электрически изменяемые пороговые напряжения запоминающего транзистора накопителя в состоянии «лог О» и «лог. 1» соответственно; аЦ,рО„ — значения температурно-временного дрейфа пороговых нанряжений запоминающего транзистора накопителя;

Ц - минимальное значение эффективного напряжения, обеспечивающее отпирание запоминаю щего транзистора накопителя в режиме считывания.

При работе формирователя на выбранную строку на словарную шину 9 от дешифратора приходит напряжение «лог. 1», коммутирующий транзистор 2 отпирается .и в соответствии с соотношением проводимостей

МДП-резистора 1 и коммутирующего траиэистора 2 на затворе управляющего транзистора 3 устанавливается напряжение «лог, О», запирающее этот транзистор. Через открытый транзистор 5 считывания емкость шины строки накопителя заряжается до напряжения - 2 В, обеспечивающего считывание информации.

При работе формирователя на невыбранную строку на словарную шину 9 иэ дешифратора поступает напряжение «лог. О», транзисторы 2 и 5 запираются. На затвор управляющего транзистора 3 через МДП-резистор l поступает напряжение «лог. 1», достаточное для его отпирания. В результате происходит разряд емкости шины строки накопителя через транзистор 3 до напряжения +5 В.

Таким образом, формирователь обеспечивает запрет считывания информации в невыбранной строке.

Преимущества предлагаемого формирова теля записи-считывания для накопителя полупостоянного ЗУ по сравнению с известными устройствами состоят в реализации как общего, так и избирательного стирания информации.

Прн применении полупостоянных ЗУ с такими формирователями в блоках хранения изменяемых микропрогра мм обеспечивается уменьшение времени перезаписи при полной замене программ (за счет общего стирания), а при частичной смене програ»1м — уменьшение емкости буферной памяти, применяемой для сохранения минимально стираемого объема данных (эа счет избирательного стирания) .

Кроме того, предлагаемый формирователь обеспечивает повышение быстродействия в режиме считывания не менее чем в

1,5 раза за счет применения второго МДПрезистора со встроенныя каналом и уменьшение мощности, потребляемой полупостоянным ЗУ,на ЗΠ— 40О О за счет перехода на низковольтные управляющие сигналы.

1. Формирователь записи-считывания для запоминающих устройств, содержащий транзистор считывания, исток которого подключен к шине считывания, затвор — к словарной шине, сток — к выходу устройства н через первый МДП-резистор — к шине записи, управляющий транзистор, исток которого подключен к шине смещения, сток — к стоку транзистора считывания, шины управления, огличаюи!ийся тем, что, с целью расширения функциональных возможностей формирователя за счет обеспечения режима общего стирания, в него введены коммутирующий транзистор, исток которого подключен к первой шине управления, затвор — к словарной шине, а сток — к затвору управляющего транзистора, второй МДП-резистор, один конец которого подключен ко второй

765873 фиг 1

Фиг.2

Составитель В. Гордоиова

Редактор О. Стеиииа .Техред К. Шуфрич Корректор М. немчик

Заказ 65ISI48 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4 щиие управления, а второй — к стоку коммутирующего транзистора.

2. Формирователь по п. 1, отличающийся тем, что, с целью повышения быстродействия в режиме счиТывания, второй МДПрезистор выполнен со встроенным каналом, коммутирующий транзистор — с индуцированным каналом, причем затвор и сток МДП"

В резистора подключены ко второй шине уп равления.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3649848, кл. 307-251, опублик. 1972.

2. Патент США № 3719932, кл. 340.17 опублик, 1973.