Частотный дискриминатор

Иллюстрации

Показать всеРеферат

- т е т н е- i-. ч е с к

".-t1p o l е <а ОБА

ЛИС

Союз Советскмх

Социалнстнческмх

Респубпкк iii766035

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. синд-ву(22) Заявлено 19.06.78 (21) 2634143/LS 09 с присоединением заявки М— (23 ) П рнорнтетОпубликовано 23.09.80. Бюллетень Рй 35

Дата опубликования описания 26.09.80 (5t)M. Кд.

Н 04 Ь 27/14

Гасударственный камитет па делам изобретений и аткрытнй (53 ) УД К 62 1, 394.

° 62 (088.8) (72) Авторы изобретения

И. И. Сушкевич, Ф. Г. Киндиренко и А. El Ивлев (71) Заявитель (54) ЧАСТОТНЫЙ ДИСКРИМИНАТОР

Изобретение относится к электросвязи и может использоваться в устройс1 вах преобразования сигналов аппаратуры передачи данных и устройствах измерения частоты и временных интервалов.

Известен частотный дискриминатор, содержащий входной усилитель-ограничитель, противофазные выходы которого соединены с входами первого и второго дифференпирующих блоков, и два эпемен

10 та И, выходы которых через интегратор соединены с выходным пороговым блоком, а входы — перекрестно подкл1ттчены к прямым и инверсным выходам триггеров, к первым входам которых подключен вы15 ход генератора тактовой частоты через первый и второй делитепи частоты, управляющий вход каждого из которых соединен с инверсным выходом соответствующего триггера t1j.

Однако известный дискриминатор имеет невысокую помехозащищенность.

ILetts изобретения - повышение помехозащищенности.

Для этого в частотный дискриминатор, содержащий входной усилитель-ограничитель, противофаэные выходы которого соединены с входами первого и второго дифференпирующих блоков, и два, элемента И, выходы которых через интегратор соединены с выходным пороговым блоком, а входы-перекрестно подключены к прямым и инверсным выходам триггеров, к первым входам которых подключен выход генератора тактовой частоты через первый и второй делители частоты, управпяющий вход каждого из которых соединен с инверсным выходом .соответствующего триггера, введены два элемента -HE и два элемента запрета, при этом выход первого дифференпирующего блока через первый элемент запрета соединен с вторым входом первого триггера, а выход второго дифференпирующего блока через второй элемент запрета соединен с вторым входом второго триггера, управляющий вход первого элемента запрета

3 766035 соединен с выходом второго элемента

И-HF, к одному из входов которого подключен дополнительный выход второго делителя частоты, а к другому входу подключен прямой выход второго триггера, управляющий вход второго элемента запрета соединен с выходом первого элемента И-НЕ, к одному из входов которого подключен дополнительный выход первого делителя частоты, а к другому 10 входу - подключен прямой выход первого триггера.

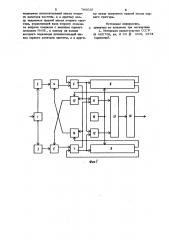

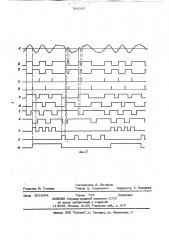

На фиг. 1 предоставлена структурная электрическая схема предлагаемого частотного дискриминатора; на фиг. 215 временные диаграммы, поясняющие его работу.

Частотный дискриминатор содержит усилитель-ограничитель 1, дифферендирующие блоки 2 и 3, элементы запрета

4 и 5, триггеры 6 и 7, делители 8 и

9 частоты, генератор 10 тактовой частоты, элементы И 11 и 12, элементы

И-НЕ 1 3 и 14, интегратор 15 и пороговый блок 16.

Устройство работает следующим образом.

Частотно-модулированный (IN) сит нал (см. фиг. 2, а) поступает на усилитещограничитель 1, усиливается и

30 ограничивается по амплитуде (см. фиг.

2, б, в). llanee импульсами (см. фиг.

2, г, д) с выходов дифферениирующих блоков 2, 3 и элементов запрета 4 и 5 запускаются со сдвигом на попупериод частоты ЧМ-сигнала триггеры 6 и 7, которые обеспечивают разблокировку делителей 8 и 9 частоты. Через время, равное средней длительности полупери» ода частоты IN-сигнала, импульсы ге- 4> нератора 10 тактовой частоты с выходов делителей 8 и 9 частоты воздействуют на триггеры 6, 7 и возвращают их в исходное состояние, обеспечивая получение на выходе этих триГгеров 45 двух прямых и двух инверсных последовательностей импульсов (см. фиг. 2, е, ж). Одновременно в течение времени, определяемого делителями 8 и 9 часто ты, на входы элементов И-НЕ 13 и 14 подаются напряжения, которые с их выходов (см. фиг. 2, и, э) запрещают прохождение через элементы запрета

4 и 5 на триггеры 6 и 7 дополнительных импульсов возникающих HB выхо 55 дах дифференпирующих блоков 2 и 3 в результате дробления ограниченного

ЧМ-сигнала (см. фиг. 2, б, в) из-за воздействия помех в канале связи.

Полученные на выходах триггеров 6 и 7 прямые и инверсные последовательности импульсов сравниваются в элементах И

11 и 12, обеспечивая детектирование

ЧМ -сигнала, соответствующего удвоенному значению верхней (см. фиг. 2, к) и нижней (см. фиг. 2, л) частот. В результате логического детектирования на выходе каждого элемента И ll и 12 формируются пачки импульсов, чередование которых осуществляется по закону модулирующей функдии. Полученные на выходах элементов И 11 и 12 последовательности импульсов усредняются в интеграторе 15 и поступают на пороговый блок 16, обеспечивающий Восстанов» ление переданного двоичного сигнала (см. фиг. 2, м).

Техническая эффективность предлагаемого решения заключается а том, что в результате введения запрета на прохождение дополнительных импульсов, сформировавшихся а результате воздействия помех а канале связи, не происходит ложных" запусков делителей частоты и не производится ложного детектирования сигнала, т. е. происходит повышение помехозащищенности частотного дискриминатора.

Формула изобретения

Частотный дискриминатор, содержащий входной усилитель-ограничитель, противофазные,выходы которого соедин ны с входами первого и второго дифферениирующих блоков, и два элемента И, выходы которых через интегратор соединены с выходным пороговым блоком, а входы перекрестно подключены к прямым— и инверсным выходам триггеров, к первым входам которых подключен выход генератора тактовой частоты через первый и второй делители частоты, управляющий вход каждого из которых соединен с инверсным выходом соответствующего триггера, о т и и ч а ю шийся тем, что, с пелью повышения помехозащищенности, введены даа элемента И-HE и два элемента запрета, при этом выход первого дифферениирующего блока через первый элемент запрета, соединен с вторым входом первого триггера, а выход второго дифферениирующего блока через второй элемент запрета соединен с вторым входом второго триггера, управляющий вход первого элемента запрета соединен с выходом второго элемента

И-НЕ, к одному из входов которого

Источники информании, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

J4 46570В, кл. Н 03 Q 3/02, 1974 (проготип ).

5 766035 6 подключен дополнительный выход второ- му входу подключен прямой выход перго делителя частоты, а к другому вхо- вого триггера. ду подключен прямой выход второго трит гера, управляющий sxolt второго элемента запрета соединен с выходом первого элемента И-НЕ, к одному из входов которого подключен дополнительный выход первого делителя частоты, а к друго766035

Составитель Е. Погиблов

Техред Е. Гаврилешко Корректор Г. Назарова.

Редактор О. Стенина

Заказ 8529154 илиад ППП Патент", г. Ужгород, ул. Проектная, 4

Тираж 729 Поднисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, >К-35, Раушская наб., д. 4/5