Устройство для декодирования сигналов пал-секам

Иллюстрации

Показать всеРеферат

Союз Советски к

Социапистическик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 766040

{6l ) Дополнительное к авт. свил-ву (22) Заявлено 20.06.78 (21) 2623893/18-09 (5! )М. Кл.

Н 04 М 9/50 с присоединением заявки №

Гоаударстееиный комитет (23) Приоритет ио делам изобретений и открытий

Опубликовано 23.09.80. Бюллетень ¹ 35 (53) УДК 621 .397 (088.8) Дата опубликования описания 25.09.80 (72) Автор изобретения

Б. Н. Хохлов (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ

СИГНАЛОВ ПАЛ-СЕКАМ

Изобретение относится к телевидению и может использоваться в цветных телевизионных приемниках и випеоконтрольных устройствах системы ПАЛ-СЕКАМ.

Известно устройство пля декодирования сигналов ПАЛ-СЕКАМ, содержащее блок задержки, на сигнальный вход которого подан сигнал цветности, два демодулятора и два коммутатора, входы управления которых соединены с выходами блока управления, первый вход которого coet0 динен с выходом релаксационного генератора, на вход которого поданы управляющие импульсы, а второй вход блока управления и вход управления блока за« держки соединены с источником управляющего напряжения ПАЛ-СЕКАМ Pj

Однако известное устройство имеет высокий уровень перекрестных искажений при приеме сигнала СЕКАМ.

Цель изобретения — уменьшение перекрестных искажений.

Qns этого в устройство для декодирования сигналов ПАЛ-СЕКАМ, содержащее блок задержки, на сигнальный вход которого подан сигнал цветности, два демодулятора и два коммутатора, входы управления которых соединены с выходами блока управления, первый вход которого соединен с выходом релаксационного генератора, на вход которого поданы управляющие импульсы, а второй вход блока управления и ахоп управления блока задержки соединены с источником управляющего напряжения ПАЛ-СЕКАМ, выходы блока задержки соединены с входами демодуляторов, первые выходы которых соединены с первым и вторым входами первого коммутатора, а второй выход первого демодулятора соединен. с первым входом введенного третьего коммутатора, второй вход которого соединен с первым выходом второго демодулятора, второй выход которого соединен с вторым входом второго коммутатора, первый ахоп которого соединен с выходом третьего коммутатора, вход управления которого соединен с ис7(>(!! )40 4 .I .,! налы Е у и Е, ., ч!. ". !у!:!!и!! <:я по строкам. В показапно. .1 на фиг..! полож.— .! нии коммутаторов 1 и 5 си! нал I поступает на выход устройства со второго

-l

5 выхода демодулятора 2, а сигнал Е, у с первого выхода демодулятора 3. Так как первые и вторые выходы демодуляторов 2 и 3 инверсны, оба выходных цветоразностных сигнала имеют одинаковую под лярность. Во время следующего строчного

Ф интервала положение коммутаторов 4 и 5

1 меняется и сигнал Е к снимается со второго выхода демодулятора 3, а сигнал

Š— с первого выхода демодулятора

1s 2. Уменьшение перекрестных искажений о- в предложенном устройстве достигается благодоря тому, что коммутаторы 4 и 5 подключены к выходам демодуляторов 2 и 3, где цветовая поднесушая отсутствует.

20 Поэтому перекрестные искажения в предложенном устройстве создаются только прохождением цветовой поднесущей через паразитные емкости запертых ветвей коммутаторов 12 и 16, в то время как

25 в известном устройстве к этим связям добавляются перекрестные искажения, вызванные коммутатором СЕКАМ.

3 точником управляющего напряжения

ПАЛ-СЕКАМ, кроме того, блок управления содержит элемент И-НЕ, выход которого соединен с первым выходом блока управления, первый вход которого соединен с собственнь|м вторым выходом и первым входом элемента И-НЕ, второй вход которого соединен с вторым входом блока управления, кроме того; блок задержки содержит линию задержки на время строки, соединенную с входом блока задержки и с входом четвертого коммутатора, а выход линии задержки на время строки через усилитель с парафразными выходами соединен с первыми входами двух сумматоров, вторые вх ды которых соединены с первым выходом четвертого коммутатора, при этом Bblxoll первого сумматора соединен с первым входом пятого коммутатора, второй вход которого соединен с вторым выходом четвертого коммутатора, вход управления которого соединен.с выходом управления блока задержки и с входом управления пятого коммутатора, выход которого соединен с первым выходом блока задержки, а выход второго сумматора соединен с вторым выходом блока задержки.

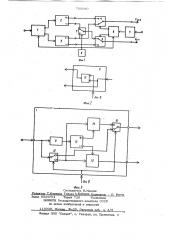

На фиг. l приведена структурная схе- 30 ма предложенного устройства; на фиг. 2структурная электрическая схема блока управления, на фиг. 3 — структурная электрическая схема блока задержки.

Устройство для декодирования сигналов ПАЛ-СЕКАМ содержит блок 1 задержки, два демодулятора 2 и 3, два коммутатора 4 и 5, блок 6 управления, релаксационный генератор 7, источник 8 управляющего напряжения ПАЛ-СЕКАМ, третий коммутатор 9, кроме того, блок 6 управления включает элемент И-НЕ 10, а блок 1 задержки содержит линию задержки 11 на время строки, четвертый ком- 4> мутатор 12, усилитель 13 с парафазными выходами, два сумматора 14 и 15, пятый коммутатор 16.

Устройство работает следующим образом.

На фиг. 1 — 3 коммутаторы 9, 12 и

16 показаны в положении, соответствующем приему сигнала СЕКАМ. В таком режиме прямой сигнал через коммутаторы

12 и 16 поступает на вход демодулятора

2. Задержанный сигнал через усилитель

13 и сумматор 15 поступает на вход демодулятора 3. На выходах демодуляторов

2 и 3 выделяются цветоразностные сигРассмотрим теперь работу предложенного устройства в режиме ПАЛ. Изменением управляющего напряжения от источника 8 коммутаторы 12, 16 и 9 переводятся во второе рабочее положение.

Логический элемент И-НЕ 10 перестает пропускать на второй выход блока 6 управления меандр полустрочной частоты.

Коммутатор 4 останавливается в поло-. жении, при котором первый выход демоI дулятора 2 соединен с выходом Е, у устройства. При этом в сумматоре 14 прямой сигнал складывается с задержанным в фазе, авсумматоре,,15 — в про-. тивофазе. На вход демодулятора 2 поступает цветовая поднесущая, содержащая только состовляющую Ь-Y с постоянной фазой, а на вход демодулятора 3 — цветовая поднесущая с составляющей 3;У фаза которой меняется каждую строку на 18СР. . После демодуляции сигнала Е он с первого выхода демодулятора 2 через неработающий коммутатор 4 поступает на выход устройства. ДемодулироО ванный сигнал Е у, полярность кото-. рого меняется каждую строку, поступает с двух инверсных выходов демодулятора

3 на входы работающего коммутатора 5, В результате на втором выходе

7600 4

5

l устройства выделяется сигйал Е с постоянной полярностью.

Таким образом, предложенное устройство обеспечивает демодуляцию сигналов ПАЛ и CEKAN и уровень перек« рестных искажений на 7,5 дБ меньше, чем в известном устройстве. Вмес те с тем, предложенное устройство проще известного, поскольку содержит на два электронных коммутатора меньше.

На базе предложенного устройства может быть выполнена полупроводниковая интегральная схема декодера ПАЛ-CEKAN, имеющая лучшие параметры, чем интегральная схема ТСА650 фирмы Филипс.

Формула изобретении

1. Устройство дпя декодирования сигналов ПАЛ-СЕКАМ, содержащее блок ло задержки, на сигнальный вход которого подан сигнал цветности, два демодулятора и два коммутатора, входы управления которых соединены с выходами блока управления, первый вход которого соединен с выходом релаксационного генератьра, на вход которого поданы управляющие импульсы, а второй вход блока управления и вход управления блока задержки соединены с источником управляющего напря- yg жения ПАЛ-CEKAN, .о т л и ч а ю щ ее с я тем, что, с целью уменьшения перекрестных искажений, выходы блока задержки соединены с входами демодуляторов, первые выходы которых соединены с первым и вторым входами первого коммутатора, а второй выход первого демодулятора соединен с первым входом введенного третьего коммутатора, второй вход которого соединен с первым выходом второго демодулятора, второй выход которого соедине с вторым входом второго коммутатора, первый вход которого соединен с выходом третьего коммутатора, вход управления которого соединен с источником управляющего напряжения ПАЛ-CEKAN.

2. Устройство по и. 1, о т и и ч а ющ е е с я тем, что блок управления содержит элемент -HE, выход которого соединен с первым выходом блока управления, первый вход которого соединен с собственным вторым выходом и первым входом элемента И-НЕ, второй вход которого соединен с вторым входом блока управления.

Э. Устройство по п. 1, о т л и ч а ющ е е с я тем, что блок задержки на время строки, соединенную с входом блока задержки и с входом четвертого коммутатора, а выход линии задержки на время строки через усилитель с парафазными выходами соединен с первы/ ми входами двух сумматоров, вторые входы которых соединены с первым выходом четвертого коммутатора, при этом выход первого сумматора соединен с первым входом пятого коммутатора, второй вход которого соединен с вторым выходом четвертого коммутатора, вход управления которого соединен с входом управления блока задержки и с входом управления пятого коммутатора, выход которого соединен с первым выходом блока задержки, а выход второго сумматора соединен с вторым выходом блока задержки.

Источники информации, принятые во внимание при экспертизе

1. Заявка Великобритании М 1395534, кл. Н 04 F, 1975 (прототип).

Фиг Г

1 фдад. 3

Составитель В.Маврин

Редактор «Т Клюкина Техоед А.Бабинец Кооцектоц» -«О. Билак

Заказ 6529/54 Тираж . 729 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035 Москва Ж-35 Рщшская наб„д 4/5

Филиал ППП Патент", г. Ужгород, ул, Проектная, 4