Мажоритарно-резервированный триггер

Иллюстрации

Показать всеРеферат

евт тнв-тех н наес

®в®! детина ЦА

Союз Советских

Социалистических

Рест)ублик

НИЕ

ИЗОБРЕТЕНИЯ ()766053

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 221278 (21) 2699904/18-21 (51)М. Кл 3

Н 05 К 10/00 с присоединением заявки Но

Государствеииый комитет

СССР ло делам июбретеиий и открытий (23) Приоритет

Опубликовано 230980, Бюллетень мо 35

Дата опубликования описания 230980 (53) УДК 621. 374 (088.8) (72) Авторы изобретения

В. П. Супрун и Ю. Г. Нестеренко (71) Заявитель (54) ИАЕОРИТАРНО-РЕЗЕРВИРОВАННЫИ ТРИГГЕР

Изобретение относится к вычисли- . тельной и импульсной технике и может быть использовано для построения резервированных триггеров повышенной надежности. 5

Известен резервированный триггер, содержащий элементы И, И-НЕ, ИЛИ и три триггера, единичные выходы которых подключены ко входам мажоритарного элемента, кроме того единичный выход 1О триггера каждого канала подключен к одному из входов элементов И-НЕ, и ИЛИ других каналов, другие входы элементов И-НЕ каждого канала подключены к выходам элементов И соответст- 5 вующих каналов и через инверторы — к элементам ИЛИ (1).

Недостатками данного резервированного триггера являются наличие общего мажоритарного элемента для трех кана- 20 лов, .отказ которого приводит к отказу всего устройства, отсутствие мажорити рования в обратной связи элементов памяти (триггеров) и отсутствие элементов, обеспечивающих полную провер- 25 ку резервированного триггера во время ,эксплуатации, что при наличии непроверяемых отказов в единственном на три канала мажоритарном элементе при водит к тому, что надежность устройст

2 ва становится хуже надежности нерезервироваиного триггера.

Известен резервированный триггер, содержащий в каждом канале блок памяти и двухступенчатую схему управления, выполненную на элементах И-НЕ, ИЛИ-НЕ, причем нулевой элемент блока памяти каждого какала выполнен в виде мажоритарного элемента входы которого подключены к выходам единичных элементов блока памяти всех каналов, первая ступень схемы управления выполнена на элементе ИЛИ, выход первого элемента

И второй ступени схемы управления подключен к одному из входов второго элемента И этой же ступени, другой вход которого подключен к одному из входов единичного элемента блока памяти и ко входу первой ступени схемы управления, а выход - к выходу единичного элемента блока памяти, другой вход которого подключен к нулевому выходу триггера (2) °

Недостатком данного резервированного триггера является то, что невозможно осуществить полную проверку функционирования резервированного триггера при его эксплуатации в составе блоков и устройств вычислитель-.

766053 ных приборов, что в конечном счете снижает его надежность.

Цель изобретения - повышение надежности путем обеспечения полной проверки функционирования устройства при его эксплуатации.

Для достижения поставленной цели

s мажоритарно-резервированном триггере содержащем в каждом канале элемент

И-ИЛИ-НЕ и мажоритарный элемент с инверсным выходом, подключенным к выходной шине и к первому входу первого вентиля элемента И-ИЛИ-НЕ, второй вход которого подключен к шине сброса, при этом первый вход второго вентиля элемента И-ИЛИ-НЕ подключен к тактовой шине, другие его входы подкачены соответственно, к шинам условий, а вы-, ход каждого элемента И-ИМЙ-HE-подключен к соответствующему входу каждого мажоритарного элемента - в каждом канале дополнительные входы первого и второго вентилей элемента И-ИЛИ-НЕ подключены к шине имитации единиц, первый вход третьего вентиля элемен- . та ИИЛИ-ИЕ-подключен к шине имитации нулей, а второй вход - к шине разрешения иьйтации.

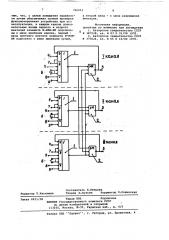

На чертеже представлена блок-схема мажоритарно-резервированного тригге ра, Схема содержит в каждом канале элемент 1 И-ИЛИ-НЕ и мажоритарный элемент 2, выход мажоритарного элемента 2 подключен к выходной шине 3 и к первому входу первого вентиля элемента 1 И-ИЛИ-НЕ, второй вход которого подключен к шине 4 сброса, пер вый вход второго вентиля элемента 1

И-ИЛИ-НЕ подключен к тактовой шине 5, другие входы соответственно — к шинам

6 условий, дополнительные входы первого и второго вентилей элемента 1

И-ИЛИ-HE подключены к шине 7 имитации единиц, первый вход третьего вентиля элемента 1 И-ИЛИ-НЕ подключен к шине

8 имитации нулевой, а.второй входк шине 9 разрешения имитации. Выход элемента 1 И-ИЛИ-НЕ каждого канала подключен к соответствующему входу мажоритарного элемента 2 каждого канала.

Мажоритарно-резервированный триггер работает следующим образом.

В режиме основного функционирования сигналы высокого уровня соответст вующие логической 1, поступают иа шины 7 и 4 и отсутствуют на шинах

8 и 9. Запись информации в мажоритарно-резервированный триггер производится по сигналам высокого уровня . иа шинах 5, перед записью информации на шины 4 и 5 сигналы высокого, уровня не поступают. При этом, так как хотя бы на одном входе каждого вентиля элементов 1 И-ИЛИ-НЕ есть логический 0, на выходе элементо

1 И-ИЛИ-НЕ устанавливается состояние логической 1, а на выходах мажоритарных элементов 2 — состояние логического 0 . Так как выходы мажоритарных элементов 2 подключены к первым входам первых вентилей элементов 1

И-ИЛИ-НЕ, то при поступлении на шины

4 сигналов логической 1 мажориzарно-резервированный триггер остается a сброшенном (нулевом) состоянии. ,Далее, если при поступлении сигнала высокого уровня на шины он отсутству" ет хотя бы на одном из входов, соединенных с шинами б, мажоритарно-резервированный триггер не изменит своего нулевого состояния. Если же в момент поступления логической 1 на шины

5 на всех входах вторых вентилей зле15 ментов 1 И-ИЛИ-НК, соединенных с шинами 6, будут сигналы высокого уровня, то на выходах элементов .1 И-NJN-НЕ устанавливается состояние логического 0, а на выходах мажоритарных

Я элементов 2 - состояние логической 1, при этом на всех входах первых вентилей элементов 1 И-ИЛИ-НЕ появляются сигналы логической 1 . Таким образом, мажоритарно-резервированный триггер устанавливается в единичное состояние. Причем, если в какомЭ ! I либо канале сигнал логической 1 на шине 4 не исчезает, а на шинах 5 и 6 отсутствуют сигналы высоксго уровня нз-эа отказов оборудования, или при наличии соответствующих QTKBBÎÂ по входам элемента 1 И-ИЛИ.-НЕ, триггеры (элементы 2 памяти) в каждом канале устройства запоьынают одну и ту же информацию. При отказе какого-либо элемента 1 И-ИЛИ-НЕ, типа обрыв по выходу, триггер (элемент памяти) этого канала неработоспособен, но на всех выходных шинах 3 информация вырабатывается истинная, При отказе какого40 либо мажоритарного элемента по выхо.Ыу, устройство будет функционировать, так как на двух других выходных шинах

3 будет вырабатываться истинная информация.

45 B режиме автоматической проверки

{например с помощью тестов) устройств, составными частями которых являются мажоритарно-резервированные триггеры, полная работоспособность элементов мажоритарно-резервированного триггера, а также основного оборудования, Вырабатывающего сигналы, поступающие на шины 4 - 6, определяется следующим образом. В течение всего времени про" верки на шины 9 поступает сигнал логической 1 и проверка производится в три этапа. На первом этапе в первом канале на шине 8 и на шине 7 сигнал логического 0, поэтому независимо от состояния на остальных вхо46 дах элемента 1 И-ИЛИ-НЕ на выходе элемента 1 И-ИЛИ-НЕ в первом канале и на соответствующих входах мажоритарных в элементав 2;устанавливается состояние логической 1, во втором канале нашину 8 поступает сигнал логической

766053 1, поэтому независимо от состоя ния на входах первого и второго вентилей элемента 1 И-ИЛИ-НЕ на его выходе и на соответствующих входах ,мажоритарных элементов 2 устанавливается состояние логического 0, третий канал устройства работает в режиме основного функционирования и на выходе элемента 1 И-ИЛИ-НЕ состояние определяется сигналами на шинах 4

6. Таким образом, состояние на выходах всех мажоритарных элементов 2 определяется сигналами на шинах 4 - 6 третьего канала. При этом, если на выходе элемента 1 И-ИЛИ-НЕ в третьем канале задается по тесту состояние логического 0, то анализируя сос- i5 тояния вйходов мажоритарных элементов

2, обнаруживаются отказы типа Обрыв на выходах элементов 1 И-ИЛИНВ во втором и третьем каналах и на вхОдах мажоритарных элементов 2,.под- Щ ключенных к этим выходам, а также в элементах, подключенных к шине 8 в первом и в третьем канале, и отказы типа Короткое замыкание в элементах., подключенных к шинам 4 - 7 в третьеМ канале. Если иа выходе элемента 1 И-ИЛИ-HK в третьем канале задается по тесту состояние логической 1, то, анализируя состояние выходов мажоритарных элементов 2, абмаруживаются отказы типа Короткое замыкание на выходах элементов

1 И-ИЛИ-НЕ в первом и третьем каналах и на входах мажоритарных элементов 2, подключенных к ним, а также в элементах, подключенных к шине 8 во втором канале, и отказы типа O6рыв в элементах, подключенных к шинам 4 - б и 8 в третьем канале и в элементах, подключенных к шине 8 в первом канале. При проверке работы 40 устройства в данком режиме тест про верки задаются таким образом, что на вход каждого вентиля элемента 1 И-ИЛИНЕ поступает код Бегущий ноль, т.е. на какой-либо вход постунает логический 0 сигнал при наличии на остальных входах вентиля сигналов логической 1, . Таким образом, имитируя иа выходе элемента 1 И-ИЛИ-НЕ

s первом канале состояние логической 1 во втором канале — состояние логического 0 и управляя мажоритарными органами 2 состоянием выхода элемента 1 И-ИЛИ-НЕ третьего канала обнаруживаются отказы типа Обрыв и типа Чсороткое замыкание по анализу состояний на соответствующих входах и выходах элементов устройства.

На втором этапе проверки все вышеописанное для первого канала происходит во втором канале, для второго- кана- () ла - в третьем, а для третьего канаРа - в первом. На третьем этапе проверки вышеописанное для проверки на первом этапе для первого канала происходит в третьем канаЛе, для второгс канала - в первом, а для третьего канала — во втором. Таким образом, с каждого канала поочередно на входы мажоритарных элементов 2 имитируются 0, 1 и функция по тесту, что обеспечивает голную проверку всех элементов устройства и элементов устройств; задающих сигналы; которые поступают на шины 4 — 9. Кроме того при определенных типах отказов элементов 1 И-ИЛИ-HE в двух каналах, и при любых типах отказов элементов 1

И-ИЛИ-НЕ в двух каналах, и при любых типах отказов устройств, задающих сигналы на шины 4 — 6 в двух каналах, мажоритарно-резервированный триггер функционирует нормально, так как с помощью сигналов на шинах 7 - 9 он перестраивается на оставшийся исправный канал, при этом функционирование мажоритарно-резервированного триггера происходит аналогично описанному для первого этапа режима проверки.

Как показал анализ и проведенные расчеты данный мажоритарно-резервированный триггер позволяет- во-первых, обеспечить 100Ъ-ную проверку устройства без непосредственного доступа к элементам устройства и, во-вторых, при наличии множества всевозможных отказов в двух каналах произвести перестройку устройства на работу от исправного канала и выдачу ао всем ,выходам истинной информации, при этом его надежность приближается к величине P + ЗР (1 — Р) + ЗРх (1 — P) против надежности известного равной

Р + 3P (1 — Р), где P — надеж юсть одного канала.

Кроме того следует отметить, что шины 8 и 9 дублируют друг друга по наличию сигнала логического 0 .

Дублирование вызвано тем, что согласно статистике отказы типа Обрыв для многих классов элементов составляют 90 - 95Ъ от всех отказов, а Обрыв для данных элементов аналогичен наличию сигнала логической ее1ею

Формула изобретения

Мажоритарно-резервированный триггер, содержащий в каждом канале элемент И-ИЛИ-НЕ и мажоритарный элемент с инверсным выходом, подключенным к выходной шине и к первому входу первого вентиля элемента И-ИЛИ-НЕ второй вход которого пс1дключен к шине сброса, при этом первый вход второго вентиля элемента И-ИЛИ-НЕ подключен к тактовой шине, другие его входы подключены, соответственно, к шинам условий, а выход каждого элемента И-ИЛИ-НЕ подключен к соответствующему входу каждого мажоритарного элемента, отличающийся

766053

Составитель Л.Петрова

Техред И.Кузьма Корректор O,Ковинская

Редактор Т.Киселева

Тираж 885 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 69 31/20

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 тем, что, с целью .повышения надежности путем обеспечения полной проверки функционирования устройства при его эксплуатации, в каждом канале допол- . нительные входы первого и второго вентилей элемента И-ИЛИ-HR подключены к шине имитации единиц, первый вход третьего вентиля элемента И-ИЛИНЕ подключен к шине имитации нулей, а второй вход — к шине разрешения имитации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельствî СССР

У 387528, кл. Н 03 К 21/00 1970, 2. Авторское свидетельство СССР

9 375824, кл. 8 05 К 10/00 1970.