Устройство для автоматического контроля интегральных схем

Иллюстрации

Показать всеРеферат

Воеоееанм аатеитнв-тех ниче на@

ОЙЙ АНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<>767674

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. саид-ву (22) Заявлено 3105.78 (2t) 2620342/18-21 (51)M Kh 3

G R 31/28 с присоединением заявки №

Государственный комитет

СССР ио делам изобветеиий и открытий (23) Приоритет

Опубликовано 3009.80.Бюллетень ¹ 36 (53) УДК 681. 326. . 7 (088.8) Дата опубликования описания 30.0980

A.Â. Горохов, Е. И ..Николаев, Е.3. Храпко и С.В. Нюхалов (72) Авторы изобретения (71) Заявитель (54) УСТРОИСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ

ИНТЕГРАЛЬНЫХ СХЕМ

Изобретение относится к электроизмерительной технике и может использоваться в устройствах контроля и диагностики неисправностей элементов радиоэлектронной аппаратуры.

Известны устройства, содержащие эталонную интегральную схему, многоконтактный зонд, элементы сравнения, элементы свертки, индикаторы несравнения, блок запуска, блок индикации запуска и блоки установки (1). . Однако такие устройства не выдают информацию о том, произошли ли в процессе контроля переключения на входах и выходах эталонной интеграль-15 ной схемы.

Наиболее близким по технической сущности к предлагаемому является устройство для автоматического контроля интегральных схем, содержащее 20 многоконтактный зонд, эталонную интегральную схему, блоки сравнения, элемент И, триггер, кнопку сброса и индикатор наличия неисправности(2).

Недостаток этого устройства . также низкая достоверность контроля.

Цель изобретения - повышение достоверности контроля. 30

Это достигается тем, что в устройство, содержащее многоконтактный зонд, соответствующие входные контакты которого соединены с входами эталонной интегральной схемы, а его соответствующие выходные контакты соединены с входами контролируемой интег- ральной схемы, выходы которой соединены с другими выходными контактами многоконтактного зонда, входные контакты которого соединены соответственно с первыми входами блоков сравнения, вторые входы которых соединены с соответствующими выходами эталонной интегральной схемы, первый элемент И, входы которого соединены соответственно с выходами блоков сравнения, триггер, один вход которого соединен с выходом первого элемен-. та И, другой его вход соединен с кнопкой сброса, индикатор наличия неис-. правности, вход которого соединен с выходом триггера, введены блоки анализа и запоминания переключений, второй элемент И и индикатор переключений, причем сигнальные входы соответствующих блоков анализа и запоминания переключений соединены соответственно с выходами эталонной интегральной схемы, с входами которой сое767674 динены сигнальные входы соответствующих блоков анализа и запоминания пе- реключений, выходы блоков анализа и запоминания перключений соединены с входами второго элемента И, выход которого соединен с входом индикатора переключений, а управляющие входы каждого из блоков анализа и запоминания переключений соединены с кнопкой сброса.

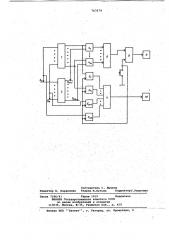

На чертеже приведена структурйая схема предлагаемого устройства.

Устройство содержит эталонную интегральную схему 1, кнопку сброса

2, контакты 3 -3и,. ЗИ q — 3@ многоконтактного зонда, блоки 4 — 4 и сравнения, блоки 51 — 5и, 5 и+1 — 5 ди анализа и запоминания переключений, элементы И 6, 7, триггер 8, индикатор 9 наличия неисправности и индикатор 10 переключений.

Устройство работает следующим образом, Эталонная интегральная схема 1 своими входами через контакты ЗА

Зи многоконтактного зонда подключена, к входам контролируемой интегральной схеМы. Идентичные выходы эталонной интегральной схемы l.и контролируемой интегральной схемы подклю-. чены к блокам сравнения 4 q — 4 и. К входам и выходам эталонной интегральной схемы 1 подключены блоки 5 — 52и анализа и запоминания переключений.

Блок и 5 q — 5 g g выдают си гн ал ло ги,ческой 1 при изменении входного сигнала из 0 в 1 или наоборот.

По мере прохождения цикла проверки контролируемой интегральной схемы блоки 5 — 5 и фиксируют наличие изменяющихся сигналов на входах и выходах эталонной интегральной схемы 1.

После того,как перекл.учения произошли на всех выводах эталонной интегральной схемы 1, элемент И 7 выдает сигнал на индикатор 10 переключений.

При наличии идентичных сигналов на выходах"контролируемой интегральной схемы и эталонной интегральной схемы 1 сигналы в виде логических 1 поступают с выходов блоков

4 — 4 и сравнения на входы элемента

И 6. Выходной сигнал элемента И 6 подтверждает предварительно установленное исходное состояние триггера

8. Установка в исходное состояние блоков 5q — 5 и анализа и запоминания переключений триггера 8:производится кратковременным замыканием кнбпки сброса 2. В случае рассогласования сигналов хотя бы по одному из выходов контролируемой интегральной схемы и эталонной интегральной схемы 1 соответствующий из блоков

4 - 4и сравнения вырабатывает логический 0, который через элемент

И 6 переключает триггер 8. При этом срабатывает индикатор 9 налиЧия не4 исправности. При отсутствии переклю чений на одном из логических выводов эталонной интегральной схемы 1 соответствующих из блоков 5 — 5 „сохраня- ли ет на выходе логический "0".В этом случае индикатор 10 переключений не горит.

Таким образом, устройство обеспечивает более высокую достоверность контроля, логически исключая возможность принятия контролируемой интегральной схемы за годную, если не на всех ее входах и выходах произошли переключения логических уровней.

1Î!

Формула изобретения

Устройство для автоматического контроля интегральных схем, содержащее многоконтактный зонд, соответствующие входные контакты которого соединены с входами эталонной интеграль20 ляющие входы каждого .из блоков анализа и запоминания переключений соединены с кнопкой сброса.

Источники информации, принятые во внимание при экспертизе

1. Приборы и системы управления -, 1977, 9 10, с. 51, рис 5 (аналог) .

2. Авторское свидетельство СССР

Р 483633, кл. 6 01 R 31/28, 1975 (прототип) .

60 ной схемы, а его соответствующие выходные контакты соединены с входа ми контролируемой интегральной схемы, выходы которой соединены с другими выходными контактами многоконтактного зонда, входные контакты которого соединены соответственно с первыми входами блоков сравнения, вторые входы которых соединены с соответствующими выходами эталонной интегральной схемы, первый элемент И, входы которого соединены соответственно с выходами блоков сравнения, триггер, один вход которого соединен с выходом первого элемента И. другой его вход соединен с кнопкой сброса, индикатор наличия неисправности, вход которого соединен с выходом триггера, отличающееся тем, 4Q что, с целью повышения достоверности контроля, в него введены блоки анализа и запоминания переключений, второй элемент И и индикатор переключений, причем сигнальные входы

45 собтветствующих блоков анализа и запоминания переключений соединены соответственно с выходами эталонной интегральной схемы, с входами которой соединены сигнальные входы соответствующих блоков анализа и запоминания переключений, выходы блоков анализа и запоминания переключений соединены с входами второго элемента И, выход которого соединен с входом индикатора переключений, а управ767674

Составитель С. Бычков

Редактор Е. Караулова Техред:М. Кузьма Корректор Г. Решетник

Заказ 7186/41 Тираж 1019 Подписное

ВНИИПИ Государственного комитета СССР по делаМ изобретений и открытий .

113035, Москва, Ж-35, Рауаская наЬ., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4