Цифровой многомерный регулятор

Иллюстрации

Показать всеРеферат

О и И,С.;ж,ij. ИЗОБРЕТЕНИЯ

«»767703

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 241178 (21) 2687306/18-24

{51) М. Кл. с присоединением заявки ¹ (23) Приоритет

G 05 В 11/32

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 3009.80. Бюллетень Мо 36

Дата опубликования описания 300980

{53) УДК 62-50 (088.8) (72) Авторы изобретения

С.К. Дауров., С.В. Ефимов, В.И. Кнышев и Н.Н. Колесов

Саратовский политехнический институт (71) Заявитель (54) ЦИФРОВОЙ МНОГОМЕРНЫЙ РЕГУЛЯТОР

Изобретение относится к области автоматического управления сложными объектами и может быть использовано для автоматического регулирования ле- 5 тательных аппаратов.

Известен многоканальный регулятор, содержащий коммутатор, преобразователь аналог-код и устройство управления,осуществляющее регулирование большого числа параметров (1 .

К недостаткам известного устройства относятся невозможность регулирования по сложным законам, а также невысокая точность. 15

Наиболее близким к изобретению техническим решением является управляющий процесс, содержащий первый преобразователь код-напряжение, цифровой вход которого через цифровой 20 запоминающий блок соединен с первым выходом устройства управления, вторым выходом подключенного к управляющему входу коммутатора, первые входы которого соединены с соответствующи- 25 ми выходами объекта регулирования, остальные вторые входы — с соответствующими выходами регулятора, а выход — с аналоговым входом преобразователя код-напряжение 121. 30

Основной недостаток известного устройства заключается в его низкой точности при усложнении алгоритмов управления.

Цель изобретения — повышение точности регулятора.

Указанная цель достигается тем, что в него введены преобразователь напряжение-код и по числу вторых входов коммутатора каналы регулирования, каждый из которых состит из последовательно соединенных комбинационного сумматора, запоминающего устройства и второго преобразователя коднапряжение, выход которого подключен к соответствующему выходу регулятора. первые входы комбинационных суммато.ров соединены с выходом преобразователя напряжение-код, вход которого . подключен к выходу первого преобразователя код-напряжение,.а вторые входы — co вторыми выходами соответствующих запоминающих устройств. Управляющие входы комбинационных сумматоров, запоминающих устройств и второго преобразователя код-напряжение подключены к соответствующим выходам устройства управления.

767703 где )jan„ i — M T HU p H Bo3- 20 действий; (<) 6) и),Ж ,„1 и " 1 1

25 — матрица чисел размером

МК(М ) с

Ю М „Ю.,И)

И1 " Мй his HH

Y1(44) в«М -"т

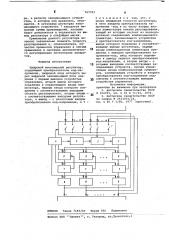

Блок=схема регулятора приведена на чертеже.

Он содержит коммутатор 1 входных

Сигналов, первый преобразователь 2 код-напряжение, цифровой запоминающий блок 3, устройство 4 управления, преобразователь 5 напряжение-код и в каждом канале комбинационный сумматор 6, запоминающее устройство 7, второй преобразователь 8 код-напря-, жение.

Работа регулятора происходит следующим образом.

Синхрбнизация работы осуществляется устройством управления, связанным . со всеми блоками регулятора.

Закон регулирования описывается следующим уравнением:

1 поминающего блока 3. В результате работы преобразователя на его выходе формируется величина, равная произведению входной переменной и постоянной из цифрового запоминающего блока.

Полученная аналоговая величина переводится первым преобразователем 5 напряжение-код в цифровую, и далее процесс вычисления производится в цифровой форме. С выхода преобразователя 5 напряжение-код произведение засылается, например, н первый комбинационный сумматор 6, где складывается с содержимым последнего регистра запоминающего устройства, состоящего.из (+ 1) регистров, и засыла- ется и первый регистр этого же запоминающего устройства. Затем содержимое всех регистров запоминающего устройства сдвигается на один регистр вниз. Следующее произведение из той же входной переменной и следующей постоянной из цифрового запоминающего блока 3 складывается но втором комбинационном сумматоре с содержимым последнего (+ + 1)-ro регистра второго запоминающего устройства и засылается в перный регистр этого же запоминающего устройства. Затем содержимое всех регистров запоминающего устройства сдвигается на один регистр вниз. М-е произведение этой же входной величины подается на вход

М) — матрица входных координат цифрового многомерного регулятора," Р -1,i;i=j число предыдущих значений управляющих воздействий, исполЬзуемых для вычйслеййя- управления на текущем шаге; 45

К - номер шага; и --число выходных координат цифрового многомерного регулятора;. и -"число входйых координат «р цифрового многомерного регулятора. и переменных llYll с выхода объекга управления и М переменных llU(l с выхода- цифровогб"- йногомерйбТо регулятора подаются на первые и вторые соответственно входы коммутатора 1 входных сигналов, образуя множество вход нйх переменных цифройого "многомерного регулятора. Кояй татор" входйьЖ сигналов последонательно подключает 60 переменные на аналоговый вход"первoro преобразователя 2 кода-напряжение. На цифровой вход преобразователя код="" йапряжение,подаются постоянные числа матрицы (Ф, Рш)ц иэ цифроного за- 65

M-го сумматора, à (M + 1)-е произведение — опять на вход первого сумматора и т.д. . Таким образом, при действии первой переменной на входе первого преобразователя 2 код-напряжение он формирует M ° 4) произведений с М 1 постоянными иэ цифрового запоминающего блока 3 и через преобразователь 5 напряжение-код и комбинационные сумматоры 6 складывает их с содержимым

Ф регистров каждого из М сдвигов запоминающего устройства. На этом завершается малый вычислительный цикл.

Следующий малый вычислительный цикл начинается с появлением второй переменной на выходе -коммутатора входных сигналов. После того как произведения последней (М + й)-й входной велйчины на соответствующие постоянные иэ цифрового запоминающего блока.3 будут в соответствующих сумматорах 6 сложены с содержимым (Р + 1)-х ре гистров запоминающих устройств 7 и записаны в первые регистры этих устройств, закончится большой вычислительный цикл, т.е. закончится время одного из шагов. В этот момент времени в одном иэ регистров каждого сдвигоного запоминающего устройства, находится величина, равная-управляющему ноздейстнию данного канала на следующем (k + 1)-м шаге. Эта величина поступает на второй преобразователь 8 код=йапряжение и далее на выход цифрового многомерного регулято76770 3

Формула изобретения

ВНИИПИ Заказ. 7193/43 Тираж 956 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ра, а регистр запоминающего устройства, в котором она .хранилась, обнуляется. В остальных регистрах запоминающего устройства 7 находятся неполные суммы произведений, которые будут дополняться и подаваться на выход регулятора в следувщих шагах.

Применение данного регулятора позволит значительно повысить точность регулирования и, следовательно, качество процессов управления в случае применения в системах автоматического регулирования летательных аппаратов.

Цифровой многомерный регулятор, содержащий преобразователь код-на-пряжение, цифровой вход которого через цифровой запоминающий блок соединен с первым выходом устройства управления, второй выход которого подключен к управляющему входу коммутатора, первые входы которого соединены с соответствующими выходами объекта регулирования, вторые входы— с соответствующими выходами регулятора, а выход — с аналоговым входом преобразователя код-напряжение, о тл и ч а ю шийся тем, что, с целью повышения точности регулятора, в него введены преобразователь напряжение -код и по числу вторых входов коммутатора каналы регулирования, каждый из которых состоит из последовательно соединенных комбинационного сумматора, запоминающего устройства и преобразователя код -напряжение, .выход которого подключен к соответст--"вующему выходу регулятора, первые О входы комбинационных сумматоров соединены с выходом преобразователя Напряжение-код, вход которого подключен к выходу первого преобразователя код-напряжение, а вторые входы — с

3$ вторыми выходами соответствующих запоминающих устройств, причем управляющие входы комбинационных сумматоров, запоминающих устройств и второго преобразователя код-напряжение поцщ ключены к соответствующим выходам устройства управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 354761, кл. G 05 В 11/14, 1970.

2. Авторское свидетельство СССР по заявке 9 2523054/24, : кл. G 06 F 1/00, 1977 (прототип).