Генератор псевдослучайных кодов

Иллюстрации

Показать всеРеферат

н тт тюк и Феъ еек@я

t «« ; fi «1 ««т r-, -I в„т а

ОП ИСАЙ ИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик 767743

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.07.78 (21) 2639066/18-24 с присоединением заявки № —. (23) Приоритет— (51) М.К . .. G 06 F 1/02

G 07 C 15/00

Государственный комитет

СССР (53) УДК 681.325 (088.8) Опубликовано 30.09.80. Бюллетень № 36

Дата опубликования описания 05.10.80 ло делам изобретений и открытий

В. П. Сидоренко, А. М. Романкевич, О. Д. Руккас, Е. Н. Чичирин и М. С. Берштейн (72) Авторы изобретения

Киевский научно-исследовательский и конструкторский институт периферийного оборудования (71) Заявитель (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ КОДОВ

Изобретение относится к области вычислительной техники и предназначено для использования в системах контроля и диагностики электронных цифровых блоков

ЭВМ.

Известен генератор псевдослучайной последовательности кодов, применямый для формирования и подачи входных воздействий на проверяемый цифровой блок и обеспечивающий совместно со счетчиком выходных реакций блока большую, чем существующие тестовые методы, полноту контроля при существенно меньшей трудоемкости подготовки исходной программы проверки.

Этот генератор содержит сдвиговый регистр с цепями обратной связи и обеспечивает формирование псевдослучайных двоичных последовательностей с вероятностью получения в них единичного сигнала, равной

0,5. Однако применение генератора в целях контроля ограничено в основном комбинационными схемами. Реальные же цифровые блоки для обеспечения корректного своего проведения требуют строго определенных временных соотношений между сигналами на информационных входах и входах синхронизации различных многоуровневых ре-!

2 гистровых и пересчетных схем, охваченных общими обратными связями, а также вре.менного разнесения сигналов в других цепях, подверженных различного рода критическим ситуациям, например, RS-ситуациям, заключающимся в неопределенности конечного состояния триггера при одновременном снятии сигналов установки с его R- u Sвходов. С другой стороны, для уменьшения времени контроля всех внутренних состояний таких блоков необходима возможность из10 менения вероятностей сигналов на выходах генератора. Так для контроля старших разрядов счетчика необходимо, чтобы вероятность его сброса была задана меньшей, чем вероятность сигнала на его счетном входе (1).

Указанные задачи в настоящее время решаются путем выборочной коммутации выходов нескольких специализированных генераторов псевдослучайных кодов, кодов

Грея, генераторов синхронизирующих импульсов и т. п. на входы контролируемого р0 блока при помощи механического или электронного коммутатора, либо применяются специальные переходные вставки для каждого типа блоков. Однако все эти решения требуют больших затрат вследствие того, 767743 что номенклатура выпускаемых цифровых блоков и число их внешних контактов достигают нескольких сотен, и для разных типов блоков отсутствует повторяемость в соответствии номеров внешних контактов типа заведенных на них внутренних цепей блока (2) .

Известен также генератор псевдослучайных последовательностей импульсов с перестраиваемой вероятностью появления единицы на каждом из его выходов. Этот генератор является прототипом предлагаемого генератора испытательных кодов и содержит основной регистр с цепью обратной связи и регистр маски (3).

Однако за счет маскирования, т. е. блокировки состояния любого из разрядов основного регистра, в данном генераторе воз..-, можно получение дополнительно лишь нулевого и единичного значений вероятностей появления единицы на его выходах. При этом для сохранения числа активных триг. геров основного регистра необходимы эле.менты И или ИЛИ для обхода блокируемых триггеров и подключения к нему такого же числа триггеров дополнительного регистра.

Кроме того, в таком генераторе невозможно получение сихронизирующих и других, так называемых, псевдоциклических импульсов с гарантированным взаимным разнесением их фронтов, что крайне необходимо для достоверного контроля цифровых блоков.

Целью изобретения является расширение функциональных возможностей генератора за счет изменения вероятностных и времен.=-;.-::: —.*ных параметров генерируемых им кодов.

Для достижения поставленной цели в известный генератор псевдослучайных кодов, содержащий регистр маски, регистр с обратной связью, введены блок синхронизации, блок памяти, преобразующий регистр и выходной регистр, выходы которого явля ются выходами генератора, первая группа вхбдов выходного регистра соединена с выходами регистра маски соответственно, а вторая группа входов выходного регистра объединена со входами регистра маски и подключена к группе выходов блока памяти соответственно и соединена с первой группой входов преобразующего регистра соответственно, вторая группа входов которого соединена с выходами регистра с обратной связью соответственно, выходы преобразующего регистра соединены со входами блока памя.ти соответственно, синхронизирующие входы всех регистров и блока памяти соединены с выходами блока синхронизации соответственно.

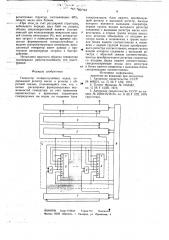

- На чертеже приведена структурная схема предлагаемого генератора кодов.

Генератор содержит выходной регистр 1, имеющий с целью совмещения во времени процессов выдачи синхроимпульсов и формирования очередного псевдослучайного код» входы поразрядного разрешения записи, 4s

so дом -ом его разряде и фазы получения его маски, определяющей те разряды выходного регистра 1, по которым в данном цикле произойдет запись полученного псевдослучайного кода. Фазы выполняются соответственно за а и m рабочих тактов генератора.

В каждом такте происходит формирование очередного значения всех п.двоичных последовательностей путем последовательного— в первой фазе и выборочного — во второй фазе порядка обращения к ъ -разрядным ячейкам блока памяти 3 и формирование очередного псевдослучайного разрядного кода в регистре 7, для чего на его шину синхронизации подается положительный импульс. Кроме того, в тактах первой фазы такие же импульсы подаются на шины синсоединенные с соответствующими выходами регистра маски 2, блок памяти 3 для формирования опорных циклических последовательностей, преобразующий регистр 4, состоящий из элементов ИЛИ 5 и 1К-триггеров 6, для преобразования равномерного распределения псевдослучайных кодов, формируемых в регистре 7 с обратной связью, и блок синхронизации 8.

Разрядность всех регистров и блока памяти 3 определяется необходимым числом одновременно генерируемых двоичных разрядов и обозначается через и.. Выходы блока памяти 3 соединены с соответствующими входами выходного регистра и регистра маски 2, а информационные входы — соответственно с выходами 1К-триггеров 6 преобразующего регистра 4, у каждого из которых одна пара 1- и К-входов соединена с выходом блока памяти 3, другая — через элемент ИЛИ 5 — с выходом регистра 7, а шины управления по третьим 1- и К-входам

pg 1К-триггеров и по вторым входам элементов

ИЛИ 5, а также шины начальной установки преобразующего 4 и 7 регистров, шины синхронизации всех четырех регистров и шины управления блока памяти 3 соединены с выходами блока синхронизации 8.

В исходном состоянии преобразующий регистр 4 сброшен в нулевое состояние. При единичном уровне на шине управления элементов ИЛИ 5 и блокировки выборки блока памяти 3 из блока 8, на выходах элементов

ИЛИ 5 и блока памяти 3 поддерживается единичный уровень. При этом через шины управления третьих 1-входов 1К-триггеров 6 по отрицательным фронтам на шинах их синхронизации в регистр 4 последовательно заносятся и затем переписываются в блок памяти 3 коды, необходимые для последующего формирования основной циклической последовательности.

После пуска процесс генерации каждого очередного л -разрядного испытательного, так называемого, псевдоциклического кода происходит за один цикл работы генератора, состоящего из двух основных фаз: фазы получения псевдослучайного кода с заданными вероятностями единиц и нулей в каж767743 хронизации преобразующего 4 и выходного

1 регистров, а также на шины управления

1-входов IК-триггеров 6, а на шинах управления элементов ИЛИ 5 и К-входов IKтриггеров 6 поддерживается нулевой уровень

При этом в каждом, предварительно сброшенном в начале фазы по шине начальной установки, 1-ом IК-триггере 6 накапливается дизъюнкция логических произведений, поступающих в каждом такте на его I -входы очередных значений ь-ой последовательности и ь -ой псевдослучайной последовательности, / снимаемой с выхода ь-го элемента ИЛИ 5.

Вероятность сохранения нулевого состояния в -ом IК-триггере 6 при этом будет равна

Р", где P = 0,5 — вероятность появления нуля в 1-ой псевдослучайной последовательности, К < количество единиц в -ой последовательности.

Для получения значений вероятностей, равных (1 — P"), требуется дополнительный (S + 1) -ый такт сложения по модулю 2 содержимого IK-триггеров 6 с единичными значениями соответствующих последовательностей. Положительный импульс в этом случае выдается также на шины управления элементов ИЛИ 5 и К-входов IK-триггеров 6.

Одновременно с этим, в течение первой фазы происходит запись последовательных значений последовательности в те разряды выходного регистра, на входы поразрядного разрешения записи которых с соответствующих выходов регистра маски 2 подается нулевой уровень. Это дает возможность между тактами выдачи псевдоциклических испытательных кодов подавать на проверяемый цифровой блок различные S-тактные синхроимпульсы. Для этого в регистр маски

2 из блока памяти 3 перед выполнением первой фазы необходимо занести соответствующую маску синхроимпульсов.

В начале второй фазы полученный псевдослучайный код запоминается в свободной ячейке блока памяти 3, регистр 4 сбрасывается и затем выполняется tn.тактов для формирования -разрядной маски этого кода. При этом циклы, в которых разрешается перепись полученного кода в i-ый разряд выходного регистра 1, могут быть заданы повторяющимися с периодом ", с номерами отсчета относительно начального цикла каждого периода, равными одному или нескольким tn.-разрядным -ным числам, где основание системы счисления и обычно <

<ц.Для этого область памяти соответствующих значений всех ОЦП разбита соответственно на а зон по г к-разрядных, перенумерованных от нуля до (t — 1) ячеек в каждой зоне, и каждое такое число кодируется нулями в i-ом разряде тех тячеек, номера которых равны соответствующим цифрам этого числа. Оставшиеся после кодирования всех чисел ячейки заполняются единицами.

Общее количество закодированных таким

SS

С другой стороны, сочетание детерминированных и статистических характеристик испытательных кодов обеспечит более полный и достоверный контроль по сравнению с другими генераторами и тестовыми методами. Например, анализ только одного процессора ЭВМ М-400 показал, что при помощи предлагаемого генератора можно проконтролировать все 100О/О его цифровых блоков, в то время как прототип обеспечивает контроль лишь блоков без глобальных обратных связей и многоуровневых образом номеров отсчета для каждого -го разряда равно произведению числа единиц по этому разряду в каждой из зон блока памяти 3, а наличие нулей или наоборот единиц одновременно во всех ячейках ь-го разряда разрешает или соответственно запрещает запись нового псевдослучайного кода в ь-ый разряд выходного регистра 1 во всех циклах.

Формирование очередного значения всех последовательностей происходит путем чтения в каждом такте второй фазы содержимого одной из ячеек каждой зоны, причем номера выбираемых д ячеек равны значениям соответствующих разрядов некоторой гаразрядной -ной переменной, периодически

15 принимающей в каждом очередном цикле последовательные от нуля до (г — 1) значения.

Одновременно с этим, в каждом такте на шины управления элементов ИЛИ 5 и 1входов IК-триггеров 6, а также на шины синхронизации регистра 4 поступают положительные импульсы. Образующийся при этом в регистре 4 код маски представляет собой поразрядную дизъюнкцию м.значений последовательностей и содержит нули в тех разрядах, для которых значение rn разрядной переменной в данном цикле совпало с кодом одного из закодированных в соответствующих разрядах блока памяти 3 чисел. В конце второй фазы код маски заносится через блок памяти 3 в регистр маски 2 и управляет записью в выходной регистр 1 полученного в конце первой фазы и хранящегося в блоке памяти 3 псевдослучайного кода.

В результате многократного циклическо го повторения описанного процесса в каждом цикле генератора на любых его выходах возможно формирование необходимых многоактивных последовательностей синхроимпульсов или псевдоциклических двоичных последовательностей с регулируемыми вероятностями единиц и нулей и заданными моментами возможного изменения логичес40 ких уровней в каждой из них.

При использовании данного генератора в системах контроля удается исключить влияние некорректных входных воздействий на проверяемый цифровой блок, в том числе задать необходимый детерминированный режим работы функционально наиболее важных его цепей, таких как цепи синхронизации, сдвига, начальной установки и т. и

«Ъ « . ° », »„„4

М7743

Формула изобретения!

ВНИИПИ Заказ 7l95//44 Тираж 75! Подписное

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 регистровых структур, составляющих 68 /о общего числа всех блоков.

"==:-:--- --;При этом,за счет регулярной структуры, небольшого йорядка двух байт на разряд, объема сверхоперативной памяти (составляющей при использовании микросхем средней степени интеграции 5о/о всех аппаратурных затрат) и совмещения во времени процессов формирования псевдослучайных и выдачи синхронизирующих импульсов, предлагаемый генератор имеет равные с прототипом аппаратурные затраты и быстродействие.

Испытания опытного образца генератора подтвердили работоспособность его конструкций:Генератор псевдослучайных кодов, содержащий регистр маски и регистр с обратной связью, отличающийся тем, что, с целью расширения функциональных возможностей генератора за счет изменения вероятностных и временных параметров генерируемых им кодов, он содержит блок синхронизации, блок памяти, преобразующий регистр и выходной регистр, выходы которого являются выходами генератора, первая группа входов выходного регистра соединена с выходами регистра маски соответственно, а вторая группа входов выходного регистра объединена со входами регистра маски и подключена к группе выходов блока памяти соответственно и соединена с первой группой входов преобразующего регистра соответственно, вторая группа входов которого соединена с выходами регистра с обратной связью соответственно, выходы преобразующего регистра соединены со входами блока памяти соответственно, с инхронизирующие входы всех регистров тз и блока памяти соединены с выходами блока синхронизации соответственно.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 468231, кл. G 06 F 1/02, 1973.

2. Патент Франции № 2163442, кл. G 06 F 15/00, 1973.

3. Авторское свидетельство СССР по заявке № 2340415/18-24, кл. G 06 F !/02, 1976 (прототип) .