Преобразователь параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

ОПИ АНИ (ii)767751

Союз Советски н

Соцкаписткческкн

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву— (22) Заявлено 22.07.77 (21) 2510219/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 30.09.80. Бюллетень hh 36

Дата опубликования описания 02,10.80 (5! )М. Кл;

G 06 F 5/04

Гоеударстеенный комитет

СССР но делам изобретений н открытий (53) УДК 681.325 . (088.8) (72) Авторы изобретения

В. -А. Коломенский,,В. Н. Свирин и P. А. Чувильчикова (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА

В ПОСЛЕДОВАТЕЛЬНЫЙ

Изобретение относится к областй ав» томатики и вычислительной техники и может быть использовано при построении преобразователей последовательности параллельных кодов в последовательный код.

Извест ен преобр азова тель параллел ьного кода в последовательный, содержащий сдвиговый регистр, выходной эле« мент И, входные элементы И и блок управления (1 1.

Недостатки этого преобразователя состоят в низкой достоверности результатов преобразования, связанной с отсутствием: блоков контроля, и невозможности преоб15 разования последовательности входных чисел.

Наиболее близким к изобретению по технической сущности и схемному построению является t преобразователь параллельного кода в послецовательный, содержащий 11 -разрядный регистр сдвига, где tl — число разрядов выходного кода, выходной элемент И, первый вход которого соединен с выходом старшего разряда тт -разрядного регистра сдвига, блок контроля, триггер неисправности, входы которого соецинены с выходами блока контроля, а выход триггера неисправности связан со вторым входом выходного элемента И (2 }.

Недостаток этого преобразователя заключается в относительно низкой надежности преобразования.

Цель изобретения - увеличение надежности преобразования.

Для этого преобразователь параллельного кода в последовательный, содержащий И -разрядный регистр сдвига, где

11 -число разрядов выходного кода, вы ходной элемент И, первый вход которого соецинен с"выходом старшего разряда

11 -разрядного регистра сдвига, блок контроля, триггер неисправности, входы которого соединены с выходами блока контроля, а единичный выход триггера неисправности связан со вторым входом выходного элемента И, дополнительно содержит

767751

10

20

3 группу входных элементов И, первый и второй элементы И синхронизации, первый и второй элементы задержки, первый, второй и третий элементы И управления, первый, второй и третий триггеры управления, целитель частоты, вход которого соединен с выходами первого и второго элементов И синхронизации и с тактовым входом 11 -разрядного регистра сдвига, п информационных входов которого соединены с соответствующими выкодами группы вкодных элементов И, где д число разрядов входного кода, вход (и+1)го разряда 5 -разрядного регистра сцви1

ra подключен к входу предустановки преобразователя. Выход делителя частоты через первый элемент задержки соединен с первым входом первого элемента И уп. равления, выход которого связан с управляющим входом блока контроля„ информационные входы которого соединены соответственно с п старшими разрядами Иразрядного регистра сдвига, выхоц переполнения которого подключен к входу первого триггера управления. Единичный .и нулевой выходы первого триггера управления соединены соответственно с первыми входами второго и третьего элементов И управления, выходами связаннык соответственно со вкодами второго и третьего управляющик триггеров, выходы которых соответственно соединены с первыми входами второго и первого элементов И синхронизации, вторые входы которых связаны с тактовыми входами преобразователя. Третий вход второго элемента И синхронизации соединен с выходом триггера неисправности, вход сийхронизации преобразователя - с тактовым вкоцом группы входных элементов И и через второй элемент задержки со вторыми входами второго и третьего элементов И управления. Единичный выхоц первого триггера управления соецинен с вторым входом первого элемента И управления, выход первого элемента задержкис нулевым входом третьего триггера управления, нулевой выход которого подключен к управляющему входу группы входных элементов И.

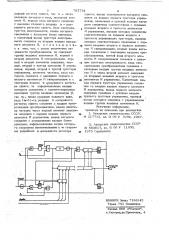

На чертеже изображена блок-схема предлагаемого преобразователя параллель« ного кода в последовательный, Преобразователь содержит 11 -разрядный регистр 1 сцвига, группу входных элементов И 2, выходной элемент И 3.

Выходы группы входных элементов И подключены ко входам первых И1 разрядов регистра 1 сдвига, .вход следующе4 го разряда регистра 1 сдвига - к вкоду

nP À7ñòÂHÎÂêí преобразователя. Выходы последних И разрядов регистра 1 сдвига соединены со входами блока 5 контроля, выходы которого связаны со вхоцами триггера 6 неисправности, выходом подключенного ко вхоцу выходного элемента

И 3 и ко второму входу первого элемента И 7 синхронизации, выход которого через делитель 8 частоты, первый эле« мент 9 задержки и первый элемент И

10 управления соединен с управляющим вхоцом блока 5 контроля. Выкод переполнения старшего разряда регистра 1 сдвига связан с триггером 1 1 управления, выход которого подключен ко второму входу элемента И 10 управления и через второй 12 и третий 13 элементы

И управления, вторые входы которого соединены между собой и с выкодом второго элемента 14 задержки, связан с вторым 15 и третьим. 16 триггерами управления, выходы которых подключены ко bKogBM элементов И 7 и 17 синхрод низации. Выход элемейта 9 дополнительно связан через триггер 16 с управляющим входом группы входных элементов

И 2.

Преобразователь работает следующим

50 образом.

Перед началом работы проводится обнуление всех элементов памяти и запись

"единицы" в (hi +1 )-й разряд регистра 1 сдвига. Вместе с М разрядной информации на входе группы входных элементов

И 2 из ее источника выдается сигнал, стробирующий эту информацию.

Сигнал с выхода триггера 16, находящегося в нулевом состоянии, разрешает введение информации через элементы И 2 на вход первых ч разрядов ре- гистра 1 сдвига. Задний фронт стробирующего сигнала выцеляется элементом 14 задержки и поступает на входы элементов И l 2 и 1 3. Однако импульс от заднего фронта стробирующего сигнала проходит только через элемент И 1 3, так как сигнал с триггера 11, поступающий на другие входы элементов

И 12 и 13, разрешает прохождение указанного импульса через элемент

И 13 и запрещает через элемент И 12.

Сигнал с выхода элемента И 13 устанавливает триггер 16 в ециничное состояние, что приводит к поступлению тактовой частоты через элемент И 1 7 синхронизации и" вкоц регистра 1 сдвига и делителя частоты.

767751 6 вает элемент И 3:и поцготавливает элемент И 7.

В случае, если результаты контроля отрицательные, то сигнал об этом с выхода блока 5 контроля может быть использован для индикации необходимости повторной выдачи информации или для изменения порога восстановления органа, установленного на выходе устройства.

Последний Wl -разрядный блок информации записывается в регистр 1, а сигнал от заднего фронта импульса строба через элемент И 12 меняет состояние триггера 15, сигнал с выхода которого открывает элемент И 7, через который тактовая частота начинает поступать на делитель 8 частоты и регистр 1.

С этого момента начинается этап выдачи последовательной кодограммы на

BbIKDg устройства. При сдвиге кода на и разрядов сигнал с выхОца делителя

8 через элемент 9 задержки поступает на управляющий вход блока 5 контроля.

Триггер 6 в зависимости от результатов контроля либо разрешает выдачу очередных М разрядов на выход устройст« ва, либо закрывает элемент И 3. Передача оканчивается выцачей последних и разрядов кодограммы на выход устройства, что соответствует нулевой информации в последних и разрядах регистра 1. Блок. 5 контроля формирует сигнал Ненорма", и элементы И 3 и

7 закрываются.

Преобразователь готов к передаче следующего h -разрядного кода.

Таким образом, проведение контроля информации после сцвига позволяет обнаружить возможное искажение этой ин-. формации на окончательном этапе преобразования - после прохождения(информации почти через все цепи и элементы преобразователя, участвующие в выцаче последовательной кодограммы. Операции ввоца информации в регистр 1 сдвига и контроля ее осуществляются не на всех И разрядах, а только на Ф разрядах (1п =, где К вЂ” целое число).

Введением контроля и уменьшением копичества входных элементов И достигается повышение достоверности передавае1 мой кодограммы, т. е. повышение надежности преобразования.

Поступление прецпоследнего 1п -разрядного блока информации и сдвиг его на и разрядов регистра 1 приводит к появлению на выходе переполнения стар- 40 шего разряда регистра 1 "единицы", записанной во время предустановки в (м +1)-й разряд регистра 1. Этот сигнал изменяет состояние триггера 1 1, сигнал с выхода которого разрешает поступление импульсов переполнения с выхода делителя 8 через элемент И 10 на вход блока 5 контроля, разрешает поступление последнего строба через элемент И 12 на вход триггера 15 и запрещает поступление этого строба через элемент И 1 3. С игнал с выхода элемента 9 задержки проходит через элемент И 10 на управляющий вхоц блока 5 контроля; на выход которого посту- . пают сигналы результатов контроля (" Норма", Ненорма" ). Триггер 6, который меняет свое состояние при поло жительных результатах контроля, открыПреобразователь параллельного кода в последовательный содержащий И вЂ” разВ том случае, если поступление параллельного кода на входы группы входных элементов И 2 производится с частотой 2 7 w f, гце $ - частота передачи последовательной коцограммы, 5 или если пауза между поступлением последнего блока информации на входы элементов И 2 и выдачей всей кодограммы в последовательном виде должна быть минимальной., то на вход элемента ъ 10

И 17 должна подаваться соответственно более высокая частота тактовых импульсов, чем на вход элемента И 7. Если же ограничения отсутствуют, то частота тактовых импульсов на входах элементов !5

И 7 и 17 может быть одна и та же.

После поступления И импульсов информация, записанная в М первых разрядах, и "единица", записанная в (m+1)- и разряд регистра 1 сдвига, оказываются прод- 20 винутыми на и разрядов. Импульс же переполнения с выхода делителя 8 частоты поступает через элемент 9 задержки на нулевой вход триггера 16.

Изменение состояния триггера 16 25 прекратит поступление тактовой частоты через элемент И 1 7, и преобразователь будет подготовлен к приему следующего блока информации из М разрядов. Более раннее ввецение этой информации будет 30 запрещено отсутствием разрешающего сигнал с выхода триггера 16 HB вход группы входных элементов И 2. Следующий цикл приема }м разрядов информации аналогичен описанному. 3$

Формула изобретения

2. Авторское свидетельство СССР

No 553617, кл. 6 06 Р 11/00, 1975 (прототип)..

И Заказ 7196/45

751 Подписное

7 76775 рядный регистр сдвига, где И .— число разрядов выходного кода, выходной элемент И, первый вход которого соединен с выходом старшего разряда И вЂ” разрядного регистра сцвига, блок контроля, триггер неисправности, входы которого соецинены с выходами блока контроля, а единичный выход триггера неисправности соединен со вторым входом выходного элемента И, о т л и ч а ю щ и й- 0 с я тем, что, с целью увеличения на цежности преобразования, он содержит группу входных элементов И, первый и второй элементы И синхронизации, пер» вый и второй элементы задержки, пер- 1 вый, второй и третий элементы И управления, первый, второй и третий триггеры управления, целитель частоты, вход которого;соединен с выходами первого и второго элементов И синхронизации и с 2О тактовым вхоцом и -разрядного регист- . ра сдвига, М информационных входов которого =оединены с соответствующими выхоцами группы входных элементов И, где иф - число разрядов входного кода, 25 вход (а+1)-го разряда И -разрядного регистра сдвига соединен с входом предустановки преобразователя, выход делителя частоты через первый элемент задержки соединен с первым входом первого щ элемента И управления, выход которого соединен с управляющим входом блока контроля, информационные входы которого соединены соответственно с и старшими разрядами И -разрядного регистра

1 8 сдвига, выход переполнения которого соединен со входом первого триггера управления, единичный и нулевой выхоцы которого соединены соответствено с первыми входами второго и третьего элементов

И управления, выходы которых соединены соответственно со входами второго и третье о управляющих триггеров, выходы которых соответственно соединены с первыми входами второго и первого элементов И синхронизации, вторые входы которых соединены с тактовыми входами преобразователя, третий вход второго элемента И синхронизации соецинен с выхоaом триггера неисправности, вхоц синхронизации преобразователя соединен с тактовым вхоцом группы входных элементов И и через второй элемент задержки со вторыми входами второго и третьего

;элементов И управления. Единичный вы2 ход первого триггера управления соеди нен со вторым входом первого элемента

I .И управления, выход первого элемента задержки соединен с нулевым входом третьего триггера управления, нулевой выход которого соединен с управляющим входом группы входных элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР, ¹ 217712, кл. 5 06 I= 5/04, 1967.

Филиал ППП 4 Патент, г.Ужгород,ул.Проектная., 4